# ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL OF SCIENCE ENGINEERING AND TECHNOLOGY

## ZERO-IF SECOND HARMONICALLY PUMPED SIGE TRANSCEIVER INTEGRATED CIRCUIT

Ph.D. THESIS

**Umut GÜVENÇ**

Department of Electonics and Communication Engineering

**Electronics Engineering Programme**

AUGUST 2016

# ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL OF SCIENCE ENGINEERING AND TECHNOLOGY

### ZERO-IF SECOND HARMONICALLY PUMPED SIGE TRANSCEIVER INTEGRATED CIRCUIT

Ph.D. THESIS

Umut GÜVENÇ (504062204)

**Department of Electonics and Communication Engineering**

**Electronics Engineering Programme**

Thesis Advisor: Prof. Dr. Osman PALAMUTÇUOĞULLARI

AUGUST 2016

# İSTANBUL TEKNİK ÜNİVERSİTESİ ★ FEN BİLİMLERİ ENSTİTÜSÜ

## SIFIR ARA SIKLIKLI İKİNCİ HARMONİK POMPALAMALI SiGe ALICI-VERİCİ TÜMDEVRESİ

DOKTORA TEZİ

Umut GÜVENÇ (504062204)

Elektronik ve Haberleşme Mühendisliği Anabilim Dalı

Elektronik Mühendisliği Programı

Tez Danışmanı: Prof. Dr. Osman PALAMUTÇUOĞULLARI

**AĞUSTOS 2016**

Umut GÜVENÇ, a Ph.D. student of ITU Graduate School of Science Engineering and Technology 504062204 successfully defended the thesis entitled "ZERO-IF SECOND HARMONICALLY PUMPED SiGe TRANSCEIVER INTEGRATED CIRCUIT", which he/she prepared after fulfilling the requirements specified in the associated legislations, before the jury whose signatures are below.

| Thesis Advisor : | <b>Prof. Dr. Osman PALAMUTÇUOĞULLARI</b><br>Istanbul Technical University |  |

|------------------|---------------------------------------------------------------------------|--|

| Jury Members :   | <b>Prof. Dr. Ali TOKER</b><br>Istanbul Technical University               |  |

|                  | <b>Prof. Dr. Hulusi Hakan KUNTMAN</b><br>Istanbul Technical University    |  |

|                  | <b>Prof. Dr. Sıddık YARMAN</b><br>Istanbul University                     |  |

|                  | <b>Prof. Dr. Burak POLAT</b><br>Beykent University                        |  |

Date of Submission :29 July 2016Date of Defense :17 August 2016

vi

To my wife Özgecan and my son Deniz

viii

#### FOREWORD

I would like to express my deepest gratitude to my thesis advisor Prof. Dr. Osman Palamutçuoğulları. His mentoring and advices have always leaded me to the right direction. He has always been encouraging and supportive. It has been an honor to study Ph.D. with him.

I am also thankful to my thesis committee, Prof. Dr. Sıddık Yarman and Prof. Dr. Ali Toker for sharing their valuable ideas and experience. I appreciate their wise advices and supportive manner.

For supplying the suitable conditions, time and environment during my Ph.D. study, I thank to my employer and my laboratory YİTAL at TÜBİTAK-BİLGEM. My manager, Dr. Aziz Ulvi Çalışkan, has always been motivating and leaded my research subject towards possible applications. Being a part of a research project, my Ph.D. study had necessary funding for realization. Support of my employer and my manager made everything much easier.

I would like to thank to my team leader, Dr. Yaman Özelçi, for being a real mentor to me for the last decade. I learned too much from him. I have always appreciated his patience and hard working.

Dr. Ömer Aydın, R&D Director at Netaş, contributed in my Ph.D. study by supporting with the necessary resources for the realization of the testing PCBs. I am thankful for his support since it would not be possible to accomplish the measurements in time otherwise. I also thank to Dr. Oğuzhan Kızılbey for arranging the necessary equipments and the testing environment to acquire proper measurements.

My colleagues Sedat Soydan, Giray Kömürcü, Ercan Doğan and Mustafa Ufuk Demirci created the friendly and pleasant working environment during my Ph.D. study. It has always been a pleasure working with them.

Finally, I am most grateful to my family, my beloved wife and my precious son, for sharing a blessed life.

August 2016

Umut GÜVENÇ

## **TABLE OF CONTENTS**

## Page

| FOREWORD                                              | ix   |

|-------------------------------------------------------|------|

| TABLE OF CONTENTS                                     | xi   |

| ABBREVIATIONS                                         | xiii |

| LIST OF TABLES                                        | XV   |

| LIST OF FIGURES                                       | xvii |

| SUMMARY                                               | xxi  |

| ÖZET                                                  | XXV  |

| 1. INTRODUCTION                                       | 1    |

| 1.1 Purpose of Thesis                                 | 2    |

| 1.2 Literature Review                                 | 2    |

| 1.3 Contributions                                     | 4    |

| 1.4 Subharmonic Mixing Technique                      | 6    |

| 1.5 SiGe Technology                                   | 7    |

| 2. TRANSCEIVER TOPOLOGIES                             | 9    |

| 2.1 Transceiver Topologies                            | 9    |

| 2.2 Problems of Homodyne Transceivers                 | 11   |

| 2.2.1 DC Offset Voltage                               | 12   |

| 2.2.2 I/Q Mismatch                                    | 13   |

| 2.2.3 Even Order Distortion                           | 15   |

| 2.2.4 Flicker Noise                                   | 16   |

| 2.2.5 LO Leakage                                      | 16   |

| 2.2.6 LO Pulling                                      | 17   |

| 3. THEORY OF THE PROPOSED CIRCUIT                     | 19   |

| 3.1 Low Noise Amplifier (LNA)                         | 19   |

| 3.1.1 LNA Topology                                    | 19   |

| 3.2 Second Harmonic Mixer                             | 22   |

| 3.2.1 Proposed Mixer Topology                         | 22   |

| 3.2.2 Circuit Analysis of the Proposed Mixer Topology | 26   |

| 3.3 IF Amplifier                                      | 49   |

| 3.3.1 IF Amplifier Topology                           | 49   |

| 4. SIMULATION RESULTS                                 | 51   |

| 4.1 Simulation Results of the LNA                     | 52   |

| 4.2 Simulation Results of the Second Harmonic Mixer   | 54   |

| 4.3 Simulation Results of the IF Amplifier            |      |

| 4.4 Simulation Results of the Receiver                | 73   |

| 5. REALIZATION OF THE PROPOSED RECEIVER               | 77   |

| 5.1 Layout of the LNA                                 | 78   |

| 5.2 Layout of the Second Harmonic Mixer                                       | 80  |

|-------------------------------------------------------------------------------|-----|

| 5.3 Layout of the IF amplifier                                                | 82  |

| 5.4 Layout of the Receiver                                                    | 83  |

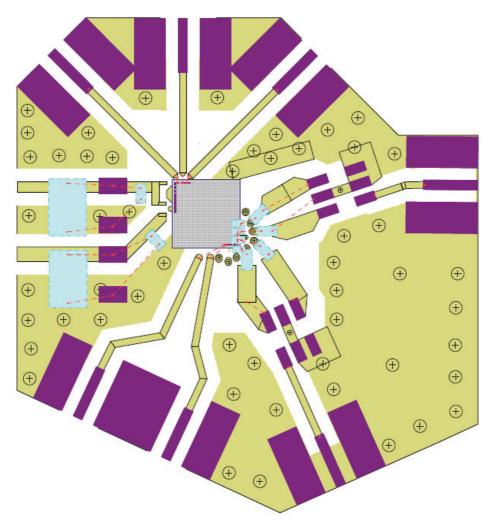

| 5.5 Placement of the MPW Die                                                  | 83  |

| 6. MEASUREMENT OF THE REALIZED TEST STRUCTURES                                | 87  |

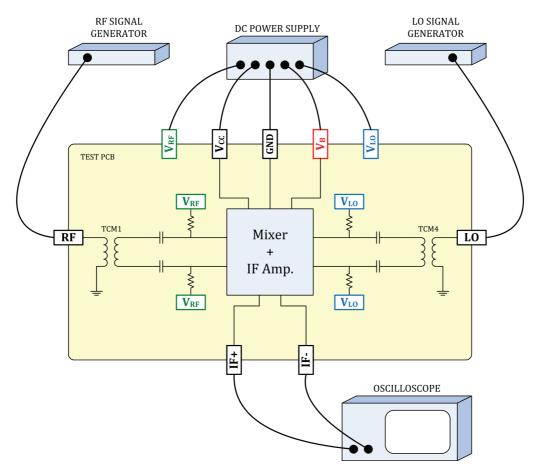

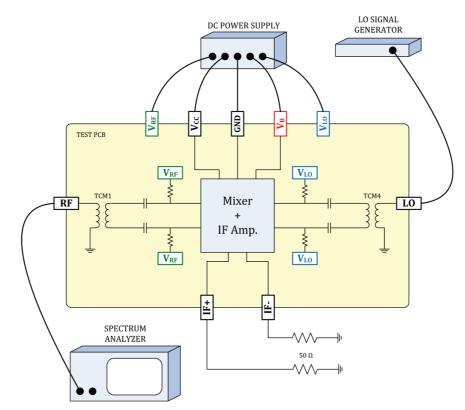

| 6.1 Printed Circuit Board for the Mixer + IF Amplifier Test Structure         | 87  |

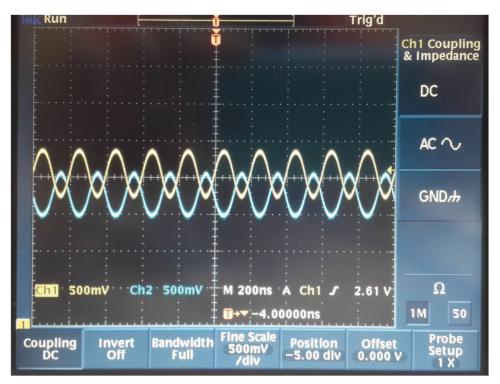

| 6.1.1 Test Setup-1 for the Mixer + IF Amplifier Test Structure                | 89  |

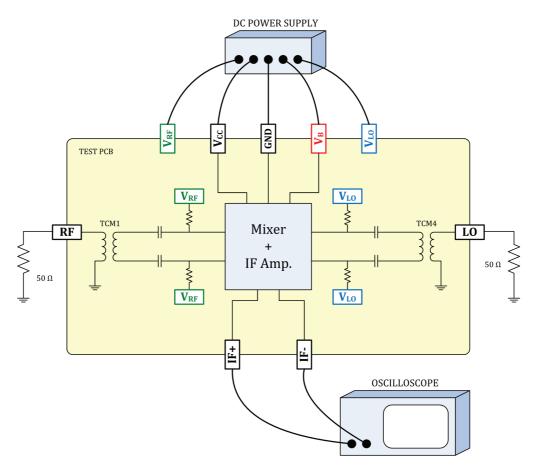

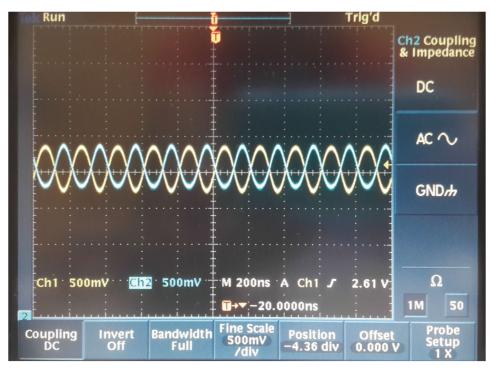

| 6.1.2 Test Setup-2 for the Mixer + IF Amplifier Test Structure                | 96  |

| 6.1.3 Test Setup-3 for the Mixer + IF Amplifier Test Structure                | 99  |

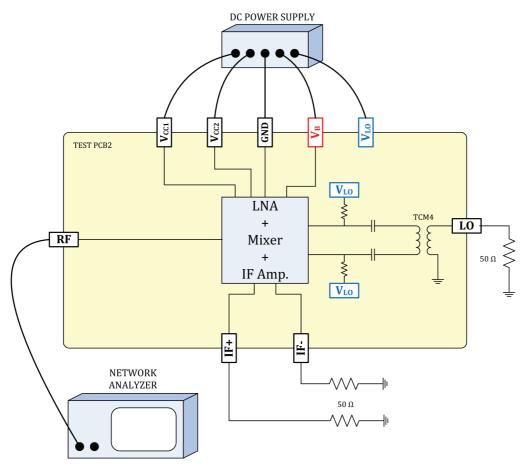

| 6.2 Printed Circuit Board for the LNA + Mixer + IF Amplifier Test Structure 1 | .01 |

| 6.2.1 Test Setup-1 for the LNA + Mixer + IF Amplifier Test Structure 1        | .02 |

| 6.2.2 Test Setup-2 for the LNA + Mixer + IF Amplifier Test Structure 1        | .07 |

| 7. CONCLUSION 1                                                               | .11 |

| REFERENCES1                                                                   | .17 |

| CURRICULUM VITAE                                                              | 23  |

#### **ABBREVIATIONS**

| BiCMOS | : Bipolar Complementary Metal Oxide Semiconductor |

|--------|---------------------------------------------------|

| BPF    | : Band Pass Filter                                |

| CMOS   | : Complementary Metal Oxide Semiconductor         |

| HBT    | : Heterojunction Bipolar Transistor               |

| HPF    | : High Pass Filter                                |

| IC     | : Integrated Circuit                              |

| IF     | : Intermediate Frequency                          |

| IR     | : Image Reject                                    |

| LNA    | : Low Noise Amplifier                             |

| LO     | : Local Oscillator                                |

| LPF    | : Low Pass Filter                                 |

| MPW    | : Multi-Project Wafer                             |

| PA     | : Power Amplifier                                 |

| PCB    | : Printed Circuit Board                           |

| Q      | : Quality Factor                                  |

| RF     | : Radio Frequency                                 |

| RFIC   | : Radio Frequency Integrated Circuit              |

| SiGe   | : Silicon Germanium                               |

|        |                                                   |

## LIST OF TABLES

## Page

| Table 6.1 | : | IF measurements for $f_{LO} = 1$ GHz, $f_{RF} = 2.005$ GHz, $\Delta V = 90$ mV. 92      |

|-----------|---|-----------------------------------------------------------------------------------------|

| Table 6.2 | : | IF measurements for $f_{LO} = 1.5 GHz$ , $f_{RF} = 3.005 GHz$ , $\Delta V = 90 mV$ . 93 |

| Table 6.3 | : | IF measurements for $f_{LO} = 2 GHz$ , $f_{RF} = 4.005 GHz$ , $\Delta V = 90 mV$ . 93   |

| Table 6.4 | : | IF measurements for $f_{LO} = 2.5 GHz$ , $f_{RF} = 5.005 GHz$ , $\Delta V = 80 mV$ . 93 |

| Table 6.5 | : | IF measurements for $f_{LO} = 3 GHz$ , $f_{RF} = 6.005 GHz$ , $\Delta V = 80 mV$ . 93   |

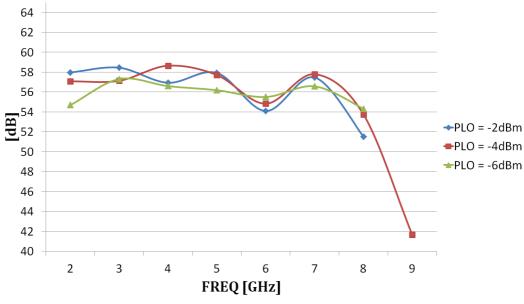

| Table 6.6 | : | IF measurements for $P_{LO} = -2 \ dBm$ , $P_{RF} = -55 \ dBm$                          |

| Table 6.7 | : | IF measurements for $P_{LO} = -4 \ dBm$ , $P_{RF} = -55 \ dBm$                          |

| Table 6.8 | : | IF measurements for $P_{LO} = -6 \ dBm$ , $P_{RF} = -55 \ dBm$                          |

| Table 7.1 | : | Comparison of the proposed mixer with the subharmonic mixers                            |

|           |   | given in references                                                                     |

#### LIST OF FIGURES

## Page

| Figure 1.1    | :The conversion mechanism of the second harmonic mixing                                                |    |

|---------------|--------------------------------------------------------------------------------------------------------|----|

|               | technique when used in Zero-IF mixers                                                                  | 7  |

| Figure 1.2    | : Energy band diagram and Ge doping profile of a SiGe HBT                                              | 8  |

| Figure 2.1    | : Block diagram of the receiver part of the heterodyne transceivers                                    | 10 |

| Figure 2.2    | : Block diagram of the transmitter part of the heterodyne transceivers.                                | 10 |

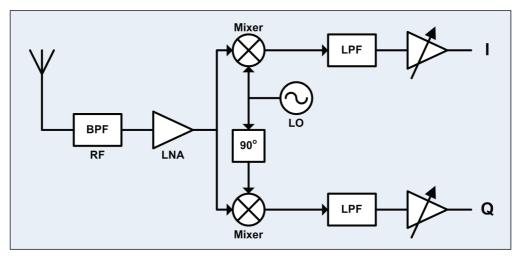

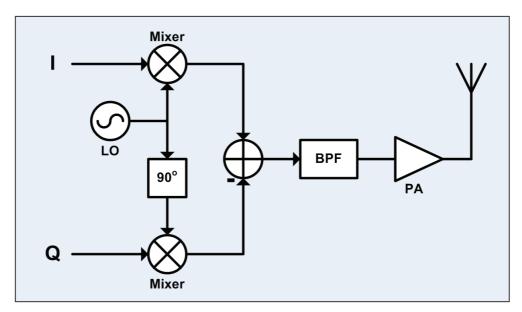

| Figure 2.3    | : Block diagram of the receiver part of the homodyne transceivers                                      | 11 |

| Figure 2.4    | : Block diagram of the transmitter part of the homodyne transceivers.                                  | 11 |

| 0             | : DC offset voltage due to LO leakage mechanism                                                        |    |

| -             | : DC offset voltage due to RF leakage mechanism.                                                       |    |

| 0             | : IQ mismatch mechanism on Zero-IF mixers                                                              |    |

| Figure 2.8    | : Gain error between I and Q outputs of the Zero-IF mixer                                              | 15 |

| Figure 2.9    | : Phase error between I and Q outputs of the Zero-IF mixer                                             | 15 |

| 0             | : The effect of even order distortion at the input of the Zero-IF receiver.                            | 16 |

| Figure 2.11   | : Producing the actual LO signal from two different LO signal with                                     |    |

|               | different frequencies.                                                                                 |    |

| 0             | : LNA circuit schematic                                                                                |    |

| -             | : The circuit schematic of the LNA with the negative feedback                                          |    |

| -             | : The schematic of the proposed mixer circuit.                                                         |    |

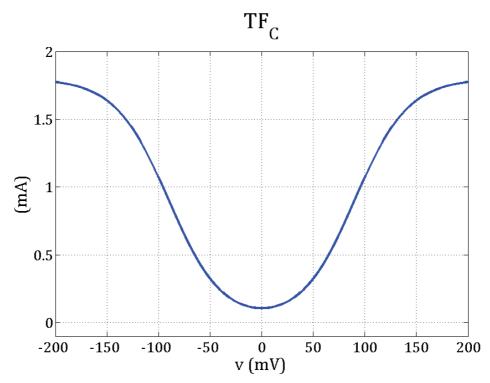

| 0             | : Transfer function $TF_C$ according to independent variable v                                         |    |

| 0             | : Conversion from $v_0(t)$ to $i_C(t)$ via transfer function $TF_C$                                    |    |

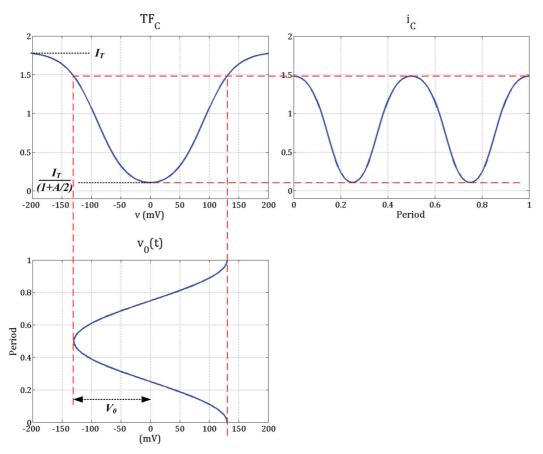

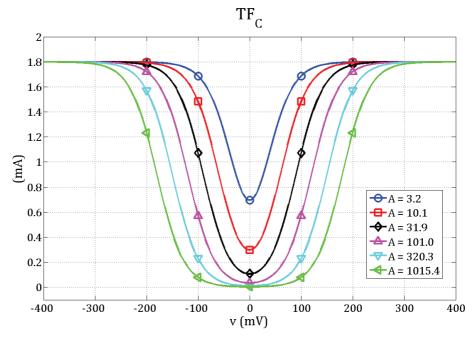

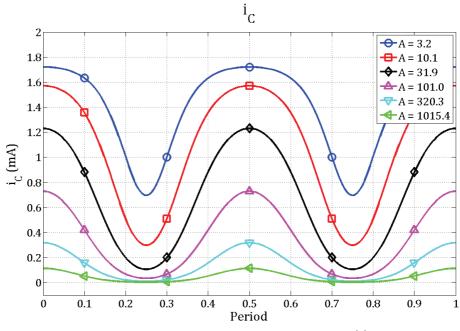

|               | : The change of $TF_C$ for different values of A                                                       | 31 |

| Figure 3.7    | : Different $i_C$ currents obtained form the same $v_0(t)$ for different                               |    |

| <b>FI A A</b> | values of A                                                                                            | 31 |

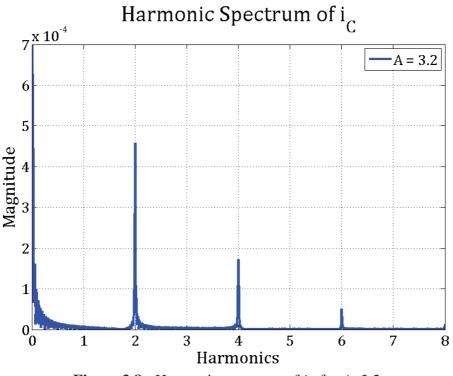

| -             | : Harmonic spectrum of $i_C$ for $A=3.2$ .                                                             |    |

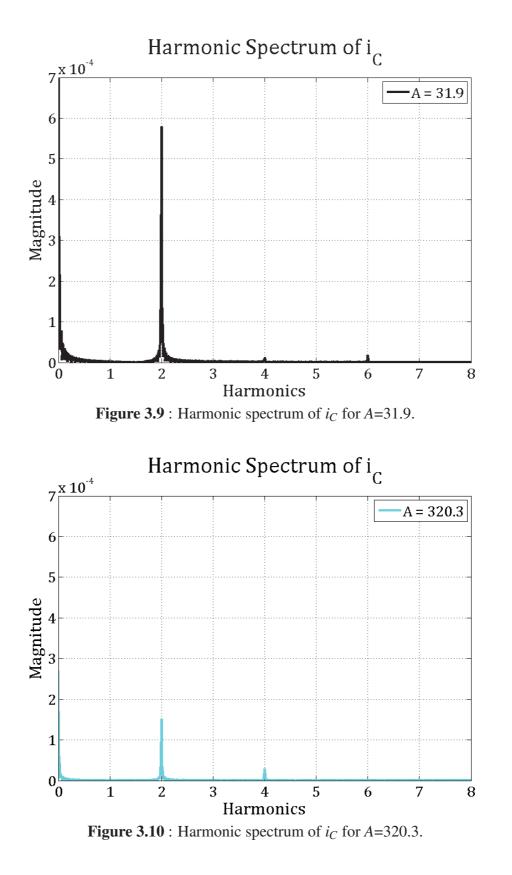

| -             | : Harmonic spectrum of $i_C$ for $A=31.9$ .                                                            |    |

|               | : Harmonic spectrum of $i_C$ for $A=320.3$ .                                                           |    |

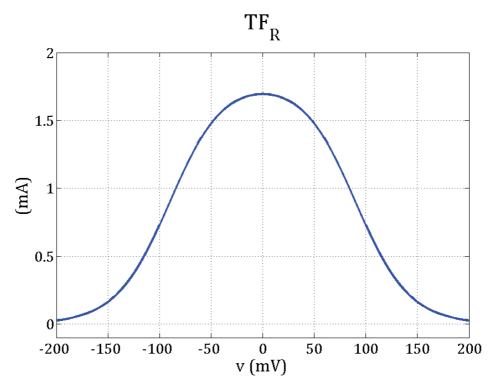

| 0             | : Transfer function $TF_R$ according to independent variable v                                         |    |

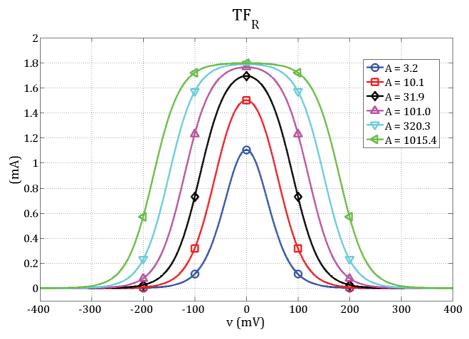

| 0             | <b>2:</b> The change of $TF_R$ for different values of A                                               | 36 |

|               | <b>3</b> : Different $i_R$ currents obtained form the same $v_0(t)$ for different values of <i>A</i> . | 36 |

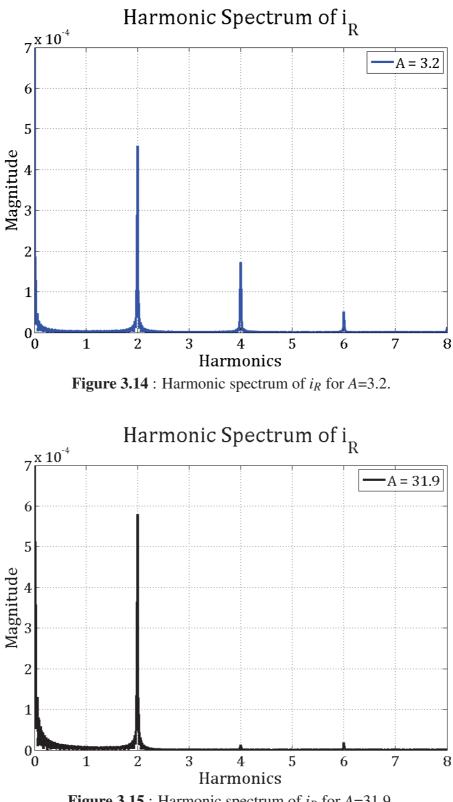

|               | : Harmonic spectrum of $i_R$ for $A=3.2$ .                                                             |    |

| -             | : Harmonic spectrum of $i_R$ for $A=31.9$ .                                                            | 37 |

| 0             | : Harmonic spectrum of $i_R$ for $A=320.3$ .                                                           |    |

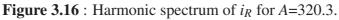

| -             | $i_C$ and $i_R$ currents for $A=31.9$                                                                  |    |

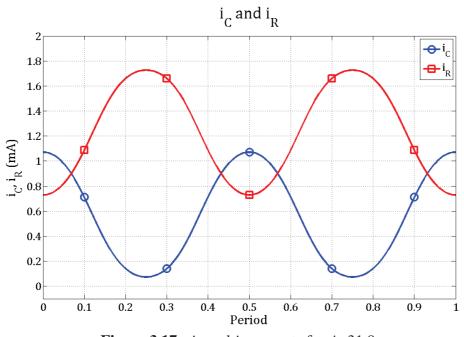

|               | <b>B</b> : The variation of the DC component coefficient of $i_C$ current                              |    |

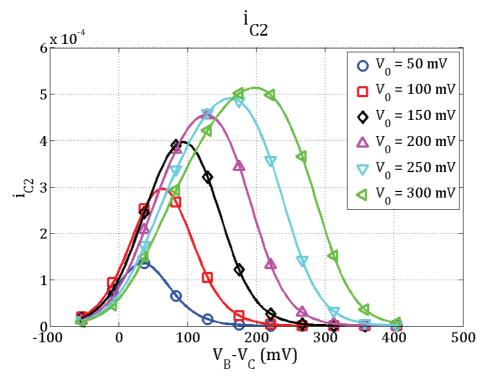

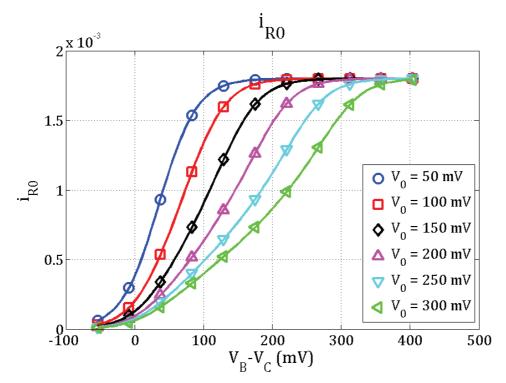

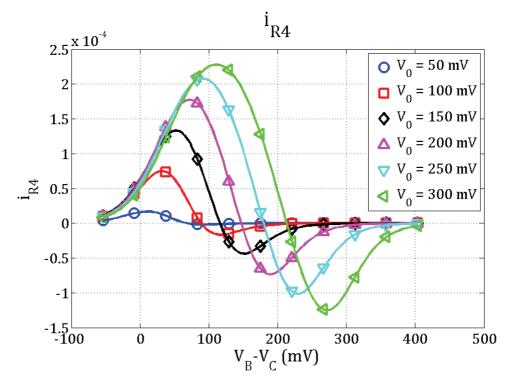

| 0             | according to $V_B - V_C$ voltage difference for different values of $V_0$                              | 40 |

|               |                                                                                                        |    |

| Figure 3.19: The variation of the second harmonic coefficient of $i_C$ current             |    |

|--------------------------------------------------------------------------------------------|----|

| according to $V_B - V_C$ voltage difference for different values of $V_0$                  | 40 |

| Figure 3.20: The variation of the fourth harmonic coefficient of $i_C$ current             |    |

| according to $V_B - V_C$ voltage difference for different values of $V_0$                  | 41 |

| Figure 3.21: The variation of the DC component coefficient of $i_R$ current                |    |

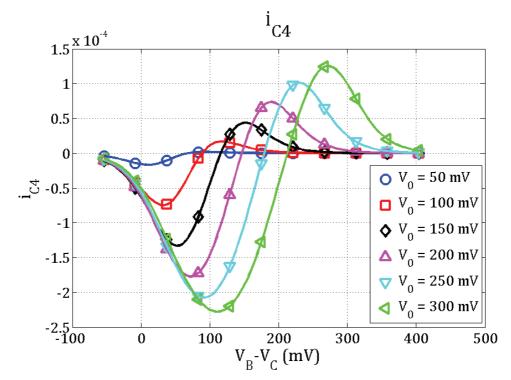

| according to $V_B - V_C$ voltage difference for different values of $V_0$                  | 42 |

| Figure 3.22: The variation of the second harmonic coefficient of $i_R$ current             |    |

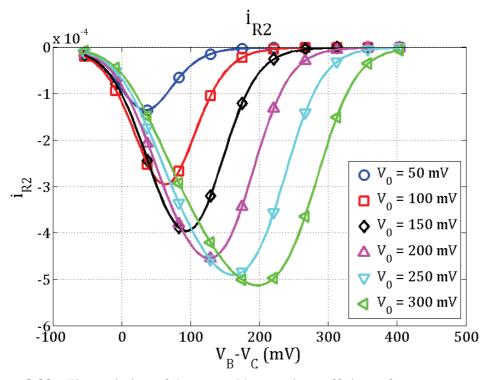

| according to $V_B - V_C$ voltage difference for different values of $V_0$                  | 42 |

| Figure 3.23: The variation of the fourth harmonic coefficient of $i_R$ current             |    |

| according to $V_B - V_C$ voltage difference for different values of $V_0$                  | 43 |

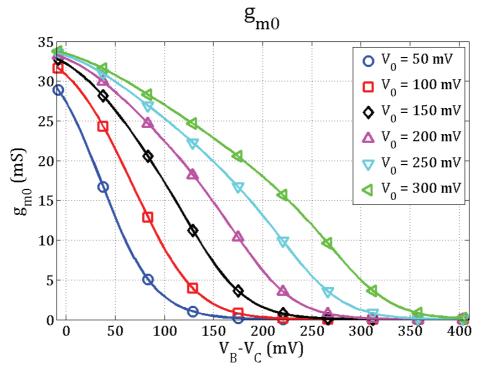

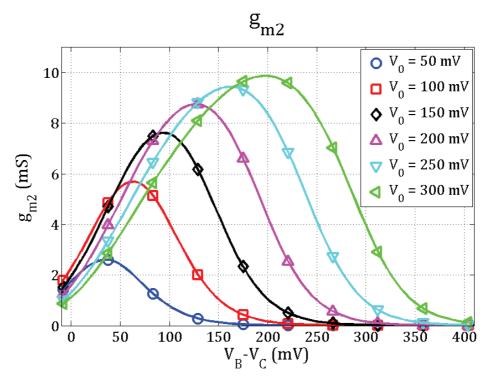

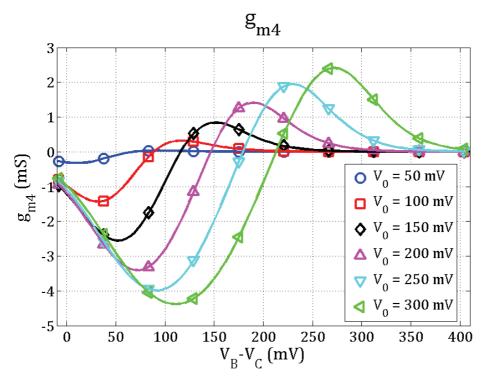

| <b>Figure 3.24:</b> The variation of the DC component coefficient of $g_m$ according to    |    |

| $V_B - V_C$ voltage difference for different values of $V_0$                               | 45 |

| <b>Figure 3.25:</b> The variation of the second harmonic coefficient of $g_m$ according    |    |

| to $V_B - V_C$ voltage difference for different values of $V_0$                            | 45 |

| <b>Figure 3.26:</b> The variation of the fourth harmonic coefficient of $g_m$ according to |    |

| $V_B - V_C$ voltage difference for different values of $V_0$                               | 46 |

| <b>Figure 3.27:</b> Conversion voltage gain according to $V_B - V_C$ voltage difference    |    |

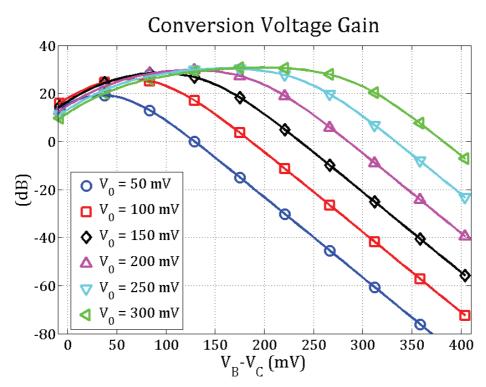

| for different values of $V_0$                                                              | 48 |

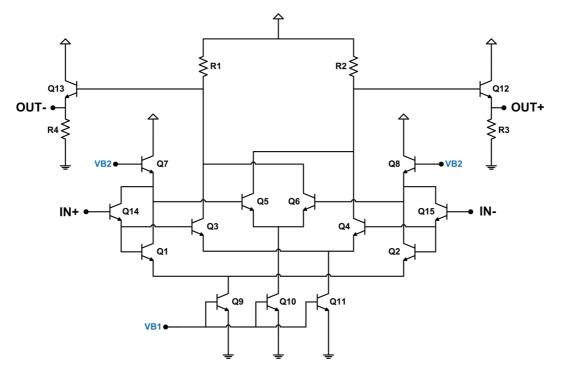

| Figure 3.28: IF amplifier circuit schematic                                                | 50 |

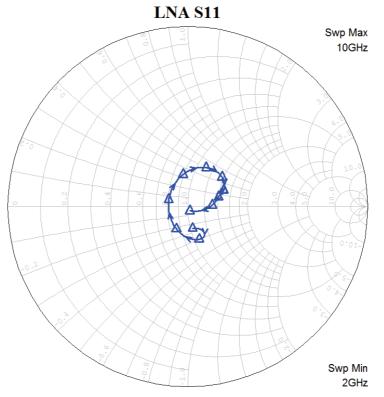

| Figure 4.1 : The S11 parameter of the LNA shown on Smith Chart                             | 53 |

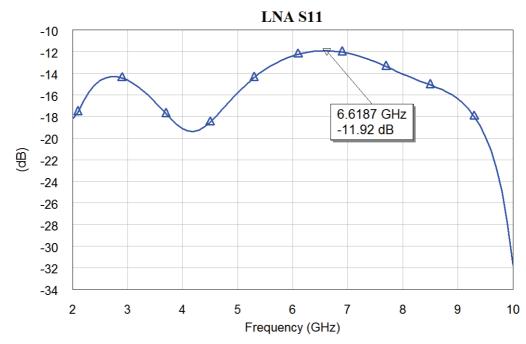

| Figure 4.2 : Magnitude of the S11 parameter of the LNA shown on rectangular                |    |

| coordinates                                                                                | 53 |

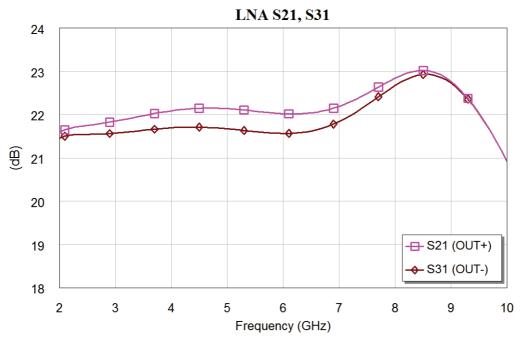

| Figure 4.3 : S21 and S31 parameters of the LNA                                             | 54 |

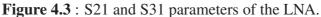

| Figure 4.4 : 1 dB compression point of the LNA.                                            | 54 |

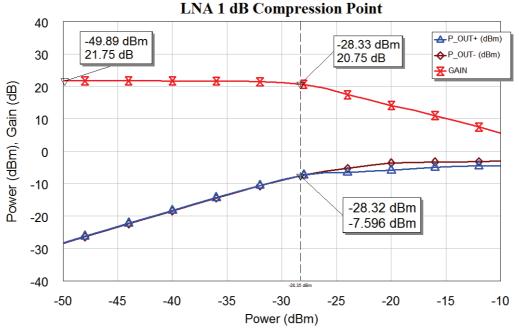

| Figure 4.5 : Noise figure of the LNA.                                                      | 55 |

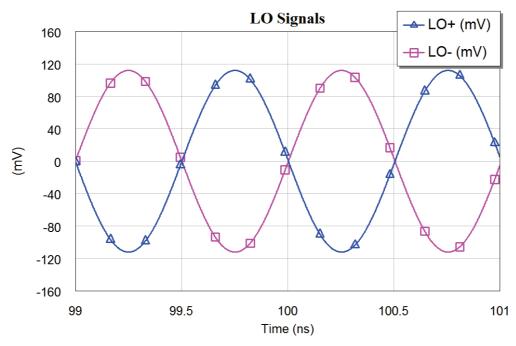

| <b>Figure 4.6</b> : The time varying part of the differential LO signals, $v_0(t)$         | 56 |

|                                                                                            |    |

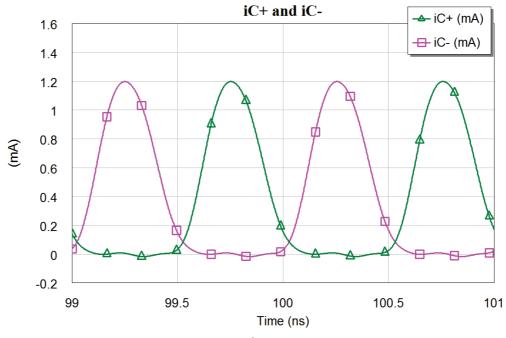

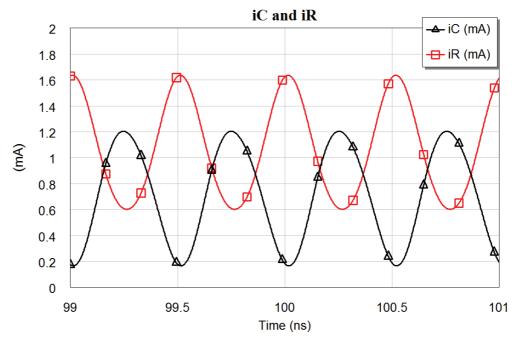

| <b>Figure 4.8</b> : The pumping current $i_C$ and the residue current $i_R$                |    |

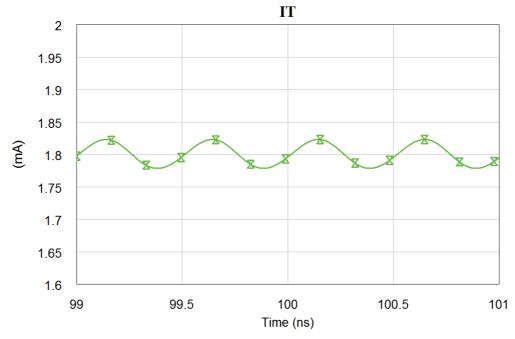

| <b>Figure 4.9</b> : The change of the total biasing current $I_T$                          | 58 |

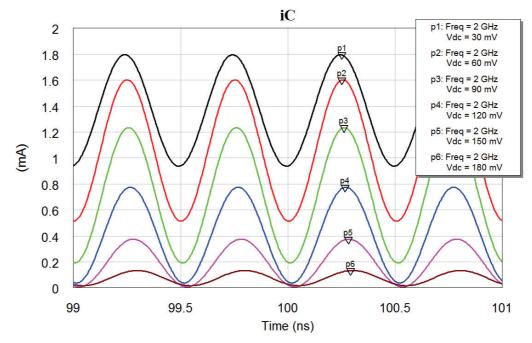

| Figure 4.10: The pumping current $i_C$ for different values of biasing voltage             |    |

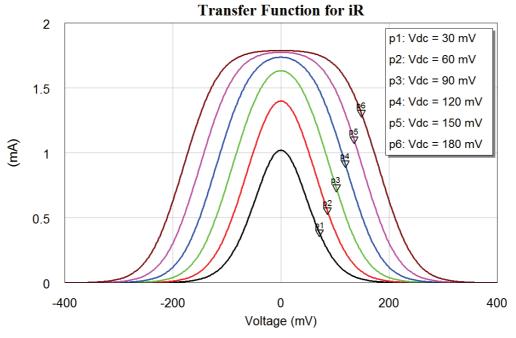

| difference $V_B - V_C$ .                                                                   | 59 |

| Figure 4.11: The residue current $i_R$ for different values of biasing voltage             |    |

|                                                                                            | 59 |

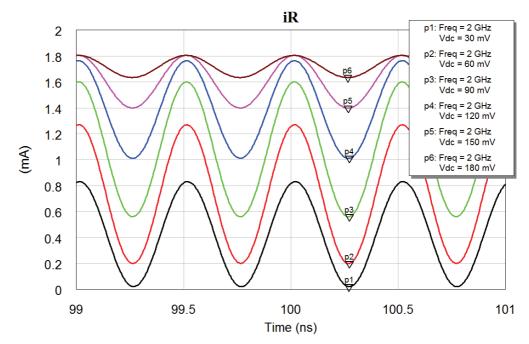

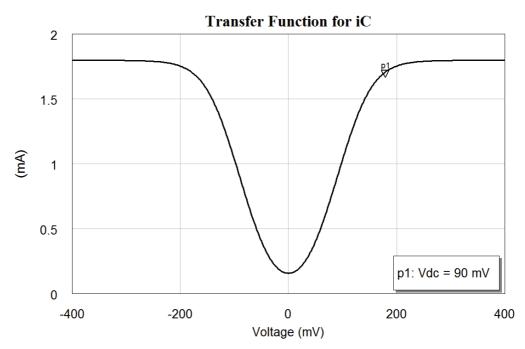

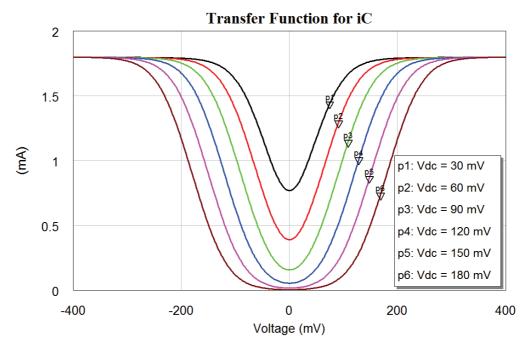

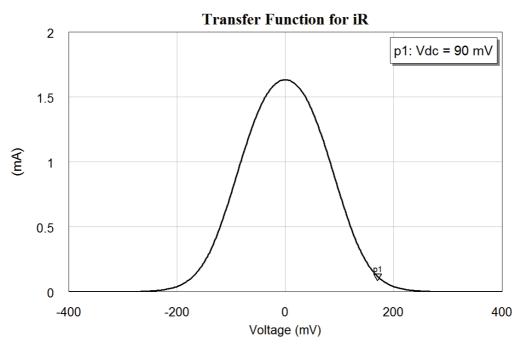

| Figure 4.12: Transfer function $TF_C$ under proper biasing conditions                      | 61 |

| Figure 4.13: Transfer function $TF_C$ for different biasing voltage differences            |    |

| $V_B - V_C$                                                                                | 61 |

| <b>Figure 4.14:</b> Transfer function $TF_R$ under proper biasing conditions               | 62 |

| Figure 4.15: Transfer function $TF_R$ for different biasing voltage differences            |    |

| $V_B - V_C$                                                                                | 62 |

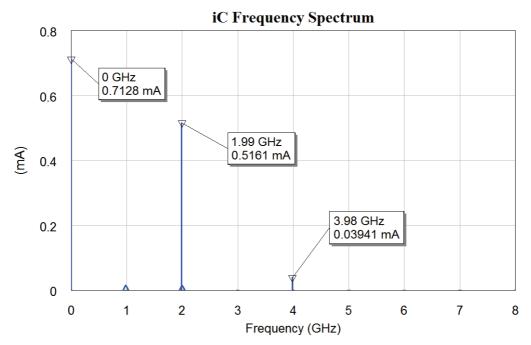

| Figure 4.16: Frequency Spectrum of the pumping current $i_C$ under proper                  |    |

| operating conditions                                                                       | 63 |

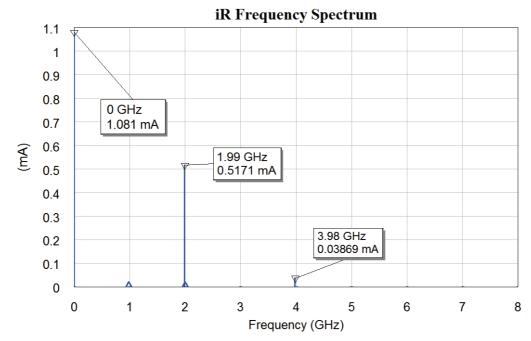

| Figure 4.17: Frequency Spectrum of the residue current $i_R$ under proper                  |    |

| operating conditions                                                                       | 63 |

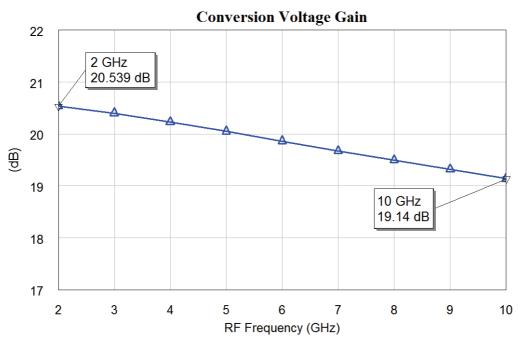

| Figure 4.18: The conversion voltage gain of the proposed mixer topology within             |    |

| 2-10 GHz RF frequency range.                                                               | 64 |

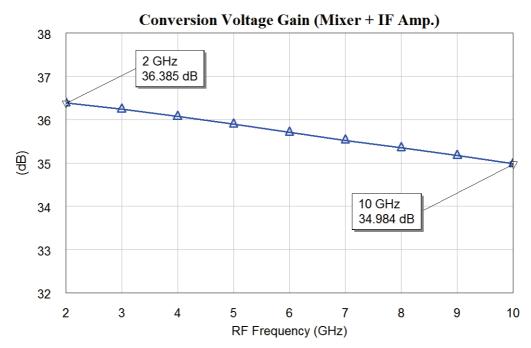

| Figure 4.19: Total conversion voltage gain within 2-10 GHz RF frequency                    |    |

| range when the mixer and the IF amplifier is connected together                            | 65 |

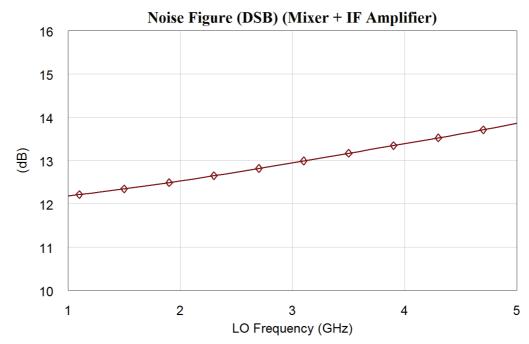

| Figure 4.20 | : Total noise figure within 1-5 GHz LO frequency range when the         |    |

|-------------|-------------------------------------------------------------------------|----|

|             | mixer and the IF amplifier is connected together                        | 65 |

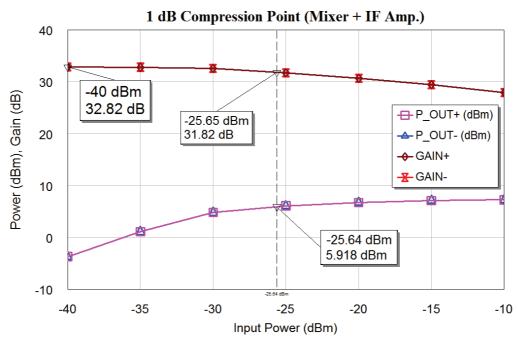

| Figure 4.21 | :1 dB compression point when the mixer and the IF amplifier is          |    |

|             | connected together.                                                     | 66 |

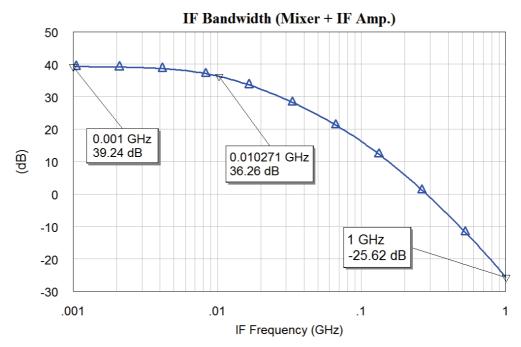

| Figure 4.22 | : IF bandwidth of the combined structure of the mixer and the IF        |    |

|             | amplifier                                                               | 67 |

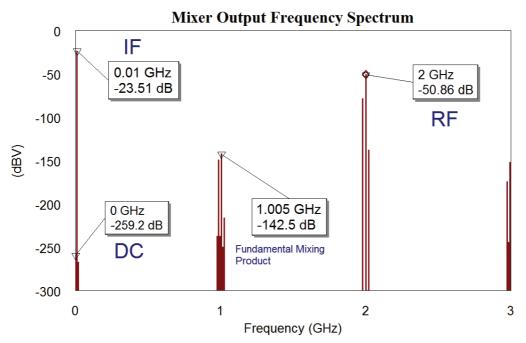

| Figure 4.23 | : Output frequency spectrum of the mixer                                | 68 |

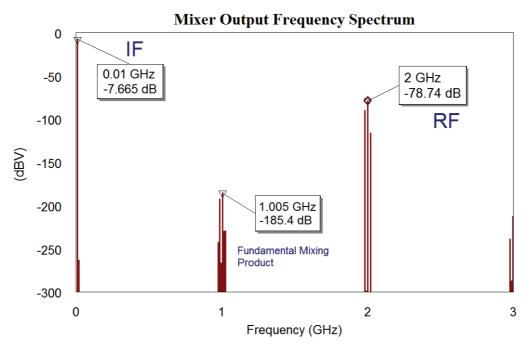

| Figure 4.24 | : Output frequency spectrum of the IF amplifier                         | 68 |

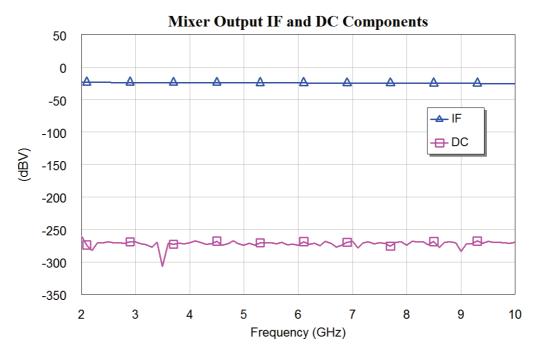

| Figure 4.25 | F: IF and DC components at the mixer output for the whole RF            |    |

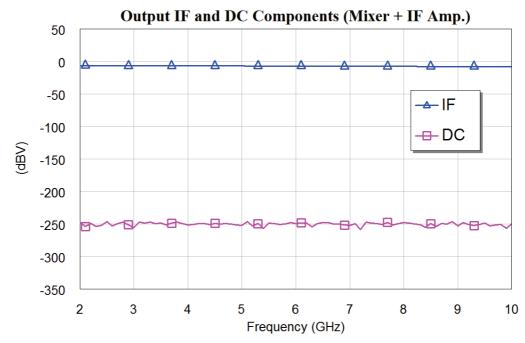

|             | frequency range                                                         | 6  |

| Figure 4.26 | : IF and DC components at the IF amplifier output for the whole RF      |    |

|             | frequency range                                                         | 6  |

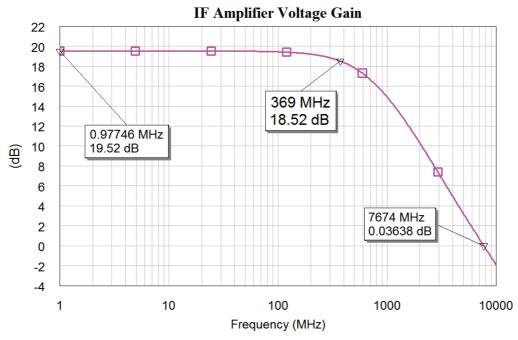

| Figure 4.27 | : IF amplifier voltage gain according to frequency                      | 70 |

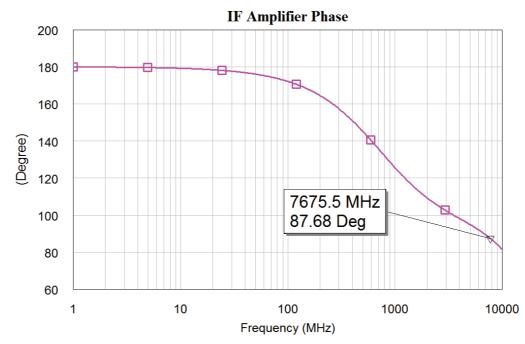

| Figure 4.28 | : IF amplifier phase shift according to frequency                       | 7  |

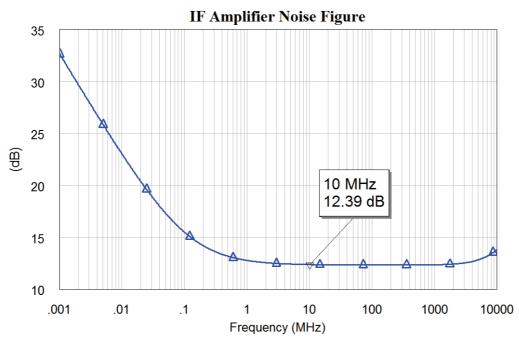

| Figure 4.29 | : IF amplifier noise figure according to frequency                      | 7  |

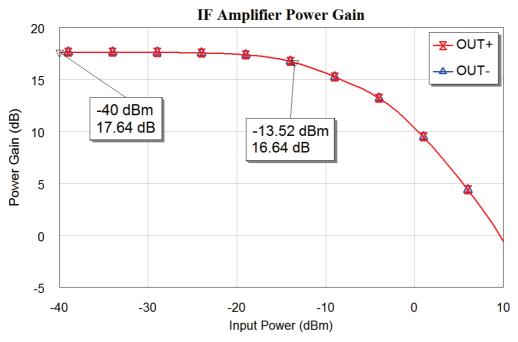

|             | : IF amplifier power gain according to input power                      | 7  |

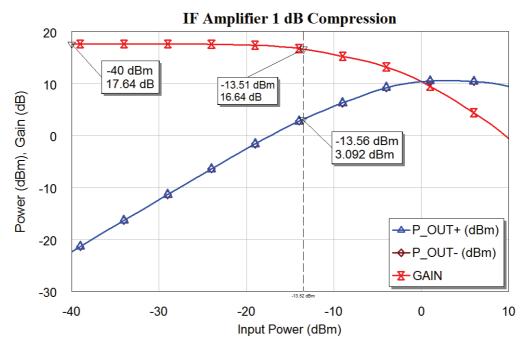

| -           | : IF amplifier output power and the 1 dB compression point              | 7  |

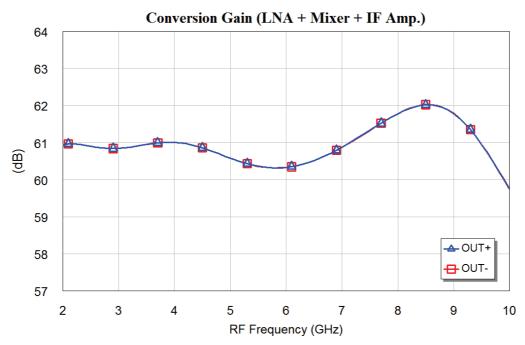

|             | : The overall conversion gain graph of the receiver topology            | 7  |

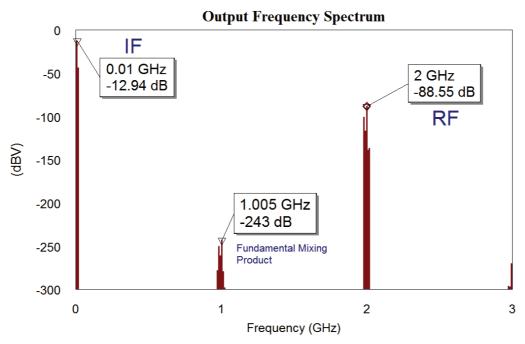

| 0           | <b>B</b> : The frequency spectrum of the IF signal.                     | 7. |

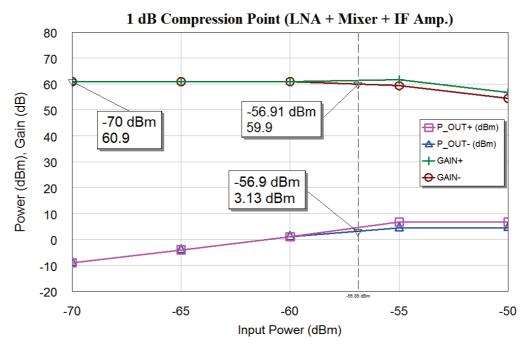

| 0           | <b>:</b> 1 dB compression point of the overall receiver circuit         | 7  |

| -           | : Layout of the LNA.                                                    |    |

|             | : Layout of the second stage of the LNA                                 |    |

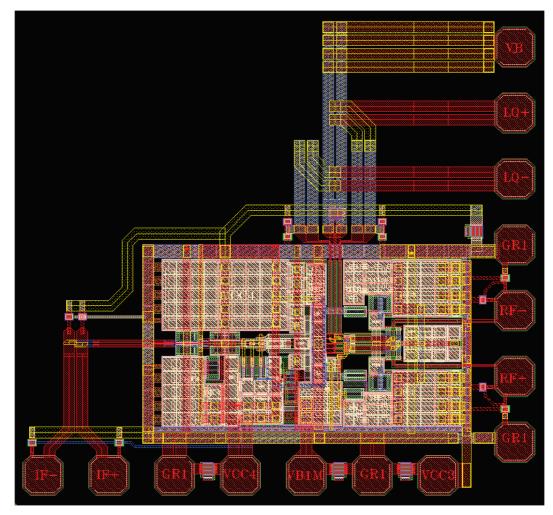

| -           | : LNA layout prepared for MPW placement.                                | 8( |

|             | : Layout of the second harmonic mixer and the IF amplifier arranged     |    |

| 8           | for MPW placement.                                                      | 8  |

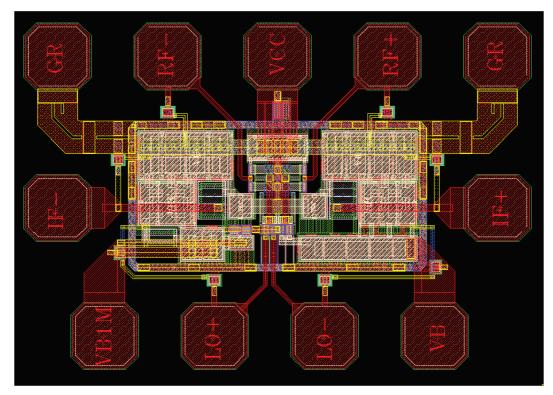

| Figure 5.5  | : Layout for separate placement of the proposed second harmonic         |    |

| 8           | mixer.                                                                  | 82 |

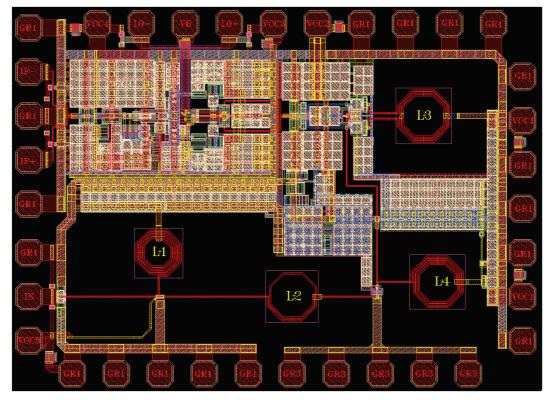

| Figure 5.6  | : Layout of the integrated receiver topology                            | 8. |

| -           | : Layout of the integrated receiver topology                            | 84 |

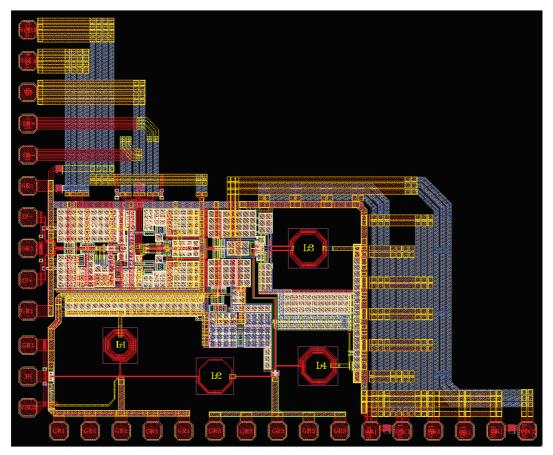

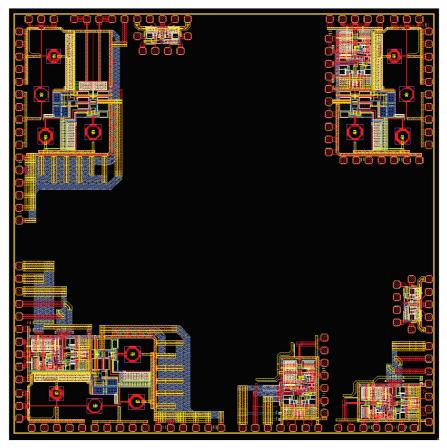

| 0           | : Placement of the layouts of the test structures on the MPW die        | 8. |

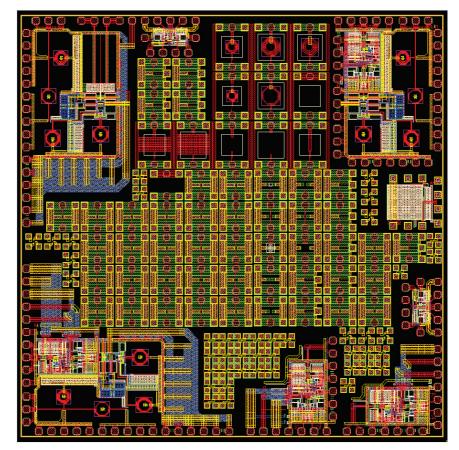

| -           | : Final layout of the MPW chip.                                         |    |

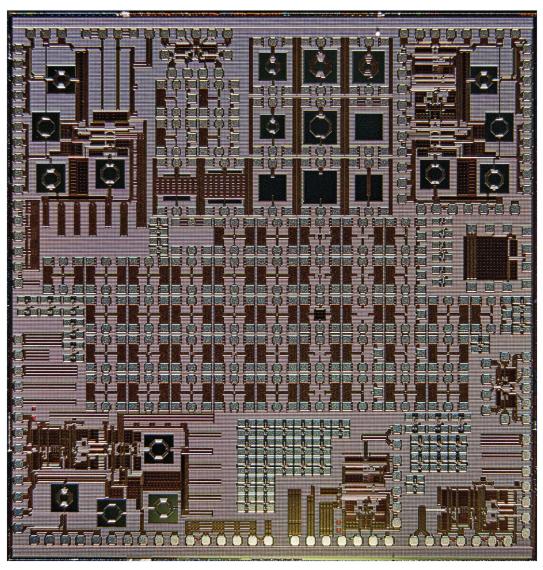

| -           | : Photograph of the manufactured test IC                                |    |

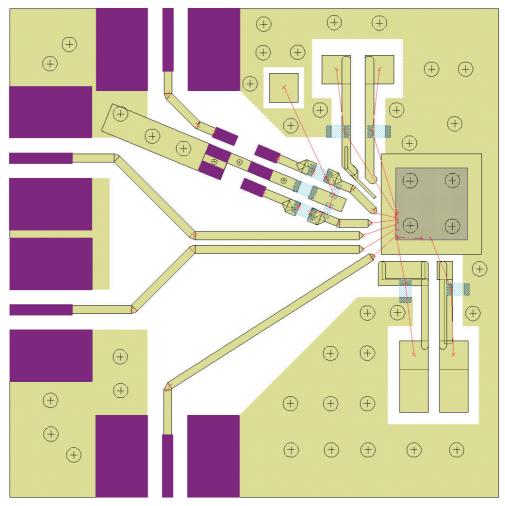

|             | : Layout of the first test PCB.                                         |    |

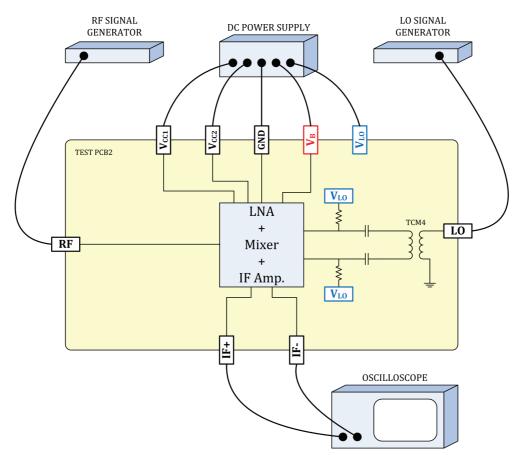

| -           | : Test setup for the conversion gain measurements of the Mixer + IF     |    |

| -80 0.0     | Amplifier test structure.                                               | 90 |

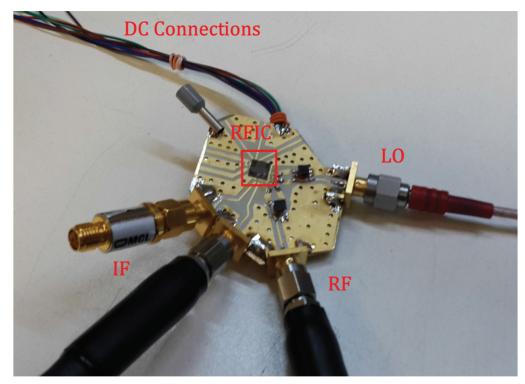

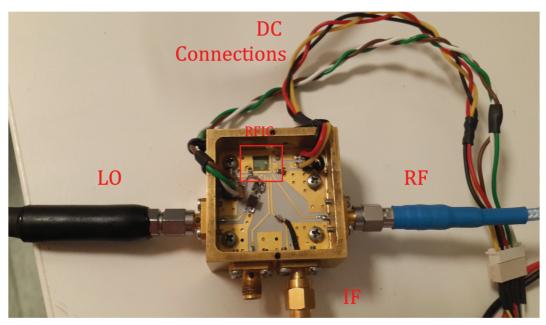

| Figure 6.4  | : Photograph of the first test PCB in the actual testing environment    |    |

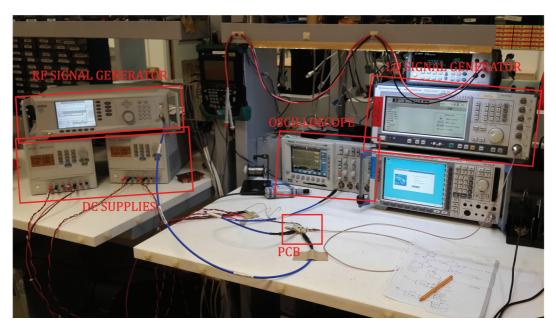

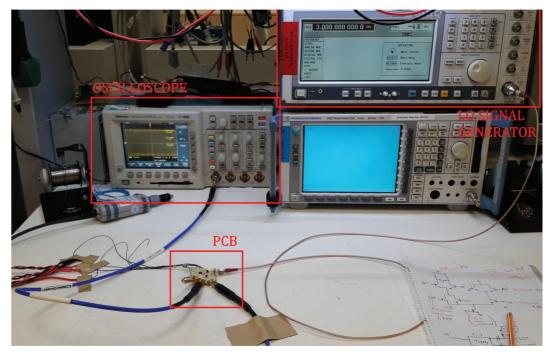

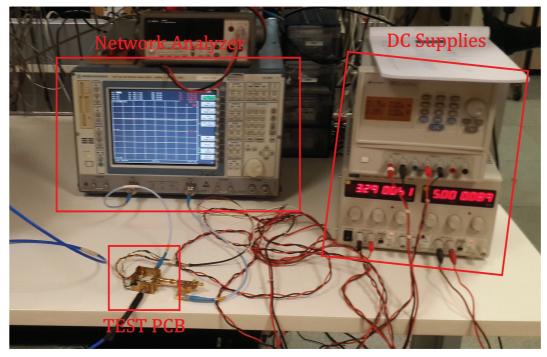

| -           | : Photograph of the actual testing environment.                         | 9  |

| -           | : Photograph of the actual testing environment                          |    |

| U           | : Measured peak-to-peak IF amplitude, $V_{PP}$ , according to the input |    |

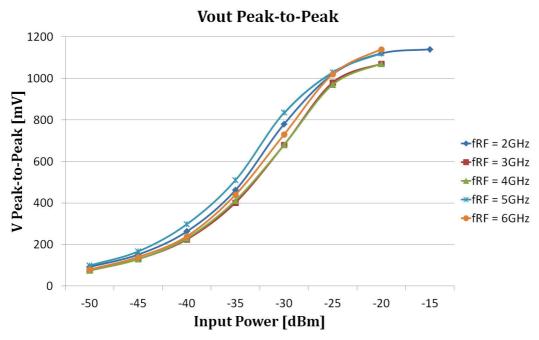

| -8 0 007    | RF power at different frequencies                                       | 94 |

| Figure 6.8  | : Calculated IF power, $P_{IF}$ , according to the input RF power at    | -  |

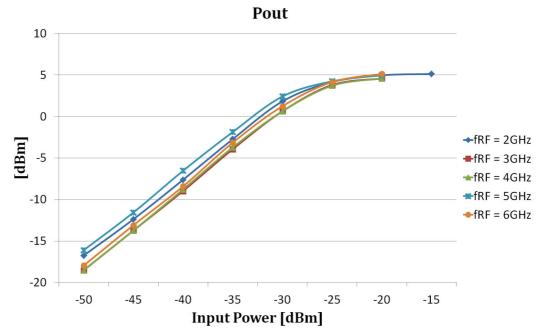

| -80 000     | different frequencies.                                                  | 9  |

| Figure 6.9  | :Calculated conversion gain according to the input RF power at          |    |

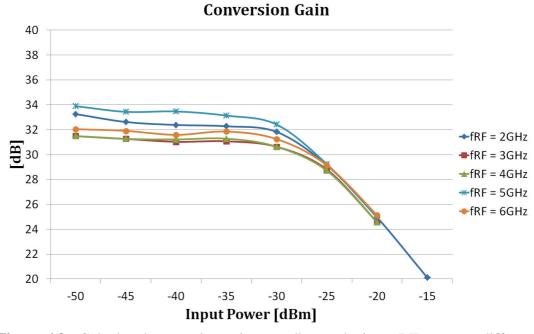

|             | different frequencies.                                                  | 9  |

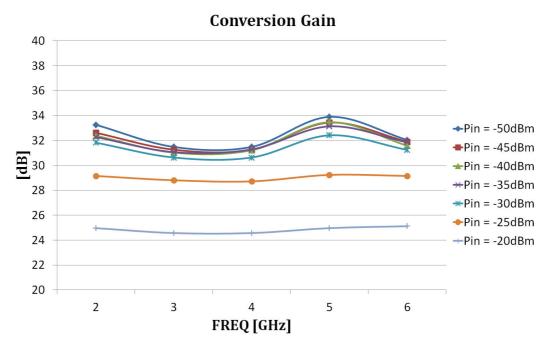

| Figure 6.10 | : Calculated conversion gain according to the input frequency           | 9  |

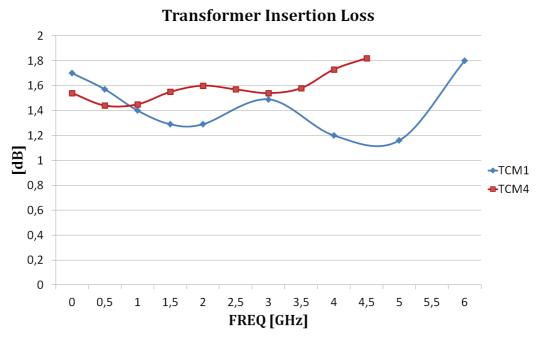

| 0           | : Loss of the transformers used for RF and LO signal paths              |    |

| 0           | r                                                                       |    |

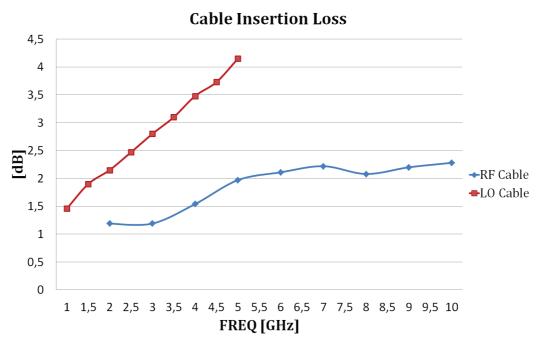

| Figure 6.12: Loss of RF and LO connection cables according to frequency             |

|-------------------------------------------------------------------------------------|

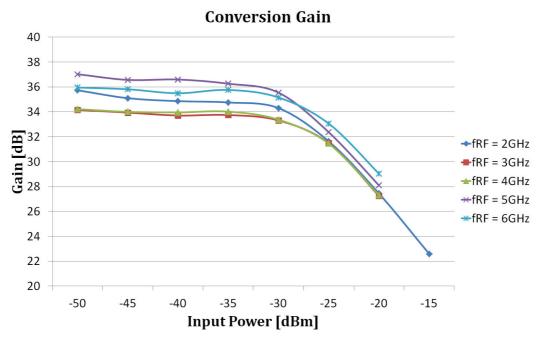

| Figure 6.13: Conversion Gain according to the input RF power at different           |

| frequencies when cable and transformer losses are added                             |

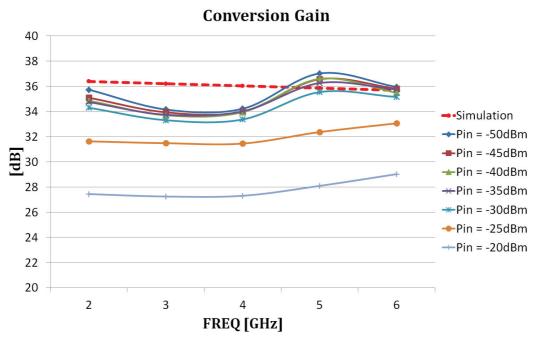

| <b>Figure 6.14:</b> Conversion Gain according to the input frequency when cable and |

| transformer losses are added                                                        |

| Figure 6.15: Test setup for measuring the second harmonic component leakage         |

| of the LO signal to the RF port of the Mixer + IF Amplifier test                    |

| structure                                                                           |

| Figure 6.16: The static DC offset seen at the IF outputs                            |

| Figure 6.17: Test setup for measuring the static DC offset due to component         |

| mismatches101                                                                       |

| Figure 6.18: IF outputs from which the measured static DC offset is subtracted102   |

| Figure 6.19: Layout of the second test PCB                                          |

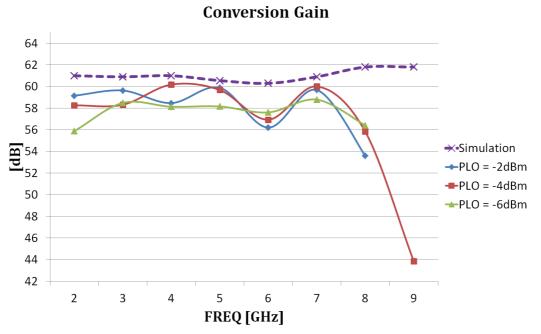

| Figure 6.20: Test setup for the conversion gain measurements of the                 |

| LNA + Mixer + IF Amplifier test structure104                                        |

| Figure 6.21: Photograph of the second test PCB104                                   |

| Figure 6.22: Photograph of the actual testing environment                           |

| Figure 6.23: Conversion gain according to RF frequency                              |

| Figure 6.24: Conversion gain according to RF frequency without the RF cable         |

| losses                                                                              |

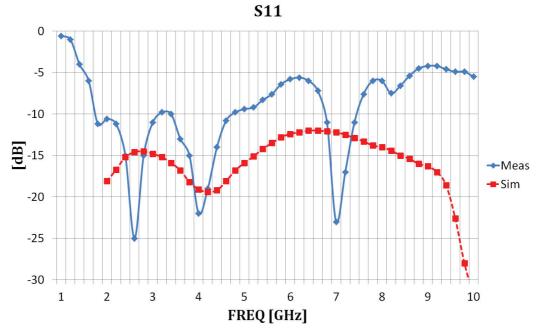

| Figure 6.25: Test setup for the measurement of S11                                  |

| Figure 6.26: Measurement and simulation results for S11109                          |

#### ZERO-IF SECOND HARMONICALLY PUMPED SIGE TRANSCEIVER INTEGRATED CIRCUIT

#### SUMMARY

The increasing number of mobile devices and the variety of new application areas arisen recently, accelerate the evolution of wireless communication systems. As the technology approaches to the concept of communicating everything, the improvement of wireless systems appear as a necessity to step forward. Thus, the requirements of the evolving technology determine the specifications to be satisfied by the transceivers of the wireless systems. To be deployed by many mobile devices, the transceivers should be simple in structure and integrated, since the area and the power consumption are main concerns of these kind of devices. Besides, it is expected from the mobile devices to include different types of wireless applications operating simultaneously. For the sustainability of the development of the mobile devices, they should benefit from simple and integrated transceivers.

As it is explained in Chapter 1, the purpose of the study is to develop a compact and integrated receiver solution for the wireless communication systems. The Homodyne, namely the Zero-IF architecture is selected to be implemented to use the advantage of simplicity of this type of receivers. It is aimed to provide adequate solutions to the well known problems of Zero-IF receivers by utilizing the proper techniques with the proper technology. The current literature is reviewed and the contributions made on the issue is summarized in Chapter 1.

Since the most of the problems of the Zero-IF transceivers are arisen from the equality of the local oscillator (LO) frequency and carrier frequency, the second harmonic mixing technique brings fundamental solutions to these problems. The half of the carrier frequency is used as the LO frequency in the second harmonic mixing technique. The fundamental mixing product at the output is suppressed and the second harmonic term is taken as the output signal. Using such a mixing technique breaks the equality of the carrier frequency and the LO frequency. Using the virtual signal of which frequency is two times the LO frequency as the mixing signal also prevents conversion of the phase noise of the oscillator signal into the signal band at the output. Realizing the local oscillator for half of the actually required frequency eases the design concerns of the oscillator. The advantages brought by using the second harmonic mixing technique is explained in details in Section 1.4.

For the integration of the Zero-IF receiver topology, SiGe BiCMOS semiconductor processing technology is selected to be used. SiGe is a semiconductor technology which is suitable for RFIC applications. The technology includes high speed transistors, high quality passive components and CMOS transistors. The variety of high performance devices provided together with the CMOS transistors suitable for dense digital circuits make it possible to easily integrate the complex mixed signal high frequency systems on the same chip. SiGe technology evolves from the well known Si

processes thus the knowledge and the infrastructure transfer during the development of the process make it easily accessible and low cost. The details about the SiGe technology is explained in Section 1.5.

The transceiver architectures Heterodyne and Homodyne are explained in Chapter 2. The Heterodyne is the widely used architecture which is mainly performing the frequency conversion in two steps by using an intermediate frequency (IF). Although they include more circuit blocks, these kind of architectures are preferred in many applications just to be stay away from the problems of the direct conversion. Heterodyne architectures are mostly realized with discrete components because of the complexity and the requirement of extra filtering. On the other hand, the Homodyne architectures, namely the Zero-IF architectures perform the frequency conversion in one step. Decreasing the number of building blocks and eliminating some filters, Homodyne architectures present a much simpler structure. However, Homodyne architectures bring some serious problems to be solved. These problems are detailed in Chapter 2.

To build up a Zero-IF receiver circuit, a low noise amplifier (LNA), a second harmonic mixer and an IF amplifier circuits are combined on a single integrated circuit. The topologies of these building blocks of the Zero-IF receiver circuit is explained in details separately in Chapter 3. The circuit schematics are given and the design concerns are explained. A fully differential structure is constructed through out the signal path. The topologies are selected accordingly to provide wide band operation. The receiver covers a variety of applications with a single structure. Covering variety of application bands also provides the ability to reuse the receiver for different services.

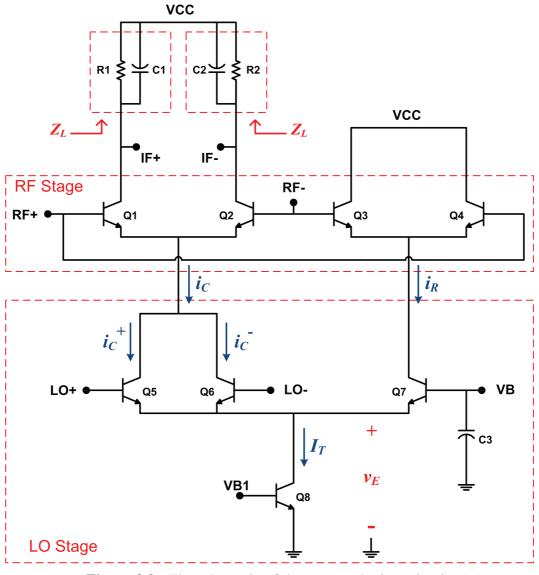

In Chapter 3, a new topology for the second harmonic mixer is proposed. The new topology on which the primary contribution is made provides an adequate mechanism to prevent the well known DC offset voltage problem of the Zero-IF receivers. By satisfying a constant DC current flow through the mixer circuit, the propagation of the large signal LO to the RF signal path through the supply lines and the substrate is prevented. The new mixing concept of operating with a constant DC current in some sense isolates the noisy mixer circuit from the rest of the building blocks. The large signal pumping current only occurs locally within the proposed mixer circuit. This is a crucial advantage especially for large scaled integrated mixed signal solutions.

The explanation of the new topology is made in Chapter 3. A detailed analysis is performed on the circuit and proper biasing conditions are exhibited. The effects of the biasing conditions over the circuit performance is shown with analytical results. The equations for the pumping current of which dominant frequency component is two times the LO frequency and the residue current which is the remaining part of the total DC current drawn from the supply voltage are derived from the large signal analysis. The change of the relevant harmonic components of the pumping current are shown according to the amplitude of LO signal and the DC biasing levels. On the graphs, how to find an optimum biasing point for a given LO amplitude is shown.

The explained circuit schematics are constructed and simulated within various test benches. The simulation results of the individual circuit blocks and the combined blocks are given in Chapter 4. The simulations of the LNA and the IF amplifier circuits are performed separately to examine the performance of these blocks. The proposed mixer simulations are given to show not only the performance of the mixer but also to verify the results given in the analysis in Chapter 3. It is exhibited that the similar results with the analysis regarding the performance of the mixer is obtained in simulations. The pumping current and the residue current graphs are obtained for the same biasing conditions as in the analysis. The simulation results of the overall receiver is also shown in Chapter 4.

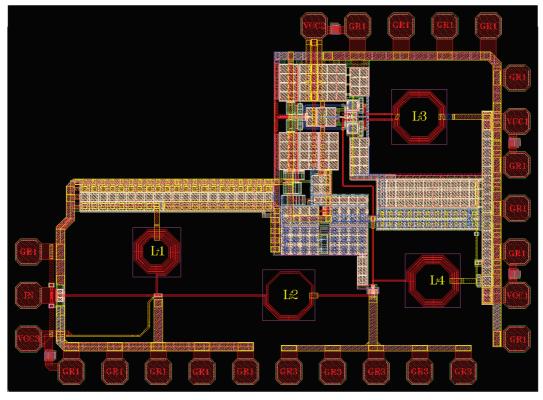

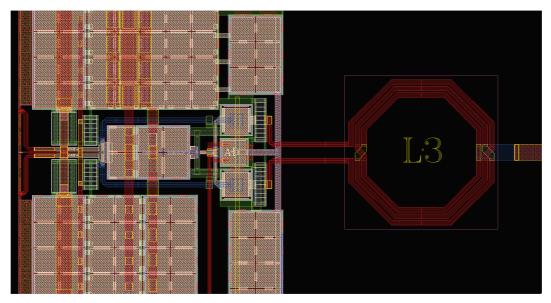

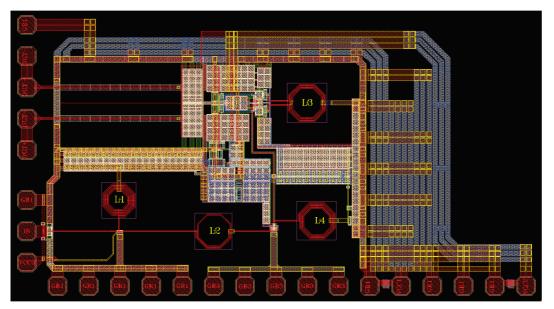

Chapter 5 is where the realization of the designed receiver is explained. The layout of the whole receiver circuit and the building blocks separately are drawn and placed for a Multi-Project Wafer (MPW) production. According to the predefined 5 mm $\times$ 5 mm integrated circuit area for MPW production, several separate layouts are prepared and placed for testing purposes. The prepared layouts are given in Chapter 5 and explained.

In Chapter 6, the preparation of the test setups and the testing environment are described and the acquired measurement results are given. Two separate Printed Circuit Boards (PCB) are designed to measure two test structures on the manufactured IC. Measurements performed on the first PCB is aimed to show the conversion gain performance of mixer on which the main contribution is made and to show the effectiveness of the proposed structure on the DC offset problem. The second PCB is used to measure the overall receiver structure consisting of LNA, mixer and the IF amplifier. Measurement results are compared to simulation results to show the correlation between theory and the practice.

The conclusions of the study are summarized in Chapter 7.

### SIFIR ARA SIKLIKLI İKİNCİ HARMONİK POMPALAMALI SiGe ALICI-VERİCİ TÜMDEVRESİ

#### ÖZET

Mobil cihazların gün geçtikçe artması ve yeni kablosuz iletişim uygulama alanlarının ortaya çıkması, kablosuz iletişim sistemlerinin gelişimini hızlandırmaktadır. Teknoloji herşeyi birbiriyle haberleştirme kavramına yaklaştıkça, daha ileriye gidebilmek için kablosuz iletişim sistemlerinin geliştirilmesi bir gereklilik olarak ortaya çıkmaktadır. Bu nedenle, gelişen teknoloji ihtiyaçları kablosuz haberleşme sistemlerinde kullanılan alıcı-vericirilerin de sağlaması gereken teknik özellikleri belirlemektedir. Mobil cihazlar için en önemli kriterler alan ve güç tüketimi olduğundan, bir çok mobil cihaz tarafından kullanılabilmesi için alıcı-vericilerin basit ve tümleşik bir yapıya sahip olmaları gerekmektedir. Ayrıca, bu mobil cihazların farklı kablosuz iletişim uygulamalarını barındırması ve bu uygulamaları eş zamalı olarak çalıştırabilmesi için bu cihazların, basit ve tümleşik alıcı-verici bloklarının faydalarını kullanımaları gerekmektedir.

Bölüm 1'de anlatıldığı gibi bu çalışmanın amacı kablosuz iletişim sistemlerinde kullanılmak üzere basit bir yapıya sahip ve tek tümdevre üzerinde tümleştirilmiş bir alıcı yapısı geliştirmektir. Bu amaca yönelik olarak Homodyne, diğer adıyla Sıfır Ara Sıklıklı yapı kullanılarak bu yapıların basitliğinden faydalanılmıştır. Uygun teknikleri ve uygun teknolojiyi kullanarak bu yapıların herkesçe bilinen önemli sorunlarına çözümler sunulması amaçlanmıştır. Konu ile ilgili var olan literatür araştırması ve bu çalışmada yapılan katkılar Bölüm 1'de özetlenmiştir.

Sıfır Ara Sıklıklı alıcı-verici yapılarının sorunlarının büyük çoğunluğu yerel osilatör sıklığı ile taşıyıcı sıklığının birbirine eşit olmasından kaynaklanmaktadır. Bu nedenle ikinci harmonik pompalamalı karıştırma tekniği bu sorunlara temel çözümler sunmaktadır. İkinci harmonik pompalamalı karıştırma tekniğinde yerel osilatör sıklığı olarak taşıyıcı sıklığının yarısı kullanılmaktadır. Karıştırıcı çıkışında temel karıştırma terimi bastırılarak, yerel işaretin ikinci harmoniği ile ilgili karıştırma terimi çıkış işareti olarak seçilmektedir. Böyle bir karıştırma tekniğinin kullanılması yerel osilatör sıklığının taşıyıcı sıklığına eşitliğini bozmaktadır. Karıştırma için yerel osilatör sıklığının taşıyıcı sıklığına eşitliğini bozmaktadır. Karıştırma için yerel osilatör sıklığının iki katı sıklıkta sanal bir işaret kullanılması, bir başka önemli sorun olan yerel osilatör faz gürültüsünün çıkıştaki işaret bandı içerisine dönüştürülmesini de engellemektedir. Ayrıca, yerel osilatörü gerçekte ihtiyaç duyulan sıklığın yarısını sağlayacak şekilde tasarlamak, yerel osilatörün gerçekleştirilmesindeki zorlukları da kolaylaştırmaktadır. İkinci harmonik pompalamalı karıştırma tekniğinin kullanılması ile sağlanan yararlar Bölüm 1.4'de detaylı olarak anlatılmaktadır.

Tasarlanan Sıfır Ara Sıklıklı alıcı topolojisinin tümleştirilmesinde kullanılmak üzere SiGe BiCMOS üretim teknolojisi seçilmiştir. SiGe özellikle yüksek sıklıklı tümdevre (RFIC) tasarımları için uygun olan bir yarıiletken teknolojisidir. Bu teknoloji, yüksek hızlı transistorlar, yüksek kalite faktörlü pasif devre elemanarı ve yoğun sayısal devre tasarımları için uygun olan CMOS transistorları içermektedir. Böylece, yüksek karmaşıklıkta karışık işaret tasarımlarının tek tümdevre üzerinde kolayca tümleştirilmesine olanak sağlamaktadır. SiGe teknolojisi iyi bilinen silisyum (Si) üretim teknolojilerinden geliştirilmiş bir teknoloji olduğundan dolayı, geliştirilme aşamasında Si teknolojilerinde elde edilmiş olan bilgi birikimi ve altyapının kullanılması, bu teknolojinin kolayca ve ucuza ulaşılabilir olmasını sağlamıştır. SiGe teknolojisi hakkında detaylı bilgi Bölüm 1.5'de verilmiştir.

Heterodyne ve Homodyne alıcı-verici yapıları Bölüm 2'de detaylı olarak anlatılmaktadır. Heterodyne yapıları geniş olarak tercih edilen ve sıklık dönüştürme işlemini bir ara sıklık (IF) kullanarak iki adımda gerçekleştiren alıcı-verici yapılarıdır. Daha fazla devre bloğu kullanılmasına rağmen bu alıcı-verici yapıları doğrudan sıklık dönüştürme işleminin getirdiği sorunlardan uzak durulması için bir çok uygulamada tercih edilmektedirler. Yapılarındaki karmaşıklık ve ihtiyaç duyulan fazladan filtreleme işlemlerinden dolayı Heterodyne alıcı-verici yapıları genel olarak ayrık elemanlarla gerçekleştirilmektedirler. Homodyne yapılar, diğer adıyla Sıfır Ara Sıklıklı alıcı-vericiler ise sıklık dönüştürme işlemini doğrudan tek bir adımda gerçekleştirmektedirler. Kullanılan devre bloklarının azaltılması ve bazı filtrelerin atılması sayesinde bu alıcı-vericiler çok daha basit bir yapı sağlamaktadırlar. Fakat, Homodyne alıcı-vericiler beraberinde bazı önemli sorunlar getirmektedirler. Homodyne alıcı-vericiler ait bu önemli sorunlar Bölüm 2'de detaylı olarak anlatılmaktadır.

Sıfır Ara Sıklıklı bir alıcı devresi oluşturmak için, bir düşük gürültülü kuvvetlendirici (LNA), bir ikinci harmonik karıştırıcı ve bir IF kuvvetlendirici devresi tek bir tümdevre üzerinde bir araya getirilmiştir. Sıfır Ara Sıklıklı alıcı devresine ait bu yapı bloklarının devre topolojileri ayı ayrı olarak Bölüm 3'de anlatılmaktadır. Bu bloklara ait devre şemaları verilmiş ve tasarım aşamasında dikkat edilen noktalar açıklanmıştır. Bütün işaret yolu boyunca tam dengeli farksal bir yapı oluşturulmaya çalışılmıştır. Yapı blokları için seçilen topolojiler geniş bantlı çalışmaya uygun olacak şekilde seçilmiştir. Böylece alıcı devresinin tek bir yapı ile çeşitli uygulamaları bir arada destekleyebilmesi sağlanmıştır. Çeşitli uygulamaları desteklemesi aynı zamanda alıcı devresinin çoklu kullanılabilirliğini de sağlamıştır.

Bölüm 3'de ikinci harmonik karıştırıcı için yeni bir devre topolojisi önerilmiştir. Asıl katkının sağlandığı bu yeni devre topolojisi, içerdiği uygun bir mekanizma sayesinde, Sıfır Ara Sıklıklı alıcıların en önemli sorunlarından biri olan DC dengesizlik gerilimi sorununa çözüm getirmektedir. Bütün karıştırıcı devresinin üzerinden akan, beslemeden çekilen toplam akımın sabit tutulmasından dolayı, büyük genlikli yerel osilatör işaretinin besleme hatları ve taban üzerinden diğer bloklara ve RF işaret yoluna sızması engellenmektedir. Yeni sunulan sabit akım akıtarak karıştırma işlemini gerçekleştirme kavramı bir anlamda yüksek gürültülü karıştırıcı devresini diğer devre bloklarından izole etmektedir. Büyük işaret pompalama akımı karıştırıcı içerisinde sadece yerel olarak oluşmaktadır. Bu özellikle, büyük ölçekli tümleştirilmiş karışık işaretli tümdevreler için büyük fayda sağlamaktadır.

Önerilen yeni yapının açıklanması Bölüm 3'de yapılmıştır. Devre üzerinde detaylı bir analiz yapılmış ve uygun kutuplama koşulları gösterilmiştir. Kutuplama koşullarının devre performansı üzerindeki etkisi analitik sonuçlarla gösterilmiştir. Gerçekleştirilen büyük işaret analizinden, baskın sıklık bileşeni yerel osilatör sıklığının iki katı olan pompalama akımı ve beslemeden çekilen toplam sabit akımın pompalama akımından geriye kalan kısmı olan fark akımı için denklemler çıkartılmıştır. Bu akımların ilgili harmonik bileşenlerinin DC kutuplama koşullarına ve yerel osilatör genliğine bağlı olarak değişimi gösterilmiştir. Verilen bir yerel osilatör genliği için en uygun kutuplama koşullarının nasıl bulunacağı grafikler üzerinde gösterilmiştir.

Açıklamaları yapılan devre şemaları kurulmuş ve çeşitli test düzenekleri için benzetimleri yapılmıştır. Yapı bloklarının ayrı ayrı benzetim sonuçları ve blokların birleştirilmiş hallerinin benzetim sonuçları Bölüm 4'de verilmiştir. LNA ve IF kuvvetlendiriciye ait benzetimler ayrı ayrı gerçekleştirilerek bu blokların performansları incelenmiştir. Önerilen ikinci harmonik karıştırıcı devresine ait benzetimler ise hem devre performansını incelemek hem de Bölüm 3'de verilen analiz sonuçlarını doğrulamak amacıyla gerçekleştirilmiştir. Karıştırıcı devresi performansı ile ilgili olarak Bölüm 3'de verilen analiz sonuçlarına benzer sonuçlar elde edildiği gözlenmiştir. Analizlerde kullanılan aynı kutuplama koşulları kullanılarak pompalama akımı ve fark akımının grafikleri elde edilmiştir. Tüm alıcı devresine ait benzetim sonuçları da Bölüm 4'de verilmiştir.

Tasarımı yapılan alıcı devresinin gerçeklenmesi Bölüm 5'de anlatılmıştır. Tüm alıcı devresinin serimi ve yapı bloklarının ayrı ayrı serimleri oluşturularak çok projeli pul (MPW) üretimi için hazırlanmıştır. MPW üretim şekilnin önceden belirlenmiş 5 mm $\times$ 5 mm tümdevre alınına uygun şekilde çeşitli serimler test amacıyla hazırlanmış ve yerleştirilmiştir. Hazırlanan serimler Bölüm 5'de gösterilmektedir.

Bölüm 6'da, ürettirilen tümdevrenin ölçülmesi için hazırlanan test düzenekleri ve test ortamı anlatılmış ve elde edilen ölçüm sonuçları verilmiştir. Üretilen test tümdevresindeki iki farklı test yapısını ölçmek için iki farklı baskılı devre (PCB) tasarlanmıştır. İlk PCB'de gerçekleştirilen ölçümler, çalışmada asıl katkı sağlanan karıştırıcı devresinin test edilmesi için kullanılmıştır. Karıştırıcının dönüştürme kazancı grafiği verilmiş ve önerilen yapının DC dengesizlik gerlimi sorunu üzerindeki etkisini göstermek amacıyla ölçümler yapılmıştır. İkinci PCB ise LNA, karıştırıcı ve IF kuvvetlendiricisinden oluşan tüm alıcı devresinin dönüştürme kazancının ölçülmesinde kullanılmıştır. Elde edilen sonuçlar benzetim sonuçlarıyla karşılaştırılarak uyumlulukları gösterilmiştir.

Çalışmadan elde edilen sonuçlar Bölüm 7'da özetlenmiştir.

#### 1. INTRODUCTION

In todays world, electronic devices using wireless communication increase in enormous numbers and varieties. In conjunction with the recent developments and the new capabilities of the semiconductor industry, the evolution of the communication systems is accelerated exponentially. The variety of new application areas are arisen and started to be used widely in our daily lives.

The fast pace evolution of the wireless systems escalate the expectations on the transceivers. Transceivers shall present excellent performance while satisfying financial concerns of the market. Especially, the consumer electronic market in the recent years has turned into an arena where worldwide manufacturers strive to lead the relevant technology to survive. The mobile devices include several types of communication applications with different frequency bands and operate them simultaneously. It is crucial to provide advanced services including different communication protocols for these devices with limited resources. Due to the limited resources of the mobile devices, the power consumption specifications gain great importance. Along with the technical difficulties and limitations, the massive pressure of the market brings the price and the time to market parameters as merits of the success of a transceiver. The requirement of low price and short time to market leads the designers to simple, compact and more integrated solutions [1,2].

Different types of transceivers exist, each having individual advantages and disadvantages. According to the requirements of the application area, generally, a specific type of transceiver is preferred. Depending on the number of steps they use to perform frequency conversion, transceivers are separated into two main categories; Heterodyne and Homodyne. Heterodyne architectures perform the frequency conversion in two steps while the Homodyne architectures accomplish in one step. Mainly, Heterodyne architectures have more complex structures but have some advantages over Homodyne transceivers. In spite of their complex structures, they are widely preferred in many applications just to stay away from the serious

problems of the Homodyne transceivers. On the other hand, Homodyne architectures have the advantage of being simple in structure. Nevertheless, their problems are to be solved to benefit its simplicity [1,2]. The two main types of transceivers, Heterodyne and Homodyne transceivers, are summarized with their problems in Chapter 2.

#### **1.1 Purpose of Thesis**

In this study, a simple and integrated receiver topology is aimed to be designed. Thus, the Homodyne architecture is selected to be realized. The simplicity of the architecture is used to get a compact and integrated receiver solution. The problems of the architecture are handled by utilizing the advantages of the subharmonic mixing technique and the Silicon-Germanium (SiGe) technology.

In subharmonic mixing technique, the fundamental mixing product at the output of the mixer is suppressed and another product regarding a harmonic of the pumping signal is taken as output. Generally, the second harmonic product is preferred and the mixing is called the second harmonic mixing in this case. Utilizing the second harmonic mixing technique brings some remarkable solutions to some of the problems of Homodyne architectures. The details of the subharmonic mixing technique is given in Section 1.4.

For the implementation of the proposed receiver, SiGe technology is used which is a rising technology for radio frequency integrated circuits (RFIC) due to its high performance components. Another main advantage of the SiGe technology is being easily available and being suitable for integration. The SiGe technology is explained briefly in Section 1.5.

By utilizing the proper techniques with the proper technology, it is aimed to develop an integrated Homodyne receiver topology which has adequate solutions to the well known problems. A novel second harmonic mixer topology is proposed and the circuit analysis is performed on it. The theoretical results and the detailed description of the proposed mixer are given in Section 3.2.

#### **1.2 Literature Review**

To clarify the technical problem, the literature is reviewed for the transceiver architectures and their problems. In [3–6], the general transceiver topologies and

their well known problems are detailed. Wide band operation of the transceivers is touched in [7]. Since the aim of the study is to propose an appropriate Zero-IF topology for integration, [8–11] are investigated to understand the difficulties in integrating the overall structure. The effectiveness of the Zero-IF topology for the integrability and for providing compact solutions is explained in [2]. Regarding the solutions to the problems of the Zero-IF transceivers, [12] propose adaptive filtering technique for I/Q imbalance compensation and [13–17] includes some advance tuning techniques for second order intermodulation distortion. Recent works [8, 18–24] on Zero-IF transceivers show the state of the art.

SiGe BiCMOS semiconductor processing technology is selected to be utilized for the Zero-IF receiver integrated circuit. The references [25–28] show the capabilities of the SiGe technology. It is noted that the SiGe technology is a suitable choice for high integration RFICs. The available devices and the performance limits of the HBTs are shown in the given references.

Subharmonic mixing technique is one of the key components of the study, since it is used to overcome most of the problems of the Zero-IF topology. In [29], it is shown how second harmonic mixing is realized with an anti-parallel diode pair. It is also shown in [29] that the phase noise of the local oscillator signal is not converted, since a virtual local oscillator (LO) signal of which frequency is two times the actual LO signal is used for mixing. Recent implementation of subharmonic mixing in Zero-IF topologies are given in [2, 18-20, 20, 23, 30-43]. The references [20, 30, 35–38, 41, 43] introduce some subharmonic mixers designed in CMOS technology while the implementations given in [23, 32–34, 40, 42] utilize the advantages of SiGe BiCMOS technology. In the given references, the subharmonic mixers are designed for Zero-IF applications to provide integrated solutions. Investigated references as the embodiments of the subharmonic mixers in different technologies are compared with the proposed mixer topology in this study in Chapter 7. The design concerns for different applications are investigated from these references. In [44], a low-IF solution is proposed to use the advantages of Zero-IF receivers without dealing with its difficulties. There are works done in [45–48] for MESFET mixers and distributed MESFET mixers and nonlinear analysis of them.

The most effective problem of Zero-IF transceivers, DC offset voltage is investigated in [49–53]. These references propose some techniques to overcome the problem and give some results regarding the effectiveness of the techniques. The references [54–56] propose some techniques against LO pulling problem and the reference [49] considers second order intermodulation distortion together with the DC offset problem. The IQ mismatch problem and related solutions are given in [57, 58]. In [59], a single chip Zero-IF CMOS implementation is proposed using one-third frequency LO.

For the design of wide band LNA, the reference [60–62] are used. The proposed circuits show the state of the art. The LNA implementations given in [60, 62] use the CMOS technology. The reference [63] is an SiGe implementation which is an integrated front-end solution for transceivers. In [64], a bias feed circuit is proposed for a SiGe LNA implementation. The IF amplifier topologies are also searched and recent works are studied. In [65, 66], recent topologies for the IF amplifier are shown. In the design of LNA and IF amplifier, [3, 5, 6, 67, 68] are also used.

#### **1.3 Contributions**

The aim of the study is to develop an integrated Zero-IF receiver topology for compact and dense applications. To achieve this goal, the proper components are combined together. One is utilizing the second harmonic mixing technique which provides some fundamental solutions to the problems of the Zero-IF transceivers naturally. The main cause of the well known problems of the Zero-IF transceivers is the equality of the LO frequency and the carrier frequency. By using second harmonic mixing technique, this equality is broken since the half of the carrier frequency is used as the LO frequency instead. The advantages brought by the second harmonic mixing technique is explained in details in Section 1.4.

Other important component utilized to get an integrated Zero-IF receiver topology is SiGe BiCMOS processing technology. SiGe is an emerging technology for the RFIC applications. Since it is developed from the advanced techniques obtained in well known Si process, it is easily accessible and affordable. Providing the complementary metal oxide semiconductor (CMOS) transistors together with the high speed SiGe heterojuntion bipolar transistors (HBT) and other analog circuit components, the SiGe technology constitutes a proper environment for the integration of complex high speed designs.

Along with combining the proper techniques and technology, the development of individual building block topologies is carried out purposefully according to the problems of the Zero-IF transceivers. A wide RF range is targeted to construct a general receiver structure covering the frequency bands of variety of applications. Besides obtaining the area and cost efficient topology, it is also intended to provide a single solution for different types of applications.

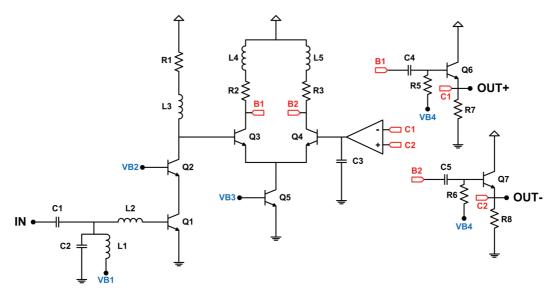

The main contribution is made on the mixer of the receiver topology. A novel second harmonically pumped Zero-IF mixer topology is proposed. Although the DC offset problem is treated by using second harmonic mixing technique, there still may be DC offset voltage at the output due to the leakage of the second harmonic of the LO signal to the RF signal path. Especially, when both the LNA and the mixer are integrated on the same chip, the leakage to the input of LNA through the substrate may cause considerable DC offset voltage. The proposed topology contains a unique mechanism to cancel the DC offset voltage at the output.

Due to the unique mechanism, a constant total DC current flows through the overall mixer circuit. First, the constant DC current is split into two and the pumping current containing the proper frequency components is obtained. After performing the mixing, the split pumping current and the residue current is combined again to form the constant DC current. Thus, the total current drawn from the supply lines is kept constant. Thanks to this attribute of the proposed mixer topology, the noisy large signal mixing operation take place locally in the mixer circuit and it is isolated from the supply and ground lines from which generally the leakage to the other circuit components occur.

In the proposed mixer topology, the leakage of the second harmonic of the LO signal to the RF input is also suppressed. Although the overall current of the mixer is kept constant, the RF input signal conducts to the transistors on which the pumping current flows. To prevent the leakage of the second harmonic of the LO signal to the RF input through the input transistors, the RF input transistors are replicated and the residue current containing the opposite frequency components is flown through these transistors. By also considering the symmetry, the overall leakage to the RF input of the mixer is also suppressed. The details of the DC offset cancellation mechanism is explained in Section 3.2.

Along with providing a new second harmonic mixer topology with conceptually new mechanism for DC offset voltage cancellation, the circuit analysis of the topology is performed for the SiGe techology. The proper biasing conditions for appropriate mixing is determined. The effects of the biasing conditions on the linearity and the efficiency of the circuit is investigated and approved with analytical results.

#### 1.4 Subharmonic Mixing Technique

Mixers widely preferred in different types of transceivers generally use fundamental mixing. In fundamental mixing technique, the upconverted or the downconverted output signal is selected as the fundamental product of the multiplication of two inputs. When the Fourier series expansion is investigated, it is seen that the fundamental term of the mixing products has the greatest coefficient among others. Thus, the fundamental mixing is widely used basically to maximize the conversion gain of the mixer. Although the conversion gain is maximized in fundamental mixing technique, some disadvantages come along with it [3–5].

Maximizing the conversion gain at the mixer decreases the effect of the noise of the following stages to the signal. However, strict restrictions are brought to the design specs of the oscillator. When the fundamental mixing technique is used in Zero-IF reception, the phase noise of the oscillator is directly converted into the signal band [3, 29]. Since, the oscillator frequency is needed to be equal to the carrier frequency, it gets more difficult to design such an oscillator. Thus, the phase noise performance of the oscillator gains great importance in the overall system performance. To design a low phase noise oscillator, it is required to have circuit components with high quality factors which is a difficult requirement to be satisfied in integrated circuits. Therefore, low phase noise oscillators are not suitable for integration so that they are implemented with discrete components.

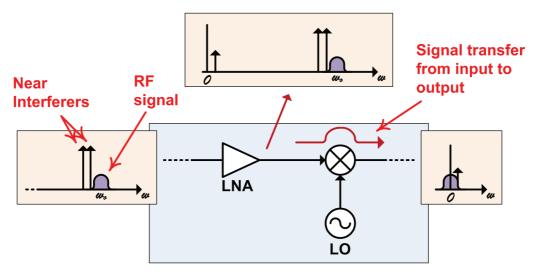

In subharmonic mixing technique, an harmonic component of the mixing products, generally the second harmonic, is selected to be the converted output [29]. The

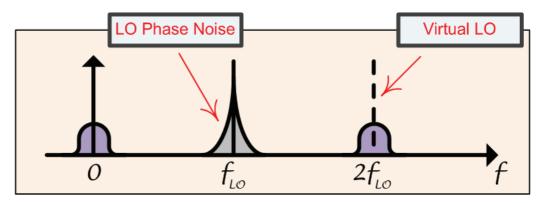

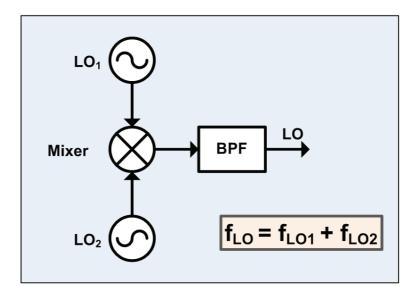

Figure 1.1 : The conversion mechanism of the second harmonic mixing technique when used in Zero-IF mixers.

fundamental mixing product is suppressed at the output. Although the harmonic component of the mixing product has a lower Fourier coefficient than the fundamental product, selecting the harmonic component as the mixing result provides some advantages. Since the fundamental mixing product is suppressed at the output, in this type of mixing the phase noise of the oscillator is not converted into the signal band [29]. The natural elimination of the phase noise of the oscillator from the signal band relieves the design specs on the oscillator in great extend. It can even be possible to integrate the oscillator together with other circuit blocks.

When second harmonic mixing technique is used in Zero-IF transceivers, it reveals even greater advantages for this specific situation. In a Zero-IF transceiver using the second harmonic mixing technique the LO frequency is arranged to be the half of the carrier frequency. Since the most severe problems specific to Zero-IF transceivers grow out from the equality of the LO frequency and carrier frequency, second harmonic mixing technique arises as an fundamental solution to these problems. The conversion mechanism of second harmonic mixing technique when used in Zero-IF mixers is shown in Figure 1.1 [29]. Here, it is shown that the RF signal band is downconverted to the base band by a virtual LO signal of which frequency is  $f_{2LO} = 2 \times f_{LO}$ , thus the phase noise spectrum around  $f_{LO}$  is not converted into baseband.

#### 1.5 SiGe Technology

SiGe is a rapidly developing semiconductor technology which has great use in high frequency microelectronics. The advantages it brought help designers to solve many

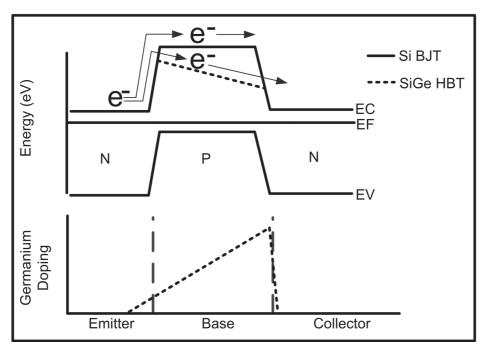

Figure 1.2 : Energy band diagram and Ge doping profile of a SiGe HBT.

problems of RF applications. Since it has evolved from the well known and widely used CMOS technology, the use of readily developed infrastructure and knowledge of CMOS technology makes SiGe technology low cost and easily accessible. Being low cost and easily accessible, SiGe technology finds place in many RF applications [25–27].

SiGe technology involves Germanium (Ge) doping into the standard Silicon (Si) substrate. As shown in Figure 1.2, the Ge doping in the base of the transistor changes in a linear fashion and bends the energy band diagram respectively. This bending of the energy band diagram creates an internal electrical field which increases the velocity of the electrons passing the base region [27, 28]. Thanks to this mechanism, very high speed transistors are obtained in SiGe technology. The high speed transistor obtained by Ge doping in the base region is called Heterojunction Bipolar Transistor (HBT). These transistors have also the advantages of being low noise and having high breakdown voltage.

## 2. TRANSCEIVER TOPOLOGIES

Two main transceiver topologies, Heterodyne and Homodyne, are summarized in this Chapter. Advantages and drawbacks of the both architectures are exposed. The problems of the Homodyne transceivers are explained in details and some techniques from the current literature used to solve these problems are given. Since the Homodyne transceiver architecture is the one to be used in this study, the reasons and the possible solutions to this kind of transceivers are given to present the technical problem clearly.

#### 2.1 Transceiver Topologies

In the current literature, there are various transceiver topologies in use, all having different advantages and disadvantages. In transceiver circuits, the topology to be used is selected according to the application area and the frequency range. Due to the challenging required specifications of the communication standards and the difficulties of the high frequency electronic design, different topologies optimized for each specific application are generally used. Necessity of high order filters, passive circuit elements with high quality factors, low jitter oscillators and impedance matching in high frequency electronics prevents the integration of the whole transceiver topology on a single chip [3–5]. The required passive components with high quality factors, high order filters and low jitters oscillators are implemented with discrete components.

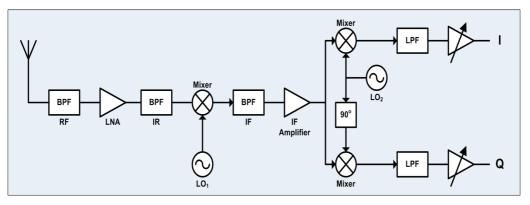

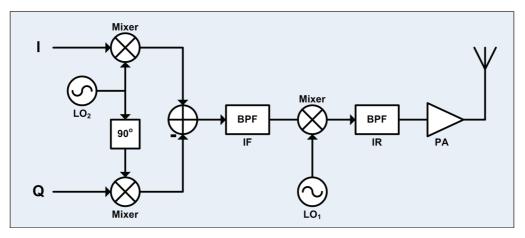

Transceiver topologies are categorized in two main types of architectures; heterodyne and homodyne [3]. Heterodyne architecture performs the frequency conversion between the radio frequency (RF) and the baseband in two steps by using an intermediate frequency (IF). This architecture comes along with a well known image problem [3]. Thus, the transceivers implemented in this architecture include additional filters to suppress the image frequency. Including two conversion steps and additional filters increase the architectures complexity, yet it is a widely preferred architecture in many applications due to its advantages [4, 7]. However, the complex structure of the heterodyne architecture makes this type of transceivers difficult to integrate on a

Figure 2.1 : Block diagram of the receiver part of the heterodyne transceivers.

Figure 2.2 : Block diagram of the transmitter part of the heterodyne transceivers.

single chip. Block diagram of the heterodyne transceivers is shown in Figure 2.1 and Figure 2.2 [3].

Homodyne transceivers on the other hand, performs the frequency conversion in one step. This type of transceivers are also known as direct conversion transceivers or Zero-IF transceivers. The frequency conversion in one step prevents the image problem and the additional filters used to filter out the image frequency is omitted in these transceivers [3, 4, 6]. The number of mixers, local oscillators (LO) and amplifiers are also decreased because of the single step conversion. This architecture has a more simple structure when compared to heterodyne transceivers. The simplicity of the architecture makes this type of transceivers more suitable for integration on a single chip. However, simplicity and being suitable for integration brings some other serious problems; DC offset voltage, I/Q mismatch and Flicker noise [3,4]. These problems of the homodyne transceivers is shown in Figure 2.3 and Figure 2.4.

Figure 2.3 : Block diagram of the receiver part of the homodyne transceivers.

Figure 2.4 : Block diagram of the transmitter part of the homodyne transceivers.

### 2.2 Problems of Homodyne Transceivers

Homodyne Transceivers, also known as Zero-IF transceivers, has a simple structure with fewer building blocks when compared to heterodyne counterparts because the frequency conversion occurs in only one step. Beside this basic advantage, since the LO frequency is equal to the carrier frequency in Zero-IF transceivers, the image problem does not occur in this type of transceivers [3]. Thus, the image reject (IR) filter is omitted. Omitting the IR filter also simplifies the design of the low noise amplifier

(LNA) in the structure, since the output of the LNA is not needed to be matched to an 50  $\Omega$  discrete filter [3].

Channel selection in Zero-IF transceivers is made by lowpass filter (LPF) in the baseband. Since this filter operates in low frequency region, it is suitable to be realized as an on-chip active filter. All the components including this LPF except the high frequency bandpass filter (BPF) and the power amplifier (PA) at the transmitter output can be integrated on a single chip. The suitability to integration of the Zero-IF transceiver topology is depicted as being promising in various works [2, 44].

# 2.2.1 DC Offset Voltage

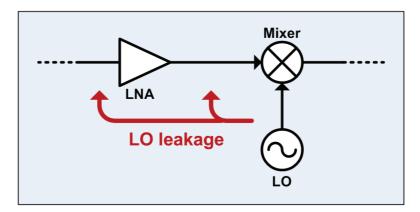

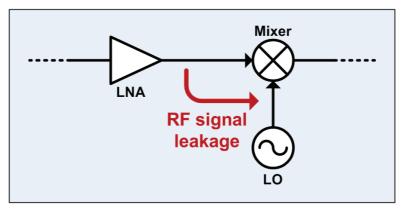

One of the most important problems of the Zero-IF transceivers is the DC offset voltage occurring at the output of the receiver. This problem appears in only Zero-IF transceivers because of the equality of the LO frequency and the carrier frequency. There are two mechanisms to be investigated as a reason of this problem. These mechanisms are shown in Figure 2.5 and Figure 2.6 [3].

In the first mechanism which is shown in Figure 2.5, the LO signal leaks to the RF path and it is downconverted in the mixer by the LO signal itself [3, 50, 69]. This results in a DC offset voltage at the mixer output. Especially the leakage to the input of the LNA may result in a greater problem since the leaked signal is amplified along with the RF signal in the LNA.

The other mechanism of the DC offset voltage problem is the RF signal leakage to the LO port of the mixer as shown in Figure 2.6. The leaked RF signal mixes itself in the mixer resulting in a varying DC offset voltage at the output of the receiver [3, 50, 69]. This mechanism is less severe according to the LO leakage mechanism since the RF signal has less power compared to LO signal even after being amplified in the LNA.

In the literature, there are some precautions proposed to solve the DC offset voltage problem. One of them is using a high pass filter (HPF) at the output [3]. This can be applied only if a suitable modulation technique removing the data close to DC is applied. Otherwise, applying a HPF results in data loss near DC. Even when the data is removed from vicinity of the DC with a suitable modulation technique, a HPF with a very low cutoff frequency is needed. To realize a very low cutoff frequency,

Figure 2.5 : DC offset voltage due to LO leakage mechanism.

Figure 2.6 : DC offset voltage due to RF leakage mechanism.

a huge capacitor is needed to be used which is only possible with usage of discrete components. Using a HPF with a very low cutoff frequency has another drawback that is insufficient filtering of the DC offset voltage [3].

As it is not feasible to filter out the DC offset voltage at the output in Zero-IF receivers, more complex solutions involving digital and analog signal processing techniques are proposed [58, 69, 70]. These techniques rely on the fact that the DC offset voltage has a very low dependency on time. The DC offset voltage of system is characterized during idle time and then the DC offset voltage when it is functional is predicted [3]. Examples of some other techniques introduced in the literature are given in [49–53,58].

Designing a fully symmetrical transceiver is also used as a precaution to this problem. It is tried to make the symmetrical paths to be effected equally form the leakages and other reasons of DC offset voltage problem. The relevant isolations in the circuit should also be considered to minimize the leakages.

#### 2.2.2 I/Q Mismatch

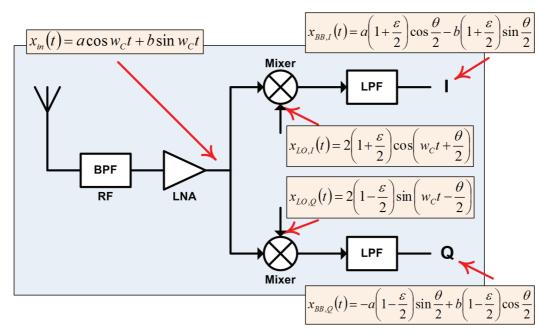

Figure 2.7 : IQ mismatch mechanism on Zero-IF mixers.

In Zero-IF transceivers, the LO frequency is equal to the carrier frequency. Thus, when the RF signal is downconverted, left and right sidebands overlap. This does not cause a problem in the modulation techniques like amplitude modulation (AM) since the left and the right sidebands carry the same information. However, in the modulation techniques like frequency modulation (FM) and phase modulation (PM) where the left and the right sidebands carry different information, the Zero-IF transceiver should produce quadrature outputs [3]. These quadrature outputs, I and Q, are produced as shown in Figure 2.3. Two equivalent paths are used for both outputs and the mixers are driven with 90° out of phase LO signals. Following two different paths after LNA, the RF signal may be subject to different gain and phase errors [3]. Similarly, the 90° out of phase LO signals may also come under different errors. This mismatch between two paths of the quadrature outputs may cause improper separation of I and Q parts of the RF signal and one output may disturb the other [3]. In Figure 2.7, the IQ mismatch mechanism in Zero-IF mixers is shown.

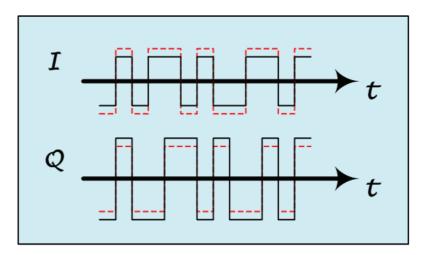

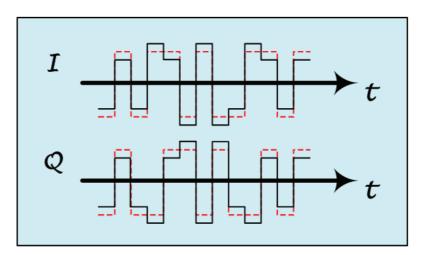

Here,  $\varepsilon$  is the gain error and the  $\theta$  is the phase error between the LO signals applied to two symmetrical paths. The resultant effects of the gain error and the phase error are shown separately in Figure 2.8 and Figure 2.9 respectively.

I/Q mismatch problem has a greater possibility to occur in discrete implementations where it is harder to make the both paths symmetrical enough. To prevent this problem,

Figure 2.8 : Gain error between I and Q outputs of the Zero-IF mixer.

Figure 2.9 : Phase error between I and Q outputs of the Zero-IF mixer.

implementing the two paths on a single integrated circuit helps in great extend. Since I/Q mismatch varies slightly with time, various post processing techniques may also be used to recover the signals [12, 57, 58]. However, these techniques increase the complexity of the circuit.

## 2.2.3 Even Order Distortion

Even Order Distortion is another issue to be solved in Zero-IF transceivers which is caused due to the equality of the LO frequency and the carrier frequency. An ideal mixer outputs only the products of the multiplication of its two inputs. In actual realizations, the signals at the inputs themselves are also transferred to the output with some loss. Because of the nonlinear behavior of the LNA and the RF input of the mixer, any two interferer signals close to the RF signal band may cause unwanted low frequency components at the RF input of the mixer [13–17]. These unwanted

Figure 2.10 : The effect of even order distortion at the input of the Zero-IF receiver.

low frequency products of the even order distortion at the input are then transferred to the output with some loss by the mixer. They reside in the baseband where the desired actual signal exists [3]. Thus, these unwanted outcomes of the interferer signals cannot be eliminated by the LPF at the output. The effect of even order distortion on Zero-IF transceivers is shown in Figure 2.10.

# 2.2.4 Flicker Noise

In Zero-IF receivers, the Flicker Noise of the stages following the mixer is added directly to the signal band since the RF signal is converted directly to baseband in the mixer. Thus, the Flicker Noise of the stages following the mixer along with the gain of the LNA and the conversion gain of the Mixer become important.

This problem arises mostly in CMOS implementations. Using a technology like SiGe where the transistors are low noise devices relieves the problem. The precautions taken for the DC offset voltage problem also help decreasing the Flicker Noise since it is dominant near DC [3,70].

## 2.2.5 LO Leakage

The radiation of the LO leakage via the antenna causes interfering signal to the other receivers. Since the LO frequency is equal to the carrier frequency, the LO leakage problem may cause considerable disturbance in Zero-IF receivers. The on-chip implementation of the local oscillator decreases this problem since the most important

**Figure 2.11** : Producing the actual LO signal from two different LO signal with different frequencies.

source of LO radiation is the bonding wires. As described in Section 1.4, using second harmonic mixing technique brings a fundamental solution to this problem even when the oscillator is implemented outside the chip [3].

# 2.2.6 LO Pulling

In Zero-IF transmitters, there exist a high power RF signal at the output of the PA. Since the frequency of this RF signal is equal to the LO signal, it may cause the output frequency of the voltage controlled local oscillator to change [3, 56]. This effect is called the LO pulling. To solve this problem, a technique which is shown in Figure 2.11 by producing the actual LO signal on-chip by mixing two external LO signals with different frequencies can be applied [3]. In [59], a single chip Zero-IF CMOS implementation is proposed using one-third frequency LO. Some other techniques to LO pulling resistant transmitters are introduced in [54–56].

Using second harmonic mixing technique as explained in Section 1.4 also helps to prevent the LO pulling problem of the Zero-IF transceivers. Since the LO frequency is the half of the carrier frequency, the high power RF signal at the PA output cannot change the frequency of the LO.

## 3. THEORY OF THE PROPOSED CIRCUIT

In this section, the building blocks of the proposed second harmonic Zero-IF receiver topology; low noise amplifier (LNA), second harmonic mixer and IF amplifier are examined separately. For the LNA and IF amplifier, differential circuit topologies are selected to be realized. The design and the realization of these block are done considering that it is aimed to obtain a receiver topology which is integrated on a single chip. The design considerations and details of the selected topologies for the LNA and the IF amplifier are given in Section 3.1 and Section 3.3 respectively.

A new second harmonically pumped mixer topology is proposed. The topology is explained in details in Section 3.2. Circuit analysis of the proposed mixer is performed and the proper operating conditions for second harmonic mixing is exhibited. Also the main contribution made to the Zero-IF receiver topology in order to solve the DC offset voltage problem is explained in this section.

#### 3.1 Low Noise Amplifier (LNA)

As a front-end to the proposed Zero-IF receiver topology a wide band LNA is designed. Selected topology is a differential two stage amplifier. It is designed to operate within a wide frequency range to satisfy a receiver which can be utilized in different applications. The selected LNA topology is explained in details in Section 3.1.1.

#### 3.1.1 LNA Topology

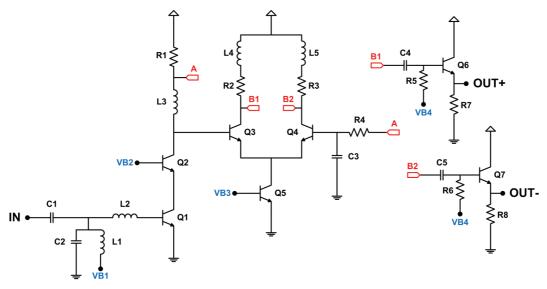

The LNA circuit schematic designed for the Zero-IF receiver is shown in Figure 3.1. For simplicity in the circuit schematic, some connections are shown with labeling. The nodes with same labels should be considered connected. The selected topology is suitable for wide band operations and it has single ended input and differential outputs. The LNA circuit is designed to operate within a wide range of 2-10 GHz. it consists of two gain stages and an emitter follower stage. The input matching of the circuit is achieved by the passive components, C1, C2, L1 and L2. L1 is also used to supply

Figure 3.1 : LNA circuit schematic.

the input biasing voltage VB1 which is generated internally. The first gain stage is a common emitter cascode gain stage consisting of Q1 and Q2 transistors. The passive components L3 and R1 compose the load impedance of the first gain stage.

The second gain stage of the LNA is a differential pair stage composed of Q3 and Q4 transistors as the identical pair and the Q5 transistor as the biasing current source. Q5 transistor is biased with a constant voltage VB3 which is also generated internally. The load impedance of the differential pair consists of R2, R3, L4 and L5 components. The passive components on both sides of the differential pair is taken identical. L4 and L5 inductors are implemented as a center tapped single symmetrical inductor. Besides supplying gain in the signal path, the main purpose of this second gain stage to convert the single ended RF signal to a balanced differential signal. To achieve this purpose, signal ended RF signal coming out from the first gain stage is applied to one input of the differential pair, to the base of transistor Q3, and the other input of the differential pair, the base of transistor Q4, is biased with the DC voltage level of the same RF signal. A low pass filter consisting of R4 and C3 is used to obtain the DC voltage level of the RF signal.