# $\frac{\text{ISTANBUL TECHNICAL UNIVERSITY} \star \text{GRADUATE SCHOOL OF SCIENCE}}{\text{ENGINEERING AND TECHNOLOGY}}$

#### LAYOUT TECHNIQUES FOR ANALOG BUILDING BLOCKS AND APPLICATION TO AN ADAPTIVE OUTPUT BUCK CONVERTER

#### M.Sc. THESIS

Faik Mevlut DURMAZ

**Department of Electronics and Communications Engineering**

**Electronic Engineering Programme**

# ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL OF SCIENCE ENGINEERING AND TECHNOLOGY

# LAYOUT TECHNIQUES FOR ANALOG BUILDING BLOCKS AND APPLICATION TO AN ADAPTIVE OUTPUT BUCK CONVERTER

M.Sc. THESIS

Faik Mevlut DURMAZ (504111244)

**Department of Electronics and Communications Engineering**

**Electronics Engineering Programme**

Thesis Advisor: Assoc. Prof. Dr. Metin YAZGI

### <u>İSTANBUL TEKNİK ÜNİVERSİTESİ</u> ★ FEN BİLİMLERİ ENSTİTÜSÜ

## ANALOG SERIM TEKNIKLERI VE UYARLANABILEN CIKIS ALCALTICI DONUSTURUCUYE UYGULANMASI

YÜKSEK LİSANS TEZİ

Faik Mevlut DURMAZ (504111244)

Elektronik ve Haberlesme Muhendisligi Anabilim Dali Elektronik Muhendisligi Programi

Tez Danışmanı: Doc. Dr. Metin YAZGI

Faik Mevlut DURMAZ, a M.Sc. student of ITU Graduate School of Science Engineering and Technology 504111244 successfully defended the thesis entitled "Layout Techniques For Analog Building Blocks And Application To An Adaptive Output Buck Converter", which he/she prepared after fulfilling the requiremnts specified in the associated legistlations, before the jury whose signatures are below.

| Thesis Advisor : | <b>Doç. Dr. Metin YAZGI</b> Istanbul Technical University           |  |

|------------------|---------------------------------------------------------------------|--|

| Jury Members :   | Yrd. Doç. Dr. Mustafa Berke Yelten<br>Istanbul Technical University |  |

|                  | <b>Yrd. Doç. Dr. Okan Zafer Batur</b><br>Bilgi University           |  |

Date of Submission : 02 May 2016 Date of Defense : 08 June 2016

To my wife, family and friends

#### **FOREWORD**

This thesis cannot be finished without endless support and encouragement of my beloved wife, Gizem. She endured all my misery and gave hope at all times.

My family, mother, grandmother and grandfather, I thank you all. You made me what I am now.

Grateful thanks to my thesis professor, Doc. Dr. Metin YAZGI. And gratest advisor of this thesis Kemal OZANOGLU.

Thanks to Yrd. Doç. Dr. Mustafa Berke Yelten and Yrd. Doç. Dr. Okan Zafer Batur for serving in my committee.

Thank you to Arda AKKAYA, Atilim ERGUL and Ahmet Mert OZDEMIR, my friends, they are great people.

A very special thanks to my professor, elder brother, mentor, ex-colleague Dr.Bortecene TERLEMEZ who is always with me.

May 2016

Faik Mevlut DURMAZ

### TABLE OF CONTENTS

|                                                        | <b>Page</b> |

|--------------------------------------------------------|-------------|

| FOREWORD                                               | iv          |

| TABLE OF CONTENTS.                                     |             |

| ABBREVIATIONS                                          |             |

| LIST OF SYMBOLS                                        |             |

| LIST OF TABLES                                         |             |

| LIST OF FIGURES                                        |             |

| SUMMARY                                                |             |

| ÖZET                                                   |             |

| 1. INTRODUCTION                                        |             |

| 1.1 Organisation of Thesis                             |             |

| 1.2 The Purpose of Thesis                              |             |

| 2. MANUFACTURING OF A MOSFET                           |             |

| 2.1 Fabrication                                        |             |

| 2.2 CMOS Fabrication Process                           |             |

| 3. BASIC LAYOUT STRUCTURES                             |             |

| 3.1 CMOS Layout Structure                              | 9           |

| 3.2 PN Diode Layout                                    |             |

| 3.3 BJT Layout                                         |             |

| 3.4 Resistor Layout                                    |             |

| 3.5 Capacitor Layout                                   |             |

| 3.5.1 MOS capacitor                                    |             |

| 3.5.2 MIM capacitor layout                             |             |

| 3.5.3 Metal - on - metal (MOM) capacitor layout        |             |

| 3.6 Electromigration                                   |             |

| 3.7 Electromigration Dependency On Physical Effects    | 18          |

| 3.7.1 Temperature                                      |             |

| 3.7.2 Wire width and current density                   |             |

| 3.7.3 Wire length                                      |             |

| 3.8 IR Drop                                            |             |

| 4. ISOLATION SCHEMES                                   | 23          |

| 4.1 Isolation of Device in Fabrication Process         | 23          |

| 4.1.1 Local oxidation of silicon (LOCOS)               | 23          |

| 4.1.2 Shallow trench isolation                         |             |

| 4.2 Isolation in Layout                                | 26          |

| 4.2.1 Disturbance from minority carrier                | 26          |

| 4.2.2 Substrate coupling noise                         |             |

| 4.2.3 Guard rings                                      |             |

| 4.2.3.1 Nwell guard ring                               | 28          |

| 4.2.3.2 Ptap guard ring                                |             |

| 4.2.3.3 Double guard ring concept                      |             |

| 4.2.4 Deep n-well structure                            | 31          |

| 4.2.5 Deep trench isolation                            |             |

| 4.2.6 NT_N (native) layer (as known as moat isolation) |             |

| 5. ISSUES RELATING LAYOUT                              | 37          |

| 5.1 Latch-up                                           | 37          |

| 5.2 Well Proximity Effect (WPE)                        | 40          |

| 5.3 STI Proximity Effect/Length of Diffusion (LOD)                                  | 41         |

|-------------------------------------------------------------------------------------|------------|

| 5.4 Antenna Effect                                                                  | 43         |

| 6. MATCHING IN LAYOUT                                                               | 45         |

| 6.1 Matching Techniques in Layout                                                   | 47         |

| 6.2 Orientation of Devices                                                          |            |

| 6.3 Placement (Location) of Devices                                                 | 48         |

| 6.4 Unit Size Device Usage                                                          | 49         |

| 6.5 Dummy Device Usage                                                              | 51         |

| 6.6 Routing Symmetry                                                                | 52         |

| 6.7 Symmetrical Placement                                                           | 52         |

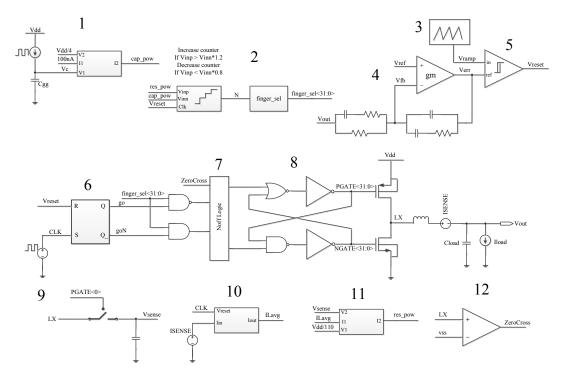

| 7. LAYOUTS OF ADAPTIVE OUTPUT BUCK CONVERTER                                        | R BLOCKS55 |

| 7.1 Adaptive Capacitive G <sub>m</sub> and Adaptive Resistive G <sub>m</sub> blocks | 56         |

| 7.2 Error Amplifier Block                                                           | 65         |

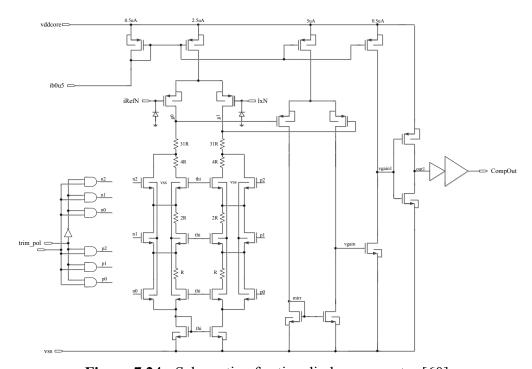

| 7.3 PWM Comparator                                                                  | 68         |

| 7.4 Ramp Generator                                                                  | 72         |

| 7.5 vSense Sample and Hold Block                                                    | 76         |

| 7.6 Active Diode Comparator                                                         | 78         |

| 7.7 Pre-Driver and Driver                                                           | 82         |

| 7.8 Current Sense Block                                                             | 98         |

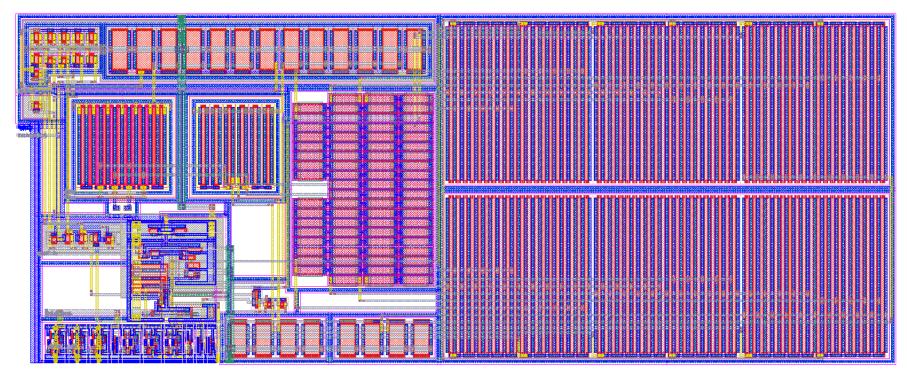

| 7.9 Buck Converter Layout                                                           |            |

| 8. ANALYSIS AND OPTIMIZATION OF METAL INTERCO                                       |            |

| LARGE-AREA POWER MOSFETs                                                            |            |

| 8.1 Physics of Current Flow in Interconnects                                        |            |

| 8.2 SPICE Lumped-Element Layout Modelling                                           |            |

| 8.3 R3D Resistive Extraction and Analysis                                           |            |

| 9. CONCLUSION AND FUTURE WORK                                                       |            |

| REFERENCES                                                                          |            |

| APPENDICES                                                                          | 135        |

| CHIDDICHI HM VITAE                                                                  | 151        |

#### **ABBREVIATIONS**

IC : Integrated Circuit

**CMOS** : Complementary Metal Oxide Semiconductor

**CAD** : Computer Aided Design

PMOS : P channel Metal Oxide Semiconductor NMOS : N channel Metal Oxide Semiconductor

**MOSFET** : Metal Oxide Semiconductor Field Effect Transistor

**MIMCAP** : Metal-Insulator-Metal Capacitor

**MOSCAP** : Metal Oxide Semiconductor Capacitor

MOMCAP : Metal On Metal CapacitorSTI : Shallow Trench IsolationLOCOS : Local Oxidization of Silicon

TOX : Thick Oxide FOX : Field Oxide

**R3D** : Resistive 3-Dimensional Extraction

RDL : Re-Distribution Layer

CBM : Capacitor Bottom Metal

CTM : Capacitor Top Metal

**RCX** : Resistive Capacitive Extraction

**SOI** : Silicon on Insulator

RHBD : Radiation Hardened by Design ELT : Enclosed Layout Transistor

#### LIST OF SYMBOLS

*J* : Current Density E : Electric field

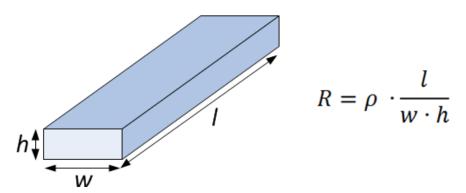

$\rho$  : Resistivity of material ( $\Omega$ m)

σ: Conductivity (S/m) μ

: Micron, 10<sup>-6</sup> meter

Ω : Ohm

V : Voltage

I : Current

I : length

w : width

h : height

$\begin{array}{lll} t_{ox} & : \mbox{ gate oxide thickness} \\ C_{ox} & : \mbox{ oxide capacitance} \\ V_{T} & : \mbox{ threshold voltage} \\ V_{BG} & : \mbox{ Bulk-gate voltage} \end{array}$

D : Drain

S : Source

B : Bulk

G : Gate

### LIST OF TABLES

|                                                                               | <b>Page</b> |

|-------------------------------------------------------------------------------|-------------|

| <b>Table 7.1:</b> Metal and contacts/via sheet resistance and current density | 88          |

| Table 8.1: Resistivity and Conductivity of materials                          | 100         |

### LIST OF FIGURES

|                                                                              | <b>Page</b> |

|------------------------------------------------------------------------------|-------------|

| Figure 2.1: Well formation stage.                                            | 5           |

| Figure 2.2 : Active and isolation stage.                                     |             |

| Figure 2.3: Gate oxide formation stage.                                      |             |

| Figure 2.4: Gate formation stage.                                            |             |

| Figure 2.5 : Source drain formation stage                                    |             |

| Figure 2.6: Shallow trench isolation.                                        |             |

| Figure 2.7: NMOS and PMOS layout cross-section.                              |             |

| Figure 2.8: Six masks that basically define an inverter.                     |             |

| Figure 3.1: PN diode structure.                                              |             |

| Figure 3.2: Top view and cross-section of BJT layout.                        |             |

|                                                                              |             |

| <b>Figure 3.3:</b> Resistor model (left), top-view (top) and layout (bottom) |             |

| Figure 3.4: MOSCAP layout cross-section.                                     |             |

| Figure 3.5 : Capacitive vs V <sub>BG</sub> .                                 |             |

| Figure 3.6: Cross-section of MIM capacitor                                   |             |

| Figure 3.7: MIM capacitor with CTM and CBM                                   |             |

| Figure 3.8: Another view of MIM capacitor                                    |             |

| Figure 3.9: MOM capacitor view                                               |             |

| Figure 3.10 : EM failure types                                               |             |

| Figure 3.11: Electromigration dependency on temperature                      |             |

| Figure 3.12: Illustrations of various diffusion processes                    |             |

| Figure 3.13: Reduced wire width                                              |             |

| Figure 3.14: IR drop in layout                                               |             |

| Figure 4.1: Bird's beak and its effect on device width                       |             |

| Figure 4.2: LOCOS formation                                                  |             |

| Figure 4.3 : STI formation                                                   |             |

| Figure 4.4: Substrate coupling noise                                         |             |

| Figure 4.5 : Guard ring path                                                 |             |

| Figure 4.6: Double guard ring for NMOS                                       | 30          |

| <b>Figure 4.7 :</b> Double guard ring for PMOS                               | 30          |

| Figure 4.8: Deep N-well CMOS inverter cross-section                          | 31          |

| Figure 4.9: Deep trench isolation                                            | 33          |

| Figure 4.10: Moat guard ring isolation                                       | 34          |

| Figure 5.1: Inverter cross-section showing NPN and PNP                       | 37          |

| Figure 5.2: Lateral NPN and vertical PNP                                     |             |

| Figure 5.3 : Scattering ions at the edge of Nwell region                     | 41          |

| Figure 5.4: Doping concentration of scattered ions                           |             |

| Figure 5.5 : SA and SB representation in MOSFET                              |             |

| Figure 5.6 : STI stress in cross-sectional view                              |             |

| <b>Figure 5.7 :</b> I <sub>d sat</sub> variation for an advanced process     |             |

| Figure 5.8: Antenna violation and jumper insertion                           |             |

| Figure 5.9: Diode insertion to prevent Antenna effect                        |             |

| Figure 6.1: Systematic mismatch behaviour representation                     |             |

| Figure 6.2: Random mismatch behaviour                                                            | 46                       |

|--------------------------------------------------------------------------------------------------|--------------------------|

| Figure 6.3 : Orientation of devices                                                              | 47                       |

| Figure 6.4: Temperature gradient and mismatch on devices                                         | 48                       |

| Figure 6.5: Input-output difference                                                              |                          |

| Figure 6.6: Breaking a device into unit sizes                                                    | 50                       |

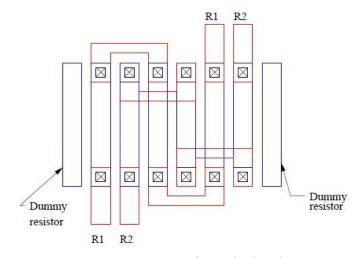

| <b>Figure 6.7 :</b> Dummy resistors at the edges of array                                        |                          |

| <b>Figure 6.8 :</b> Layout of matched resistors.                                                 |                          |

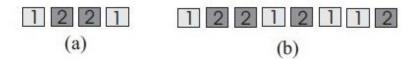

| Figure 6.9: 1-D symmetry layout structures                                                       | 53                       |

| Figure 6.10 : 2-D symmetry examples.                                                             | 54                       |

| Figure 6.11 : Complex 2-D layout structures                                                      |                          |

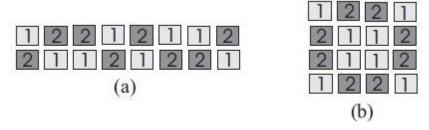

| Figure 7.1: Adaptive output buck converter system model                                          |                          |

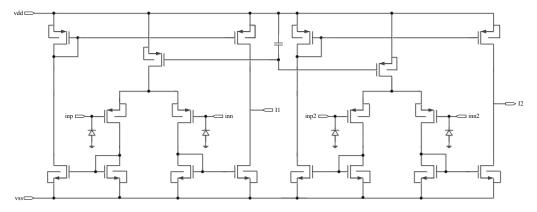

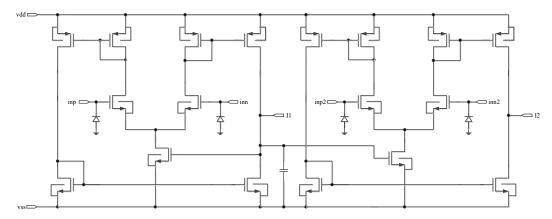

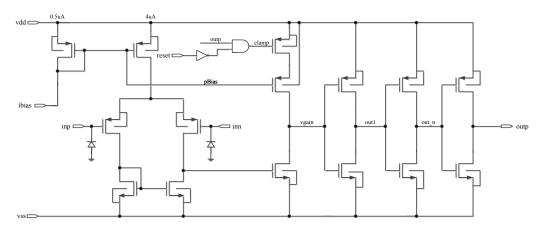

| Figure 7.2: Adaptive Capacitive Gm schematic                                                     |                          |

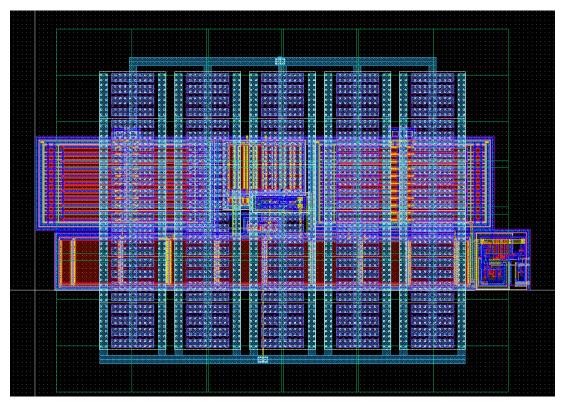

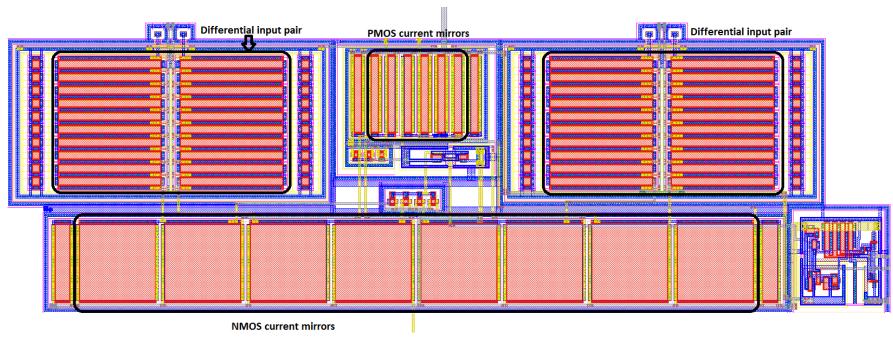

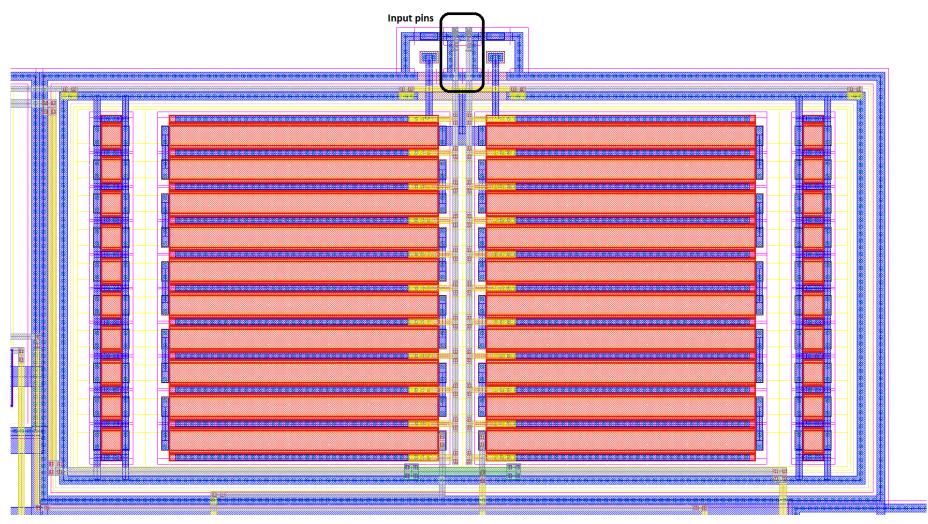

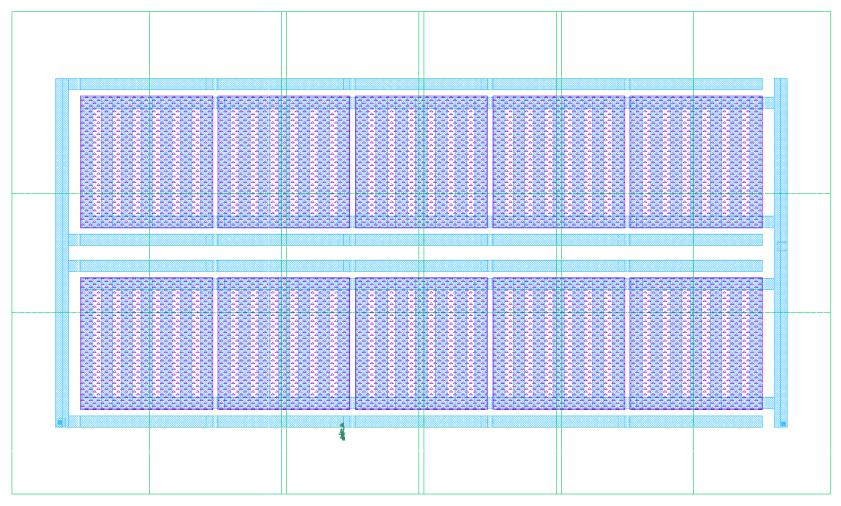

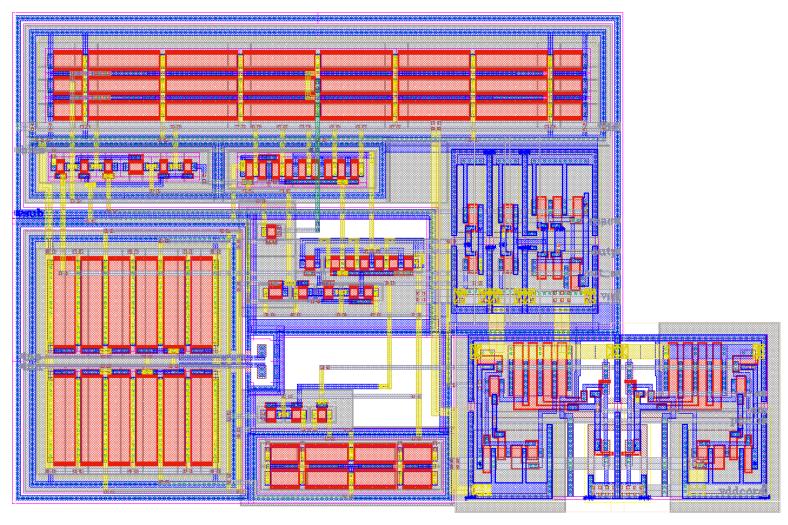

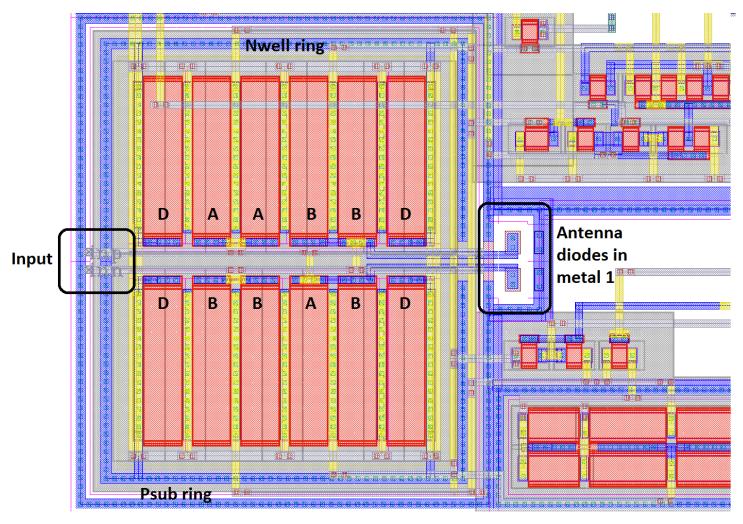

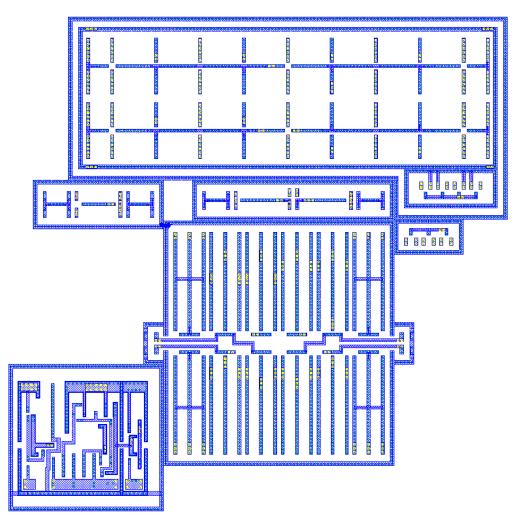

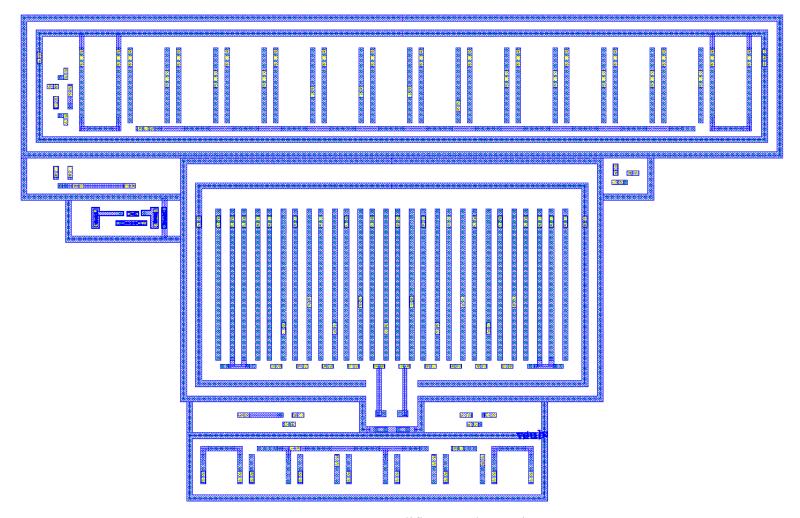

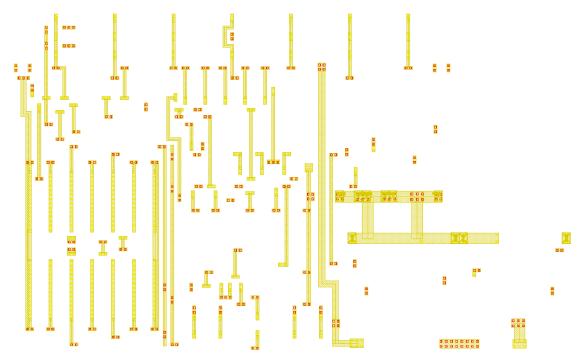

| Figure 7.3: Overall layout of Adaptive Capacitive Gm block                                       |                          |

| Figure 7.4: Simplified Layout of Adaptive Capacitive Gm block                                    |                          |

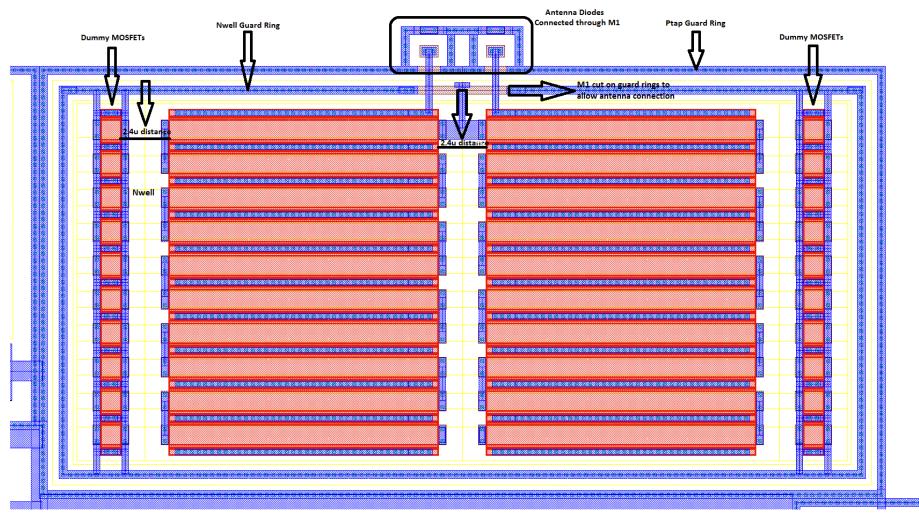

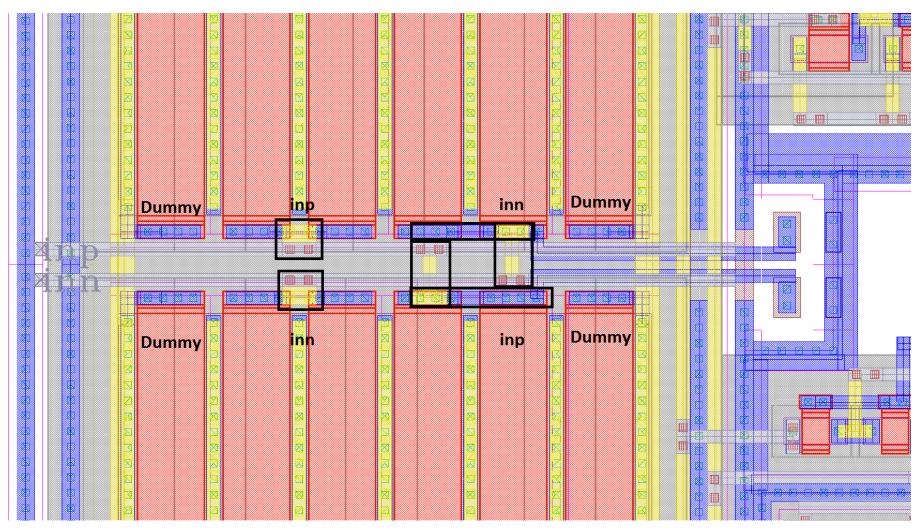

| Figure 7.5: Differential input pairs with detailed explanation                                   |                          |

| Figure 7.6: Layout with metal routing connections                                                |                          |

| Figure 7.7: Schematic of adaptive resistive gm circuit                                           |                          |

| Figure 7.8: Overall layout of Adaptive Resistive Gm block                                        |                          |

| Figure 7.9: Layout of adaptive resistive gm block in detail.                                     |                          |

| Figure 7.10: MIM capacitor block                                                                 |                          |

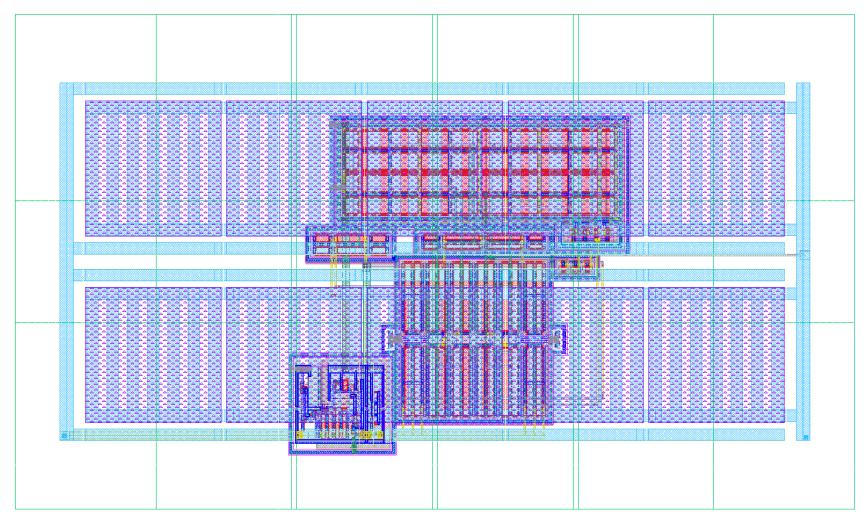

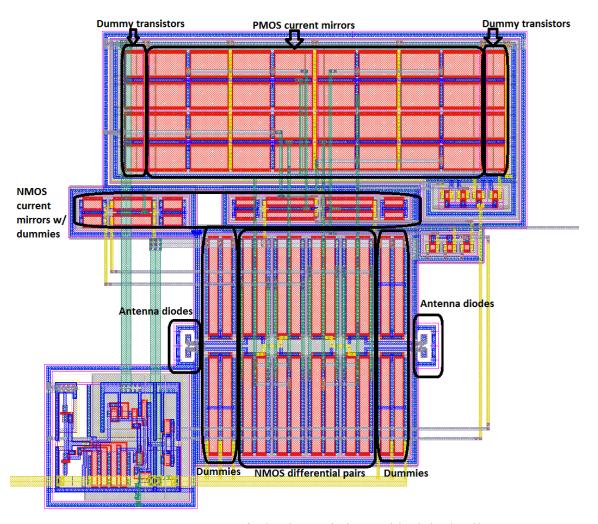

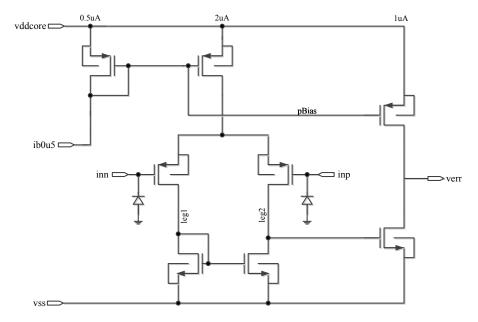

| Figure 7.11 : Schematic of error amplifier.                                                      |                          |

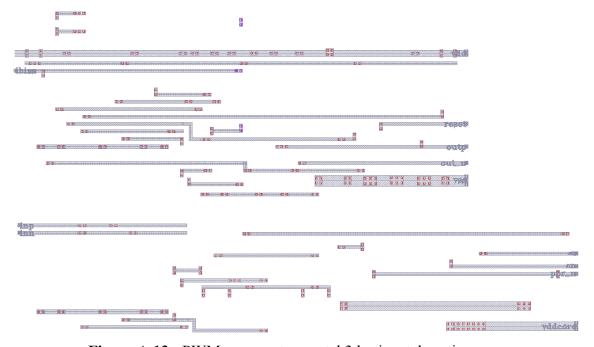

| Figure 7.12: Layout of error amplifier                                                           |                          |

| Figure 7.13 : Detailed PMOS differential pair                                                    |                          |

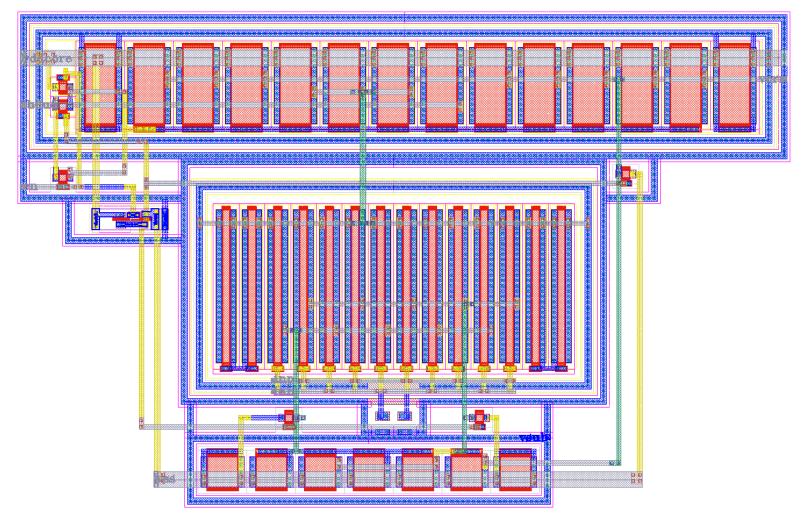

| Figure 7.14 : Schematic of PWM comparator                                                        |                          |

| Figure 7.15 : General layout of PWM comparator                                                   |                          |

| Figure 7.16: Differential pair zoomed                                                            |                          |

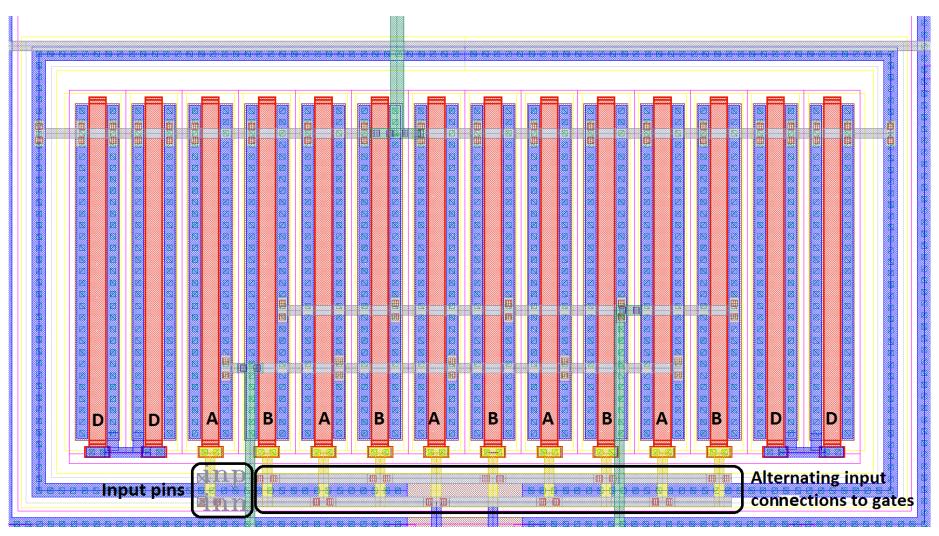

| Figure 7.17: Gate connections of common-centroid differential PMOS pairs                         |                          |

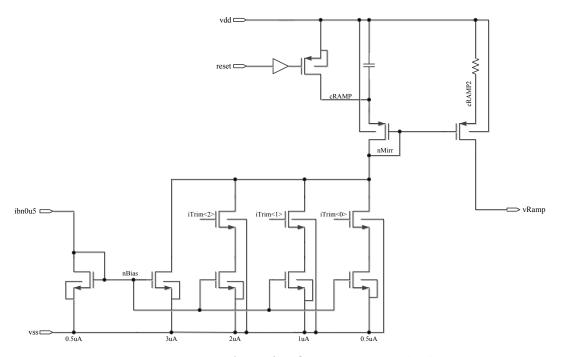

| Figure 7.18: Schematic of ramp generator                                                         |                          |

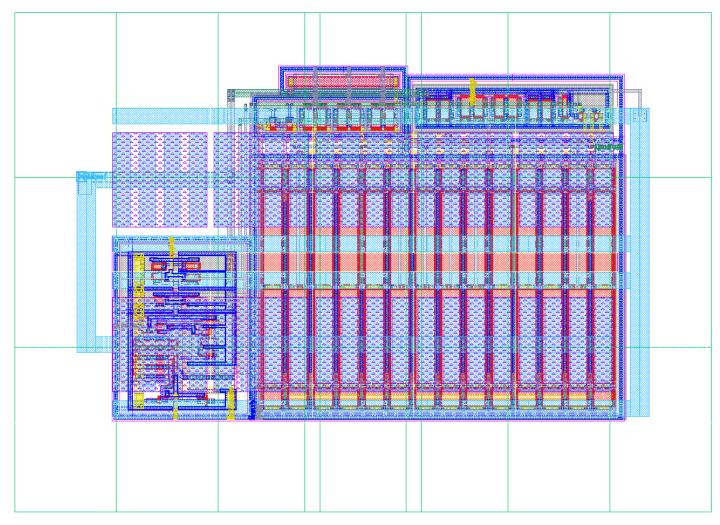

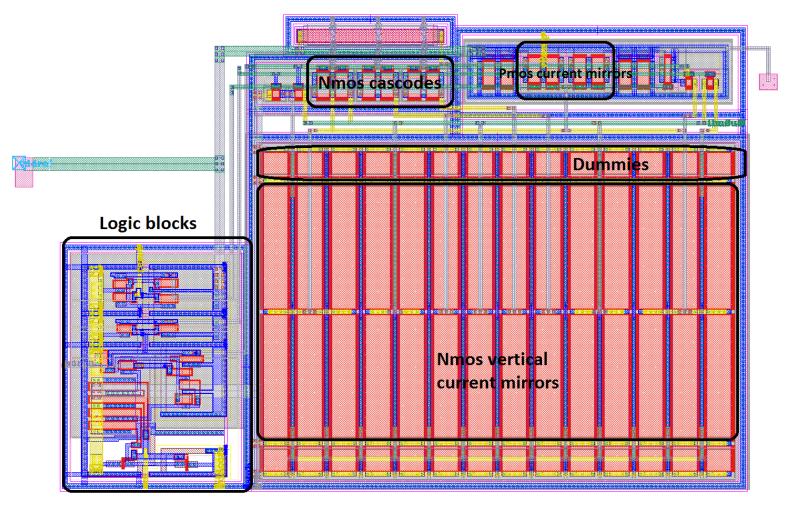

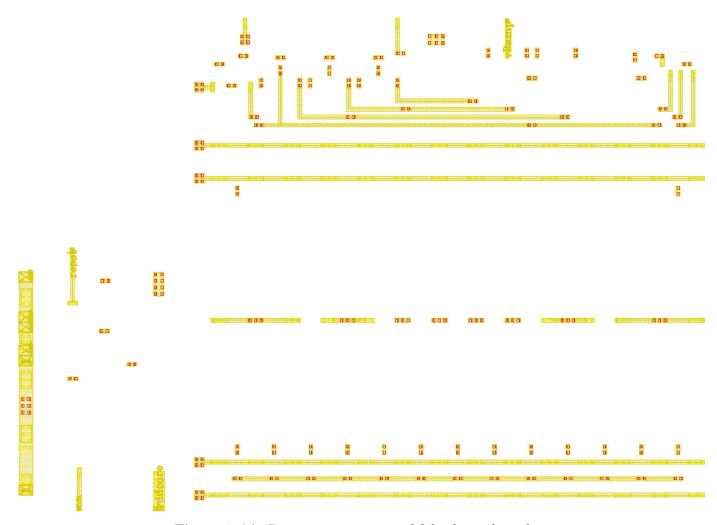

| Figure 7.19: General layout of ramp generator                                                    |                          |

| Figure 7.20: Simplified layout without MIM capacitors on top                                     |                          |

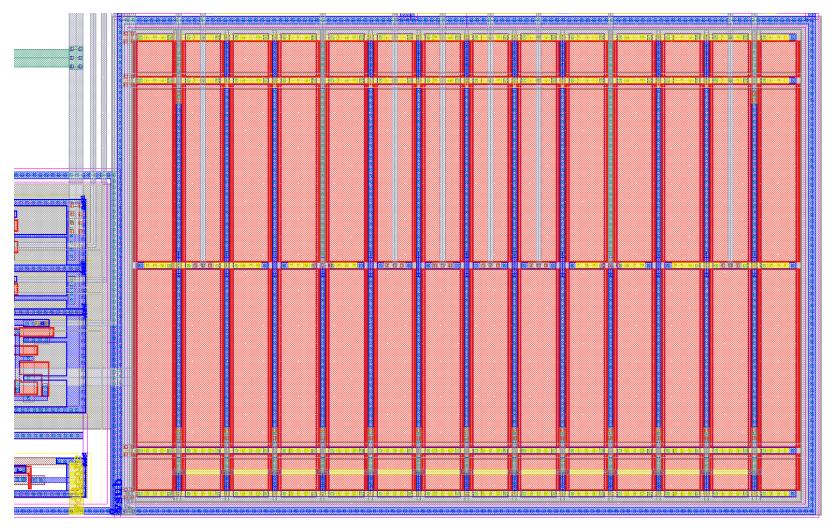

| Figure 7.21: NMOS current mirror connections                                                     | /4<br>75                 |

| Figure 7.22: Schematic design of vSense sample&hold block                                        |                          |

| 9                                                                                                | 7 <b>0</b><br>7 <b>7</b> |

|                                                                                                  |                          |

| Figure 7.24: Schematic of active diode comparator.                                               |                          |

| Figure 7.25: Layout of active diode comparator  Figure 7.26: Detailed blocks inside active diode |                          |

|                                                                                                  |                          |

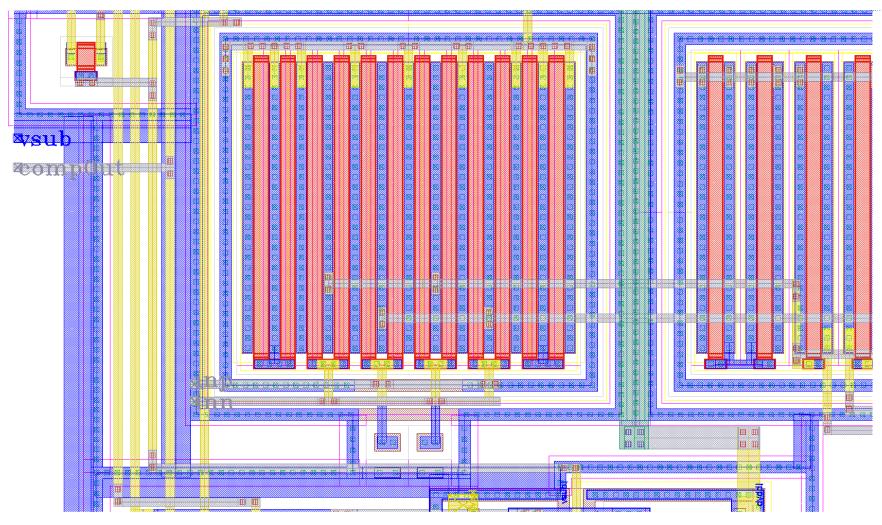

| Figure 7.27: First stage PMOS differential pair and connections                                  |                          |

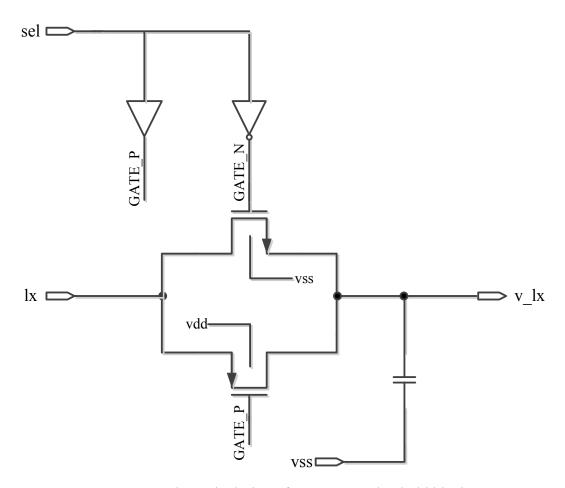

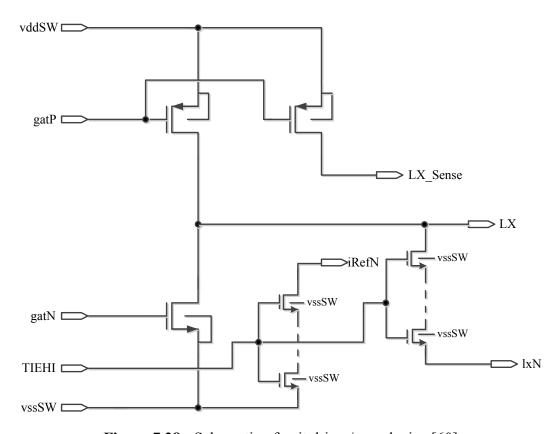

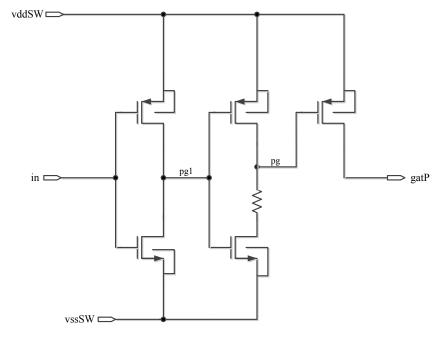

| Figure 7.28: Schematic of unit driver/pass device                                                |                          |

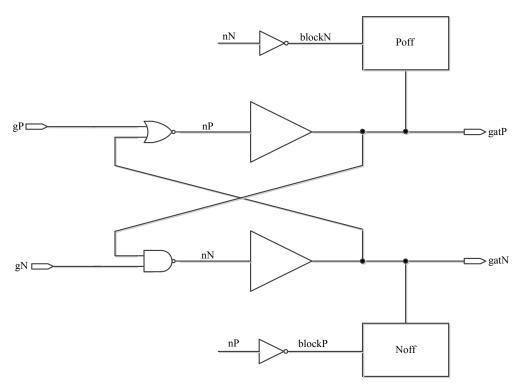

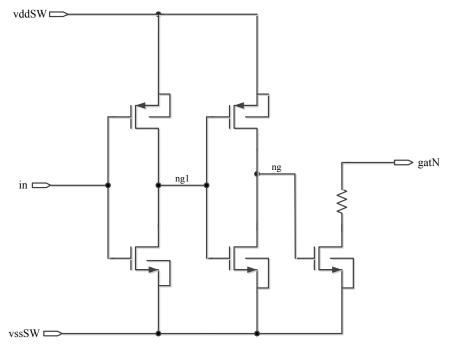

| Figure 7.29: Schematic of unit pre driver                                                        |                          |

| Figure 7.30 : Schematic design of P <sub>off</sub> logic                                         |                          |

| Figure 7.31 : Schematic design of N <sub>off</sub> logic                                         |                          |

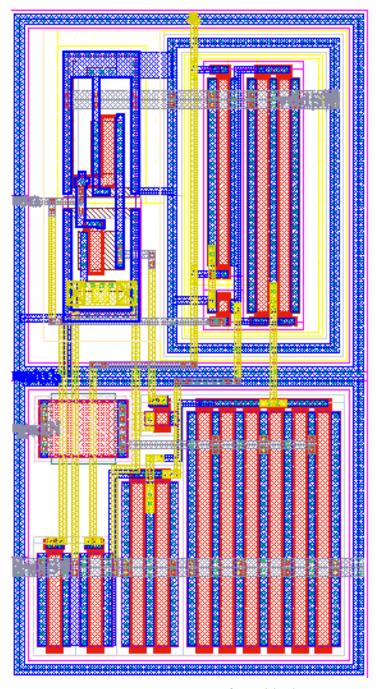

| Figure 7.32: Layout of N <sub>off</sub> block                                                    |                          |

| Figure 7.33: Layout of P <sub>off</sub> block                                                    |                          |

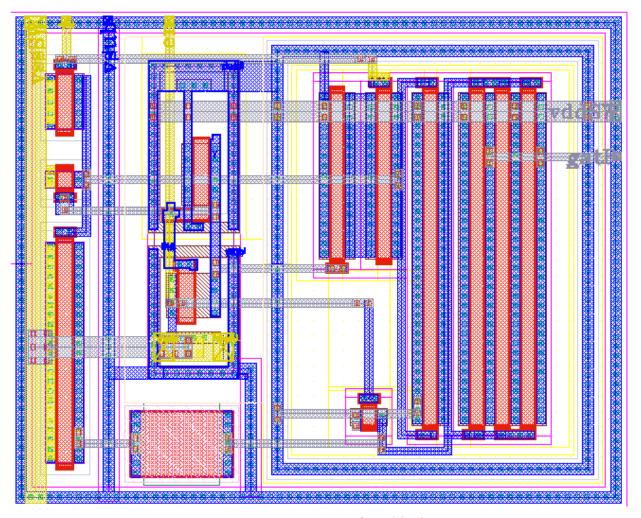

| Figure 7.34: Layout of buck unit drive block                                                     |                          |

| Figure 7.35: Buck drive unit and its sub blocks                                                  |                          |

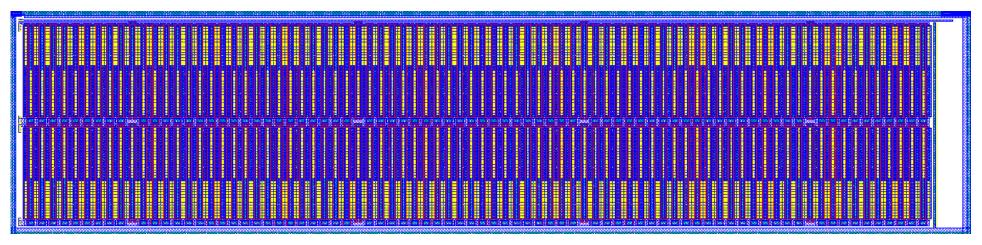

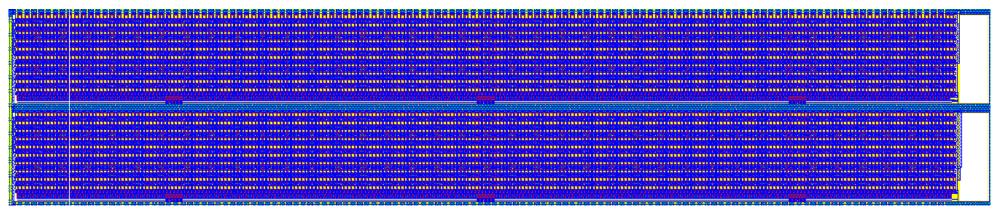

| Figure 7.36: NMOS unit pass device layout                                                        |                          |

| Figure 7.37: NMOS unit pass device with metal 2                                                  |                          |

| Figure 7.38: NMOS unit pass device with metal 3                                                  |                          |

| Figure 7.39: NMOS unit device with metal 4                                                       |                          |

| Figure 7.40: NMOS unit pass device metal 5                                                       | 93                       |

| Figure 7.41: PMOS unit pass device                                                                               | 93  |

|------------------------------------------------------------------------------------------------------------------|-----|

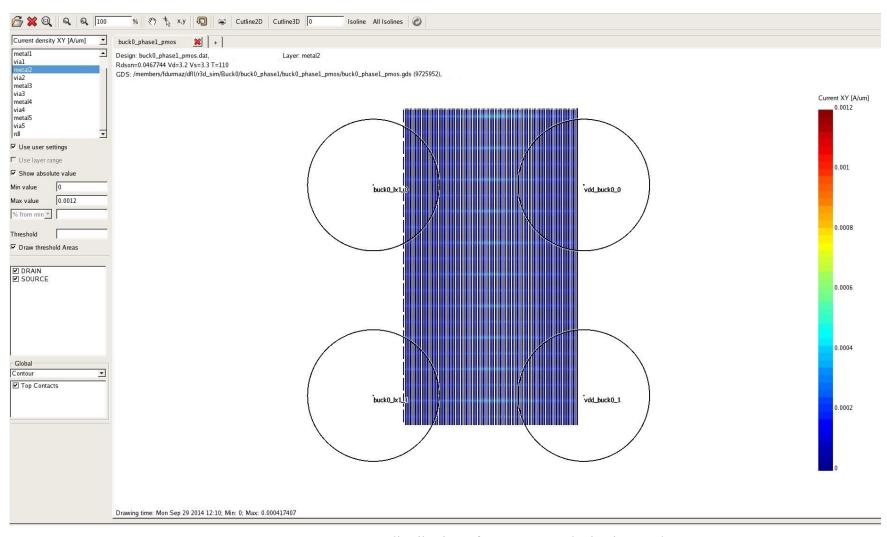

| Figure 7.42: PMOS unit pass device with metal 2                                                                  | 94  |

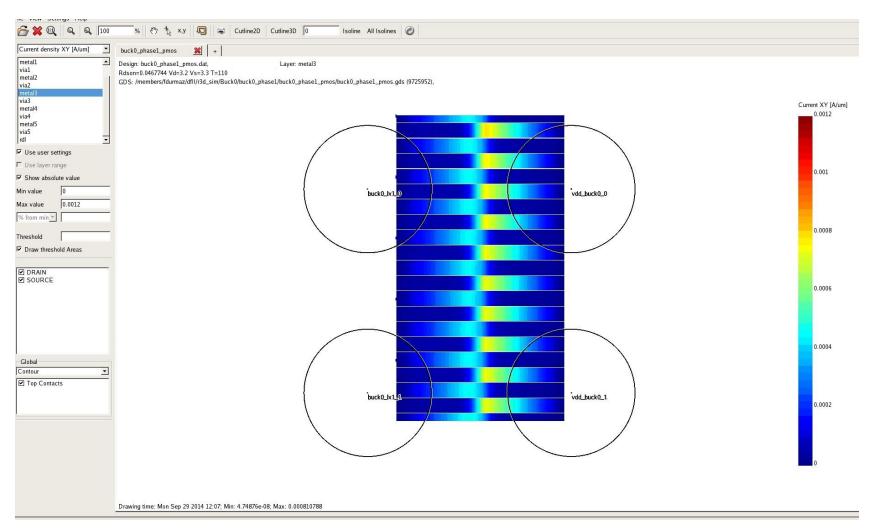

| Figure 7.43: PMOS unit pass device with metal 3                                                                  | 94  |

| Figure 7.44: PMOS unit pass device with metal 4                                                                  |     |

| Figure 7.45: PMOS unit pass device with metal 5                                                                  | 95  |

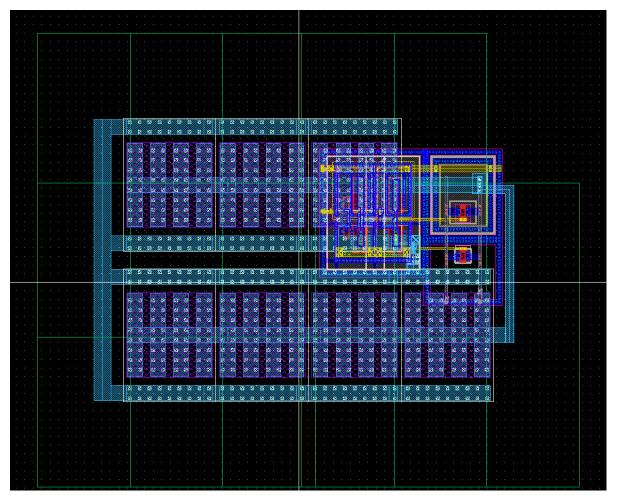

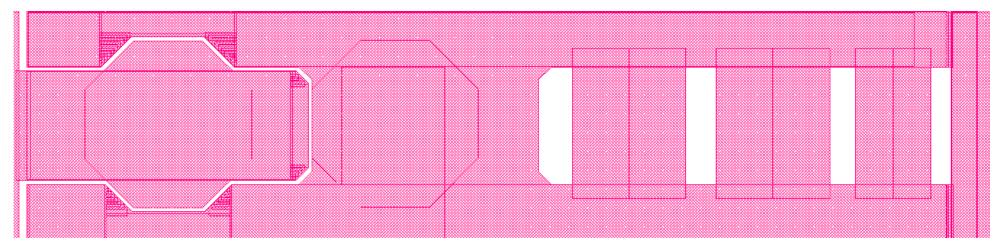

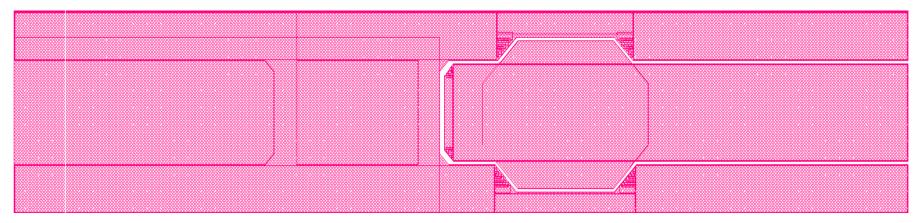

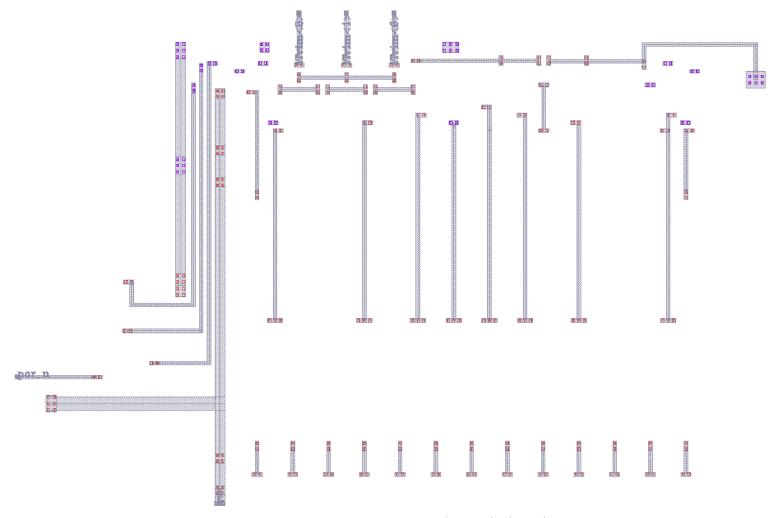

| Figure 7.46: Pass device layout with its drivers                                                                 | 97  |

| Figure 7.47: Schematic of current sense block                                                                    |     |

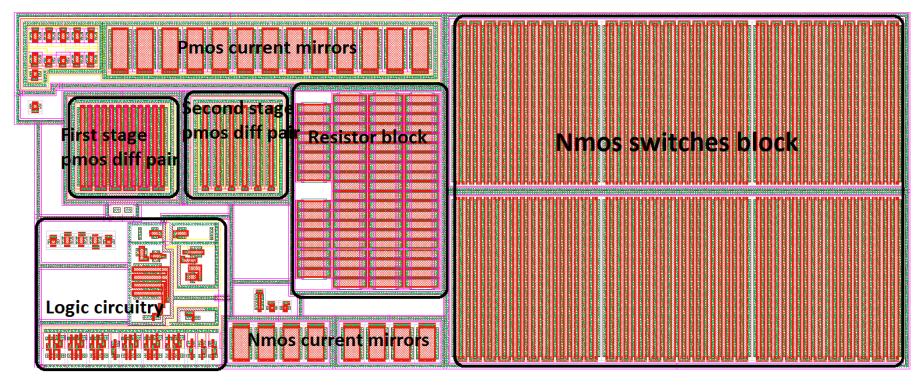

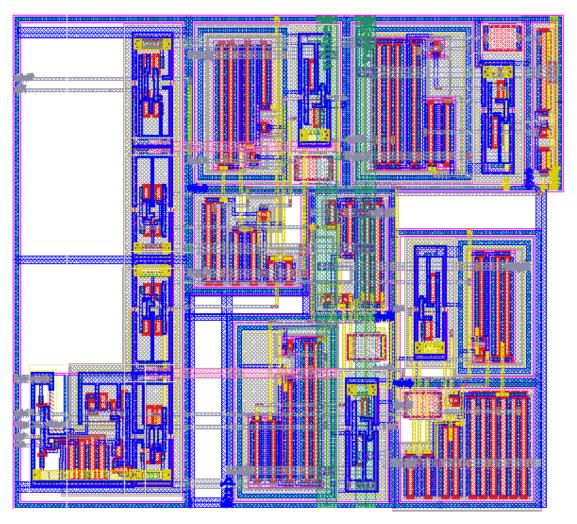

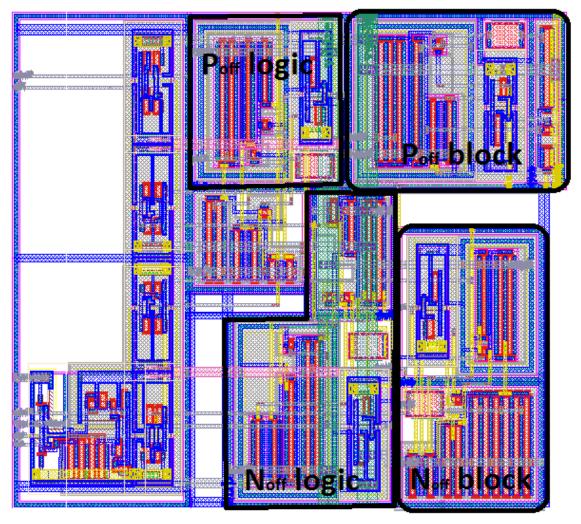

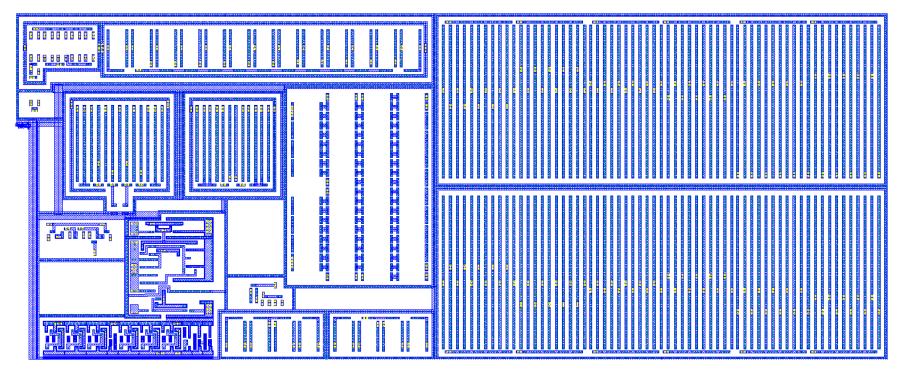

| Figure 7.48: Complete layout of buck converter                                                                   | 99  |

| Figure 7.49: Buck converter blocks                                                                               |     |

| Figure 8.1: Resistance of a straight piece of metal                                                              | 102 |

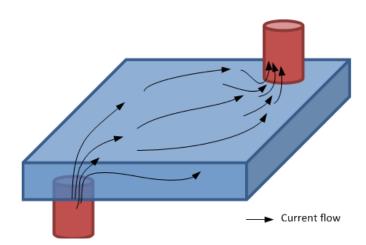

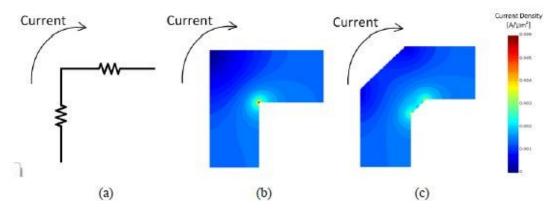

| Figure 8.2 : Current crowding effect near the contacts                                                           |     |

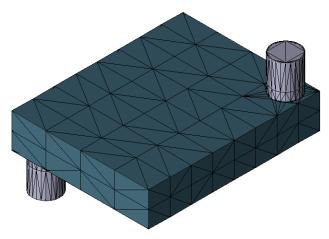

| Figure 8.3: 3D mesh of a metal interconnect                                                                      | 104 |

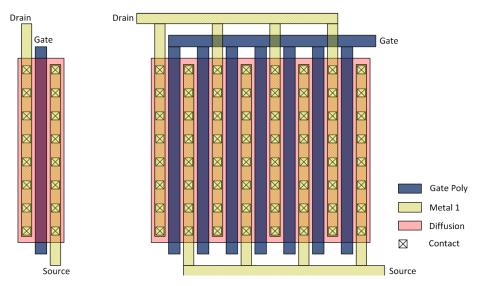

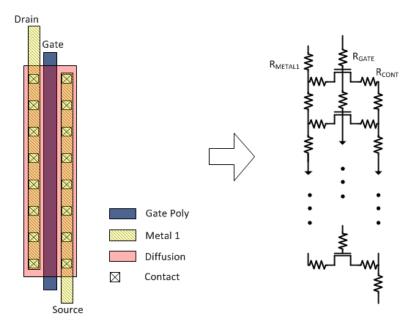

| Figure 8.4: Single MOS finger layout, basic MOS multi-finger layout                                              | 105 |

| Figure 8.5 : SPICE lumped-element model for MOS finger                                                           |     |

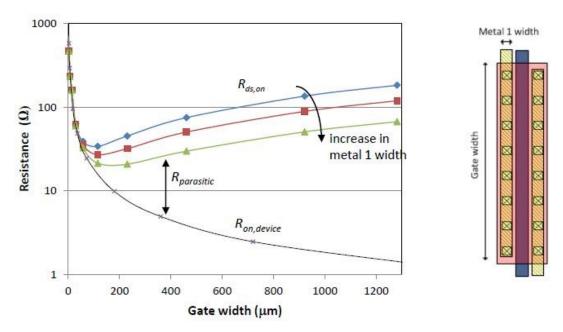

| <b>Figure 8.6 :</b> Simulation results of R <sub>on,device</sub> , R <sub>ds,on</sub> and R <sub>parasitic</sub> |     |

| Figure 8.7 : SPICE lumped-element model of a cornered metal interconnect                                         |     |

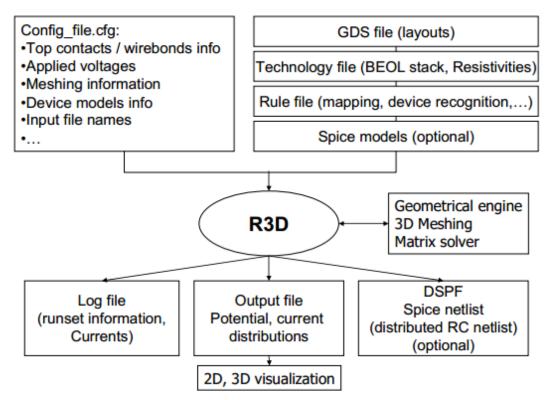

| Figure 8.8: R3D simulation flow diagram                                                                          |     |

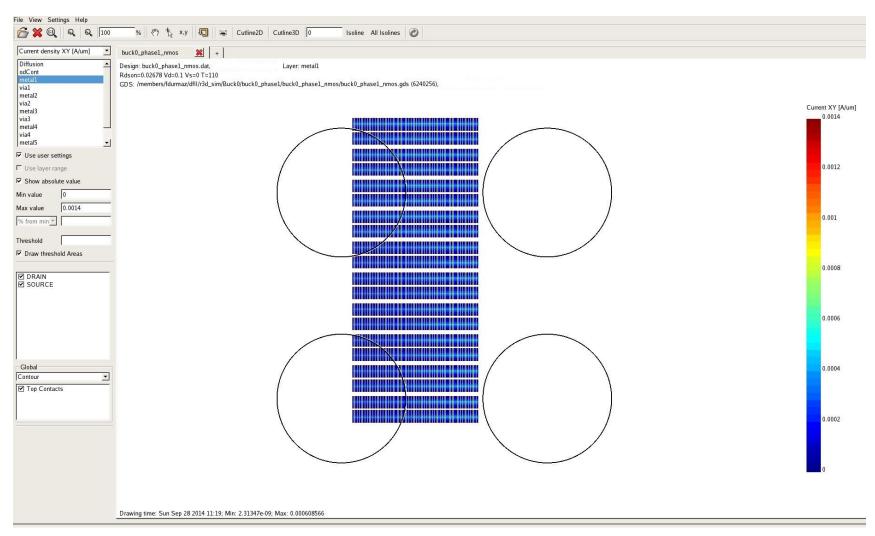

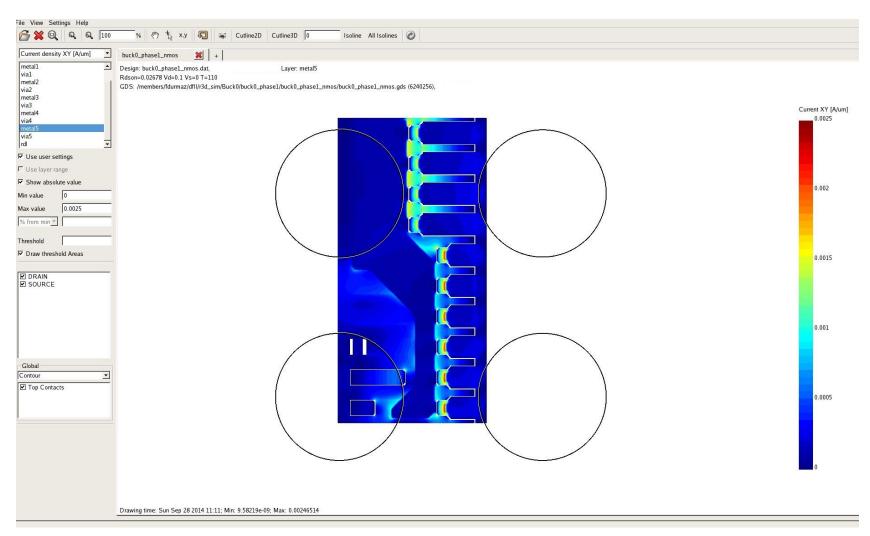

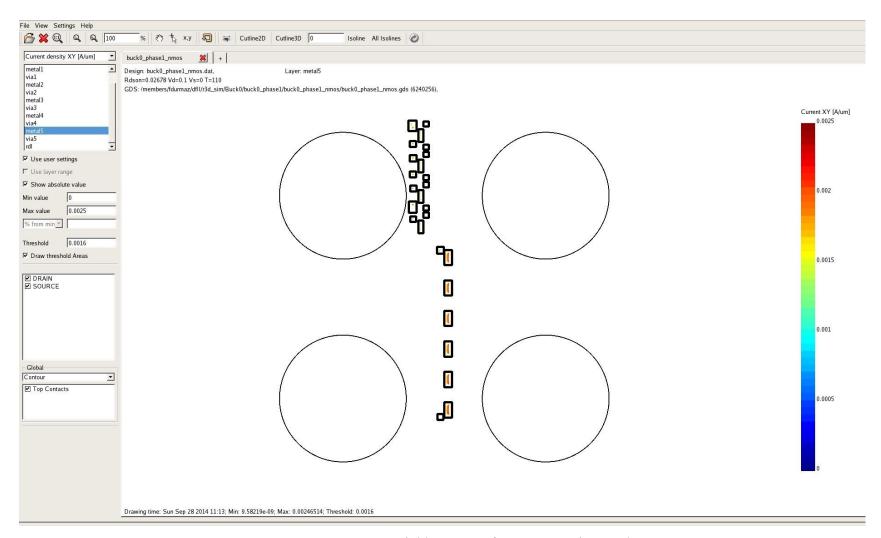

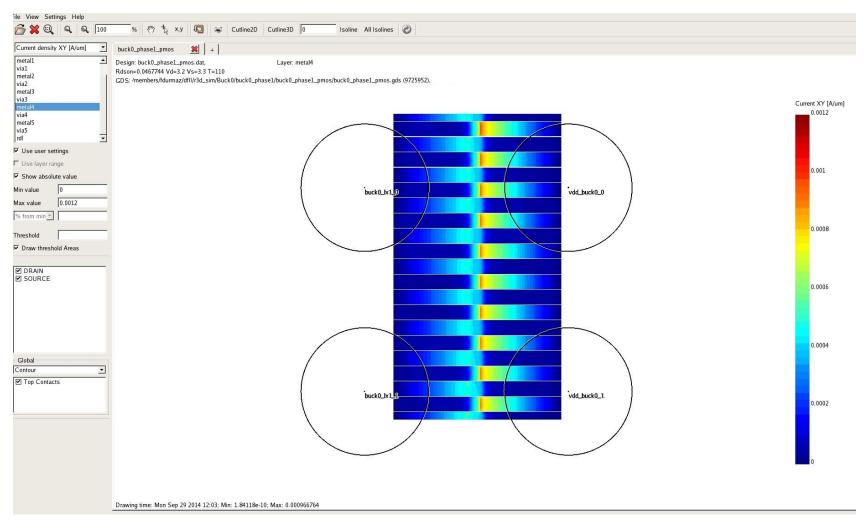

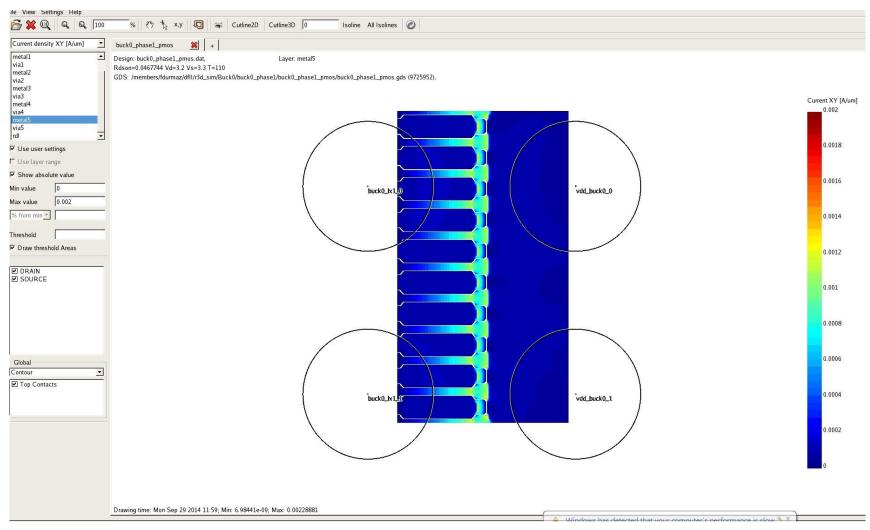

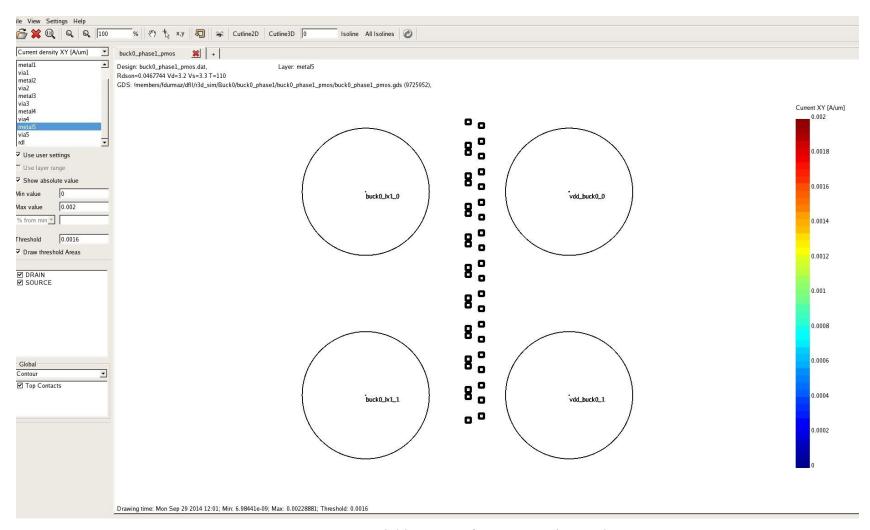

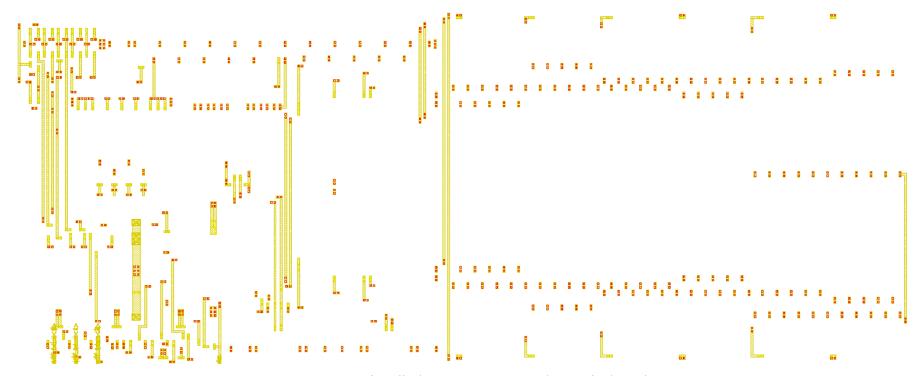

| Figure 8.9: R3D Current distribution of NMOS pass device in metal 1                                              |     |

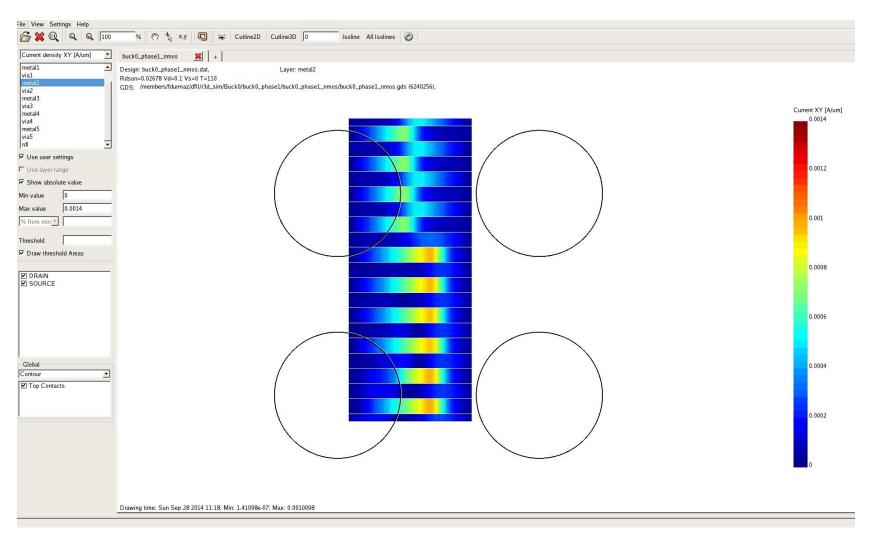

| Figure 8.10: R3D Current distribution of NMOS pass device in metal 2                                             |     |

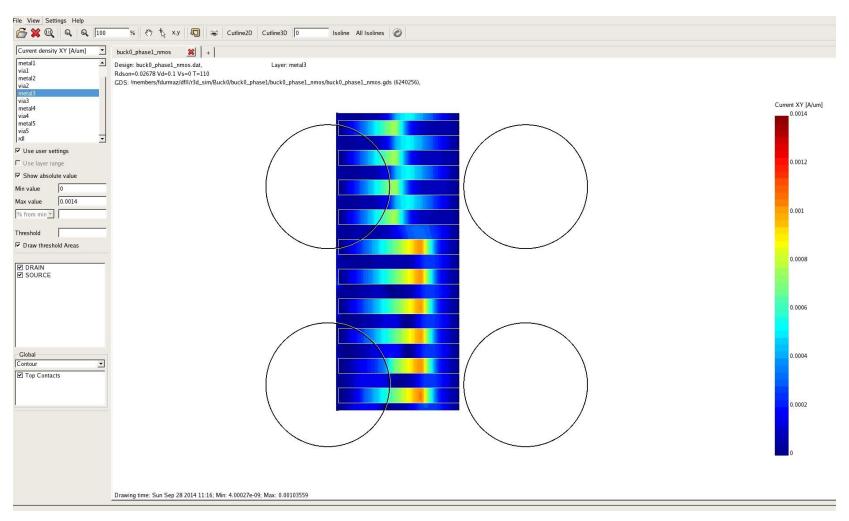

| Figure 8.11: R3D Current distribution of NMOS pass device in metal 3                                             |     |

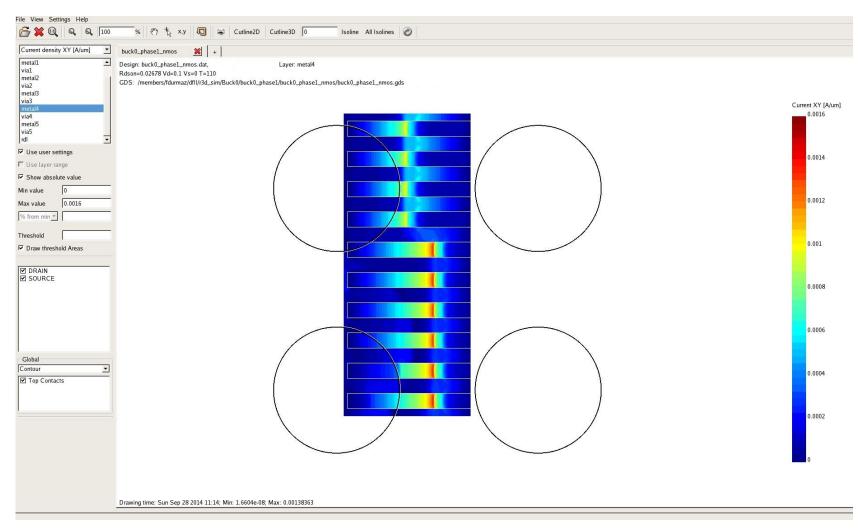

| Figure 8.12: R3D Current distribution of NMOS pass device in metal 4                                             |     |

| Figure 8.13: R3D Current distribution of NMOS pass device in metal 5                                             |     |

| Figure 8.14: R3D Potential hotspots of NMOS part in metal 5                                                      |     |

| Figure 8.15: R3D Current distribution of PMOS pass device in metal 2                                             |     |

| Figure 8.16: R3D Current distribution of PMOS pass device in metal 3                                             |     |

| Figure 8.17: R3D Current distribution of PMOS pass device in metal 4                                             |     |

| Figure 8.18: R3D Current distribution of PMOS pass device in metal 5                                             |     |

| Figure 8.19: Potential hotspots of PMOS part in metal 5                                                          |     |

| Figure 8.20: R3D resistance result for NMOS part                                                                 |     |

| Figure 8.21: R3D resistance result of PMOS part.                                                                 |     |

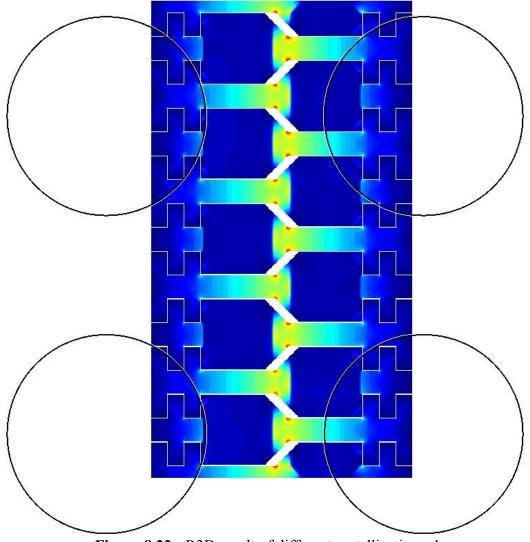

| <b>Figure 8.22 :</b> R3D result of different metallization - 1                                                   |     |

| Figure 8.23: R3D result of different metallization - 2                                                           |     |

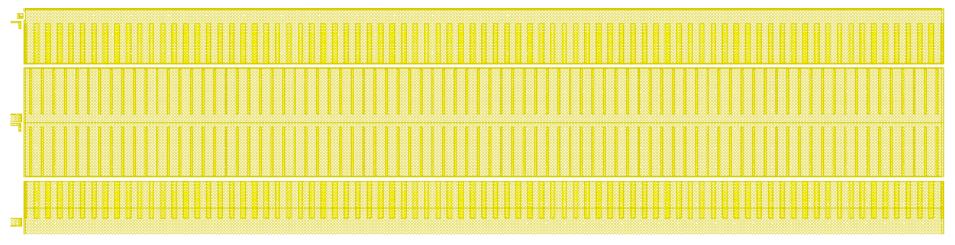

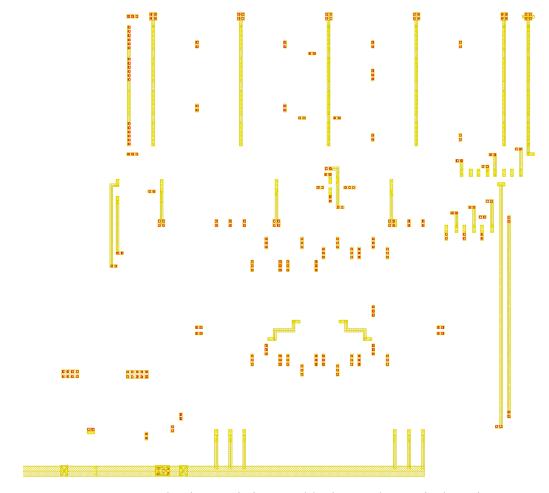

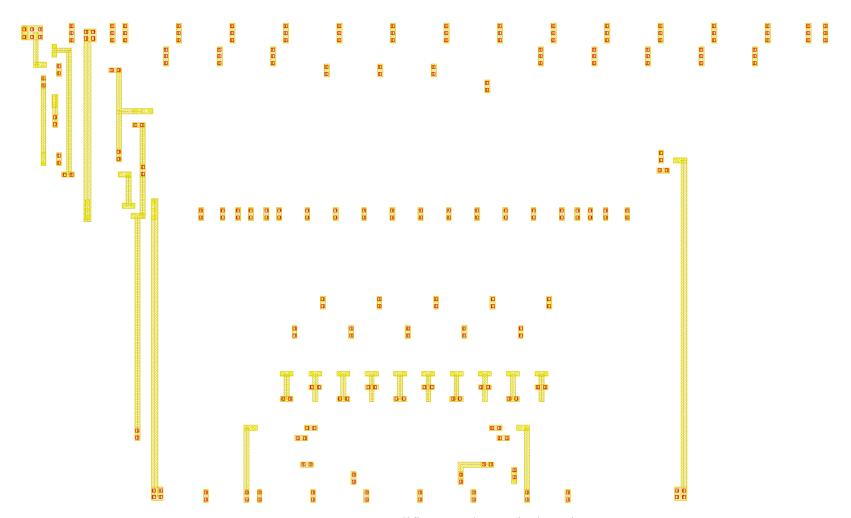

| Figure A.1: Adaptive Capacitive Gm block metal 1 routings                                                        |     |

| Figure A.2: Adaptive Capacitive Gm block metal 2 vertical routings                                               |     |

| Figure A.3: Adaptive Capacitive Gm block metal 3 horizontal routing                                              |     |

| Figure A.4: Adaptive Resistive Gm block, metal 1 routings                                                        |     |

| Figure A.5: Adaptive Resistive Gm block, metal 2 vertical routings                                               |     |

| Figure A.6: Adaptive Resistive Gm block, metal 3 horizontal routings                                             |     |

| Figure A.7: Adaptive Resistive Gm block, metal 4 vertical routings                                               |     |

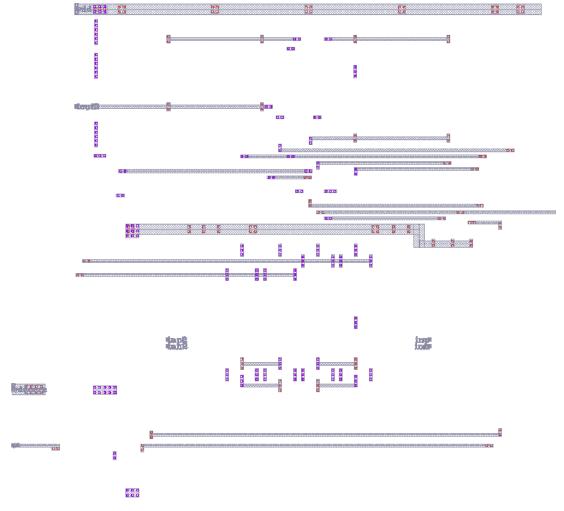

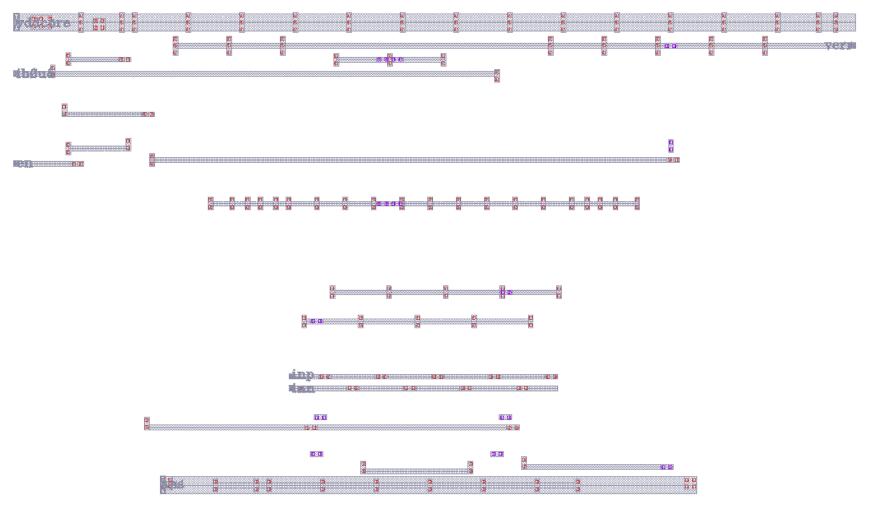

| <b>Figure A.8 :</b> Error amplifier, metal 1 routings                                                            |     |

| <b>Figure A.9 :</b> Error amplifier, metal 2 vertical routings                                                   |     |

| Figure A.10: Error amplifier, metal 3 horizontal routings                                                        |     |

| Figure A.11: Error amplifier, metal 4 vertical routings                                                          |     |

| Figure A.12: PWM comparator, metal 2 vertical routings                                                           |     |

| Figure A.13: PWM comparator, metal 3 horizontal routings                                                         |     |

| Figure A.14: Ramp generator, metal 2 horizontal routings                                                         |     |

| Figure A.15: Ramp generator, metal 3 vertical routings                                                           |     |

| Figure A.16: Ramp generator, metal 4 horizontal routings                                                         |     |

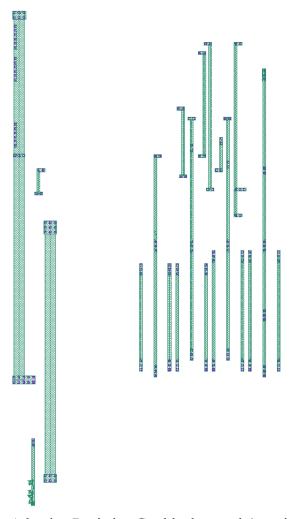

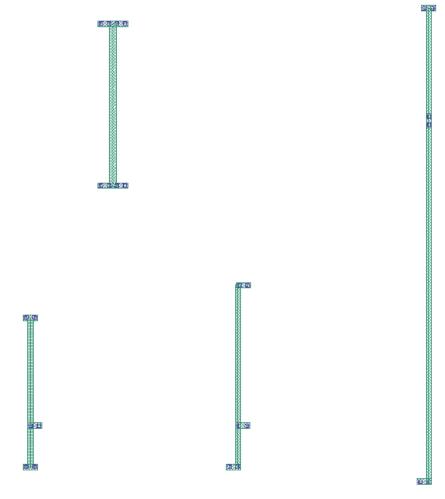

| Figure A.17: Active diode comparator, metal 1 routings                                                           |     |

| Figure A.18: Active diode comparator, metal 2 vertical routings                                                  |     |

| Figure A.19: Active diode comparator, metal 3 horizontal routings | 153 |  |

|-------------------------------------------------------------------|-----|--|

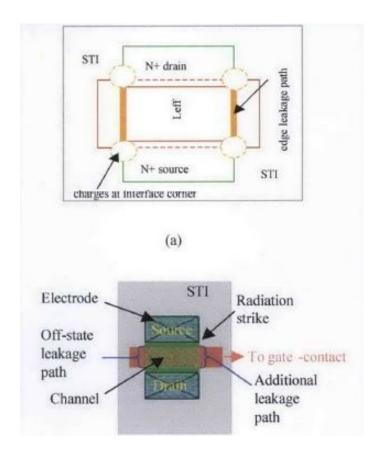

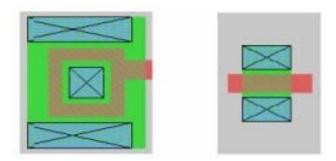

| Figure C.1: Radiation effects mechanism                           | 156 |  |

| Figure C.2: An ELT and a simple MOSFET                            | 156 |  |

### ANALOG LAYOUT TECHNIQUES AND APPLICATION TO AN ADAPTIVE OUTPUT BUCK CONVERTER

#### **SUMMARY**

Integrated circuits (ICs) have become an essential part of our daily lives. Different kind of chips called Application Specific Standart Product (ASSP) is being used in specific part of a system. Chip creation contains analog, digital and layout designs. Each design step is important to successfully fabricate desired chips.

There is a need for power management circuitry in ICs, in order to power each and every device. Today's trend of mobile technology increases the need of power management. LDOs, DC-DC converter or buck converter and buck-boost converters must be utilized. Inside ICs, power management circuit design is an active research area and there are many publications in the literature about this topic. This thesis focuses on basic layout, layout strategies and layout of buck converter.

This thesis is organized as follow. In chapter 1, the fabrication process of. MOSFET devices are explained. Then basic layout structures are described in detail, starting from CMOS layout structures to diode, BJT layout and layout of passive components. Isolation structures are explained in chapter 4. These isolations are both contain process related isolation and layout design isolations. Issues coming from layout are given in detail in chapter 5 which affects block performance significantly. Layout matching is explained and demonstrated in chapter 6. These layout structures and strategies are very important in layout design.

In chapter 7, analog blocks of adaptive output buck converter is explained in detail. The layout designs are analysed in detail to show what kind of layout structure is used. Most important part of buck converter is the pass device which is explained in detail with layouts. Resistive extraction tool is used to extract metallization resistance for spotting the weak parts in pass device metal structure. Moreover, this tool gives the total on resistance of pass device which can be given feedback to analog designer to modify their buck converter simulations.

Total laid out pass device area is 800μ x 650μ while total buck converter design occupies 800μ x 940μ. Buck converter is designed in a 0.25μ process with 1 poly 5 metal process.

# ANALOG SERIM TEKNIKLERI VE UYARLANABILEN CIKIS ALCALTICI DÖNÜŞTÜRÜCÜYE UYGULANMASI

#### ÖZET

Otuz yılda teknolojinin gelişmesi ile hayatımız değişmiş, teknoloji büyük yer kaplamaya başlamıştır. Bunun arkasında tümdevre tasarımı ve üretimi önemli bir yer kaplamaktadır. On sekiz ayda bir tümdevrenin boyunun yarıya inmesi veya işlem gücünün iki katına çıkması mottosu gelişimi hızlıandırmıştır. Tümdevrelerin temel yapı taşı olan yongalar bu harekete ayak uydurma adına giderek küçülmekte veya bir yonganın tek başına gerçekleştirdiği işlem yapabilme kabiliyeti artmaktadır. Yonga tasarımı temelinde analog tasarım, sayısal tasarım ve serim içermektedir. Bunlar ayrı ayrı gibi gözüksede bir yonga içinde bunları barındarmaktadır.

Analog tasarım ve sayısal tasarım bilgisayar destekli tasarım programları ile simülasyonları yapılmakta ve yapılan tasarım doğrulanmaktadır. Daha sonra bu tasarımların yonga içerisinde yerleştirilmesi, farklı amaç için tasarlanmış devreler daha sonra birbirleri ile gerekli bağlantıların yapılması suretiyle, uygulamanın ihtiyaç duyduğu belli bir amaca sahip yonga üretilmektedir. Devrelerin, transistörlerin ve diğer yapıların yerleştirilmesi, birbirleri ile gerekli bağlantılarının yapılması noktasında serim denmektedir. Analog ve sayısal tasarımlarda kullanılan transistor boyutu küçüldükçe tasarlanan devrelerde yaşanabilecek sorunlar artmaktadır. Özellikle kullanılan transistör, direnç ve kapasitörlerin boyutu küçüldükçe üretiminde kaynaklanabilecek ve serim aşamasında sorun yaratma durumları artmaktadır.

Günümüzde eğilim teknolojik ürünlerin düşük çalışma enerji özellikleri ile batarya ömrünün uzun olması yönündedir. Bunun olmasını sağlayan unsurlardan biri yongaların düşük enerji tüketmesi için ihtiyaç duydugu gerilim ve akım değerlerinin azaltılması, diğer unsur ise bataryaların teknolojisi geliştirilip aynı boyutlarda daha yüksek enerji depolanmasıdır. Yongaların ihtiyaç duyduğu düşük gerilim değerlerini bataryanın sağladığı gerilim değeri ile sağlamak mümkün değildir. Çünkü bataryanın enerjisi azaldıkça, sağladığı gerilim değeri ihtiyaç duyulan sabit gerilim sağlayamamaktadır.

Bu nedenle güç yönetimi yongaları kullanılmaktadır. İçinde bulundurduğu elemanlar ile bataryadan aldığı gerilim ve akım değerlerini düzenleyip, sistemde bulunan her yonganın ihtiyaç duyduğu, her yongaya özel gerilim ve akım değerlerini sağlayarak sisteme iletmektedir.

Güç yönetimi yongası içinde kullanılan en önemli elemalardan biri çıkış alçaltıcı dönüştürücü elemanıdır. Bu elemanın amacı, bataryadan gelen değişken gerilim değerini, gerekli gerilim ve akım değerine regüle ederek ve bunu yaparkan verimlilik yani enerji kaybını en az seviyede tutarak yapan elemandır. Günümüzde çıkış alçaltıcı dönüştürücü elemanlarının verimlilik değeri %95 ler civarındadır. Bu sayede gerilim ve akım regüle edilirken enerji seviyesi en az seviyede tutulmaktadır.

Tezin amacı, çıkış alçaltıcı dönüştürücü elemanına serim teknikleri bakımından incelenmesi ve uygulanınca daha iyi sonuçlar veren serim teknik ve özelliklerine odaklanmıştır.

Tezin giriş kısmından sonra ikinci bölümünde transistörün üretim aşamaları anlatılmıştır. Daha sonra endüstride yaygın olarak kullanılan N katkılı transistör ve P katkılı transistörlerin birlikte kullanıldığı birbirini tamamlayan metal oksit yarıiletken üretim teknolojisi detaylı bir şekilde anlatılmıştır.

Üçüncü bölümde en temel serim yapıları aktarılmıştır. N katkılı transistor, P katkılı transistörlerin serim yapıları ve özellikleri gösterilmiştir. Sonrasında diyot yapısının serimi anlatıldı, çift kutuplu transistör yapısı gösterildi. Tasarlanan yongalarda kullanılan direnç yapısı ve direnç çeşitleri aktarıldı. Aynı şekilde kullanılan kapasite çeşitleri, birbirlerine göre üstünlükleri şekiller yardımıyla detaylı bir şekilde anlatıldı. Transistörleri, yarı-iletken olmayan elemanları ve devrelerin bağlanması için kullanılan metallerin kullanım sonucu aşınarak düşük dirençli olması istenirken, iç direncinin artmasi durumu anlatıldı. Fiziksel etkilerin buna neden olması durumları açıklanmistir.

Tasarlanan devrelerin tasarlanma durumlarına göre yüksek gürültülü olma durumunun izolasyon teknikleri ile nasıl birbirlerin ayrılabileceği detaylı bir şekilde açıklandı. Bu izolasyon yapıları üretimde özel teknikler ile sağlanabildiği yapılar ile serim aşamasında uygulanabilecek izolasyon stratejileri anlatılmistir.

Beşinci bölümde serimden kaynaklanabilecek sorunlar detaylı bir şekilde açıklandı. Doğru yaklaşım yapılmamış bir serimin bütün yongayı ve dolayısıyla tümdevreyi yakma durumu anlatıldı. Sorunlarında bir diğeri N katkılı transistörlerin ve P katkılı transistörlerin birbirlerine fazla yakın yerleştirmesi sonucu iki yapınında analog tasarımda yapılan simülasyondaki modelinden çok daha farklı davranma durumu anlatıldı. Bu olası sorunların serim aşamasında nasıl dikkate alınması gerektiği, analizinin nasıl ve hangi temelle yapılması gerektiği dolayısıyla bu sorunların çözümleri gösterilmistir.

Devre tasarımında yapılan simülasyon ile serimde yongaya konan transistörlerin aynı gerilim, akım davranışlarının sergilememesi durumu anlatıldı. Bunu nedenleri detaylı bir şekilde verildi. Çözüm olarak farklı serim teknikleri ve bunların avantajları, serime dolayısıyla devreye etkileri açıklandı. En önemli etmenin birbirleri ile belirli bir hassaslık derecesine sahip olması gereken tasarımlarım serim teknikleri, yerleştirme stratejisi, serimde birim eleman kullanmanın yarattığı iyileştirme, serimde transistörlerin kenarlarına konulan fazla transistörlerin birbirleriyle hassaslık gerektiren tranistör yapılarında yarattığı iyileştirme etkileri detaylı ve açıklayıcı bir şekilde anlatıldı. Metal bağlantılarda uygulanabilecek simetrinin avantajları gösterildi. Transistörlerin simetrik yerleştirilme şekilleri ve bu yerleştirme çeşitlerinin birbirlerine göre üstünlükleri anlatılmistir.

Yedinci bölümde, önceki bölümlerde anlatılan tüm yapıların, stratejilerin, göz önüne alınması gerekn durumların hepsi dikkate alınarak ve alçaltıcı dönüştürücü yonga tasarımında uygulanması detaylı bir şekilde anlatıldı. Alçaltıcı dönüştürücü tasarımının sahip oldugu alt analog devrelerin seriminin yapılış figürlerle ve açıklayıcı anlatımla aktarılmıştır.

Alçaltıcı dönüştürücünün en önemli yapı elemanı olan ve alçaltıcı dönüştürücünün mantığı olan yüksek akım sağlamayı sağlayan bu devre, serimi ve üzerine gerekli metallerin konmasından sonra yapılan 3 boyutlu direnç çıkarımı ve analizi yapan program ile analiz yapıldı. Bu programın görsel avantajı resimlerle detaylı bir şekilde aktarıldı. Bu programın transistör modeli arassındaki yaklaşım farkı örneklerle gösterildi. Alçaltıcı dönüştürücü üzerinde geçen yüksek akımın davranış özellikleri de anlatılmistir.

Son olarak serimi yapılmış alçaltıcı dönüştücü resimlerle gösterildi, yonga içerisinde kapladığı alan hesaplandı ve kullanılan transistörün yapıiçi direnci üzerine eklenen metallerin yarattıgı fazladan direnç değeri 3 boyutlu direnç çıkarım programı sayesinde bulunarak alçaltıcı dönüştürücünün üretildiğinde sahip olacağı toplam direnç bulundu. Tezin daha ileriye götürülebilmesi adına yapılabilecek adımlar hakkında bilgi verilmiştir.

#### 1. INTRODUCTION

Layout design is a part of chip design and production. It sits between circuit design phase and produced/real world chip architecture. Circuit design contains analog and digital design. All together builds a system and addition of mixed-signal creates chip required in real life. Circuit design is drawings of transistor-level or gate-level design of transistors. This is not real world representation of a chip. Thus, layout design is the physical representation of the circuit.

CMOS ICs are made using an extremely complicated process that in the end results in tiny transistors and metal wires being constructed and connected on a silicon substrate. Layout design is the art of drawing these transistors and wires as they look like in silicon.

The CMOS circuit design process consists of defining circuit inputs and outputs, hand calculations, circuit simulations, circuit layout, simulations including parasitics, reevaluation of circuit inputs and outputs, fabrication, and testing.

The task of laying out the IC is often given to a layout designer. Parasitics are the stray capacitances, parasitic resistances of wiring the nets, PN junctions, and bipolar transistors which cause latch-ups. Layouts of all these devices are explained in this thesis [1].

Power management IC are one of today's important and necessary part of technological devices because trend is being more mobile. Inside power management chips, buck converter occupies a large and important function. The thesis focused on layout basics, advanced layout strategies and layout of a buck converter.

### 1.1 Organisation of Thesis

Thesis is organized and summarized as below:

Chapter 2 covers production flow of a chip and explaines how a transistor is fabricated. Process steps are briefly covered.

In Chapter3, basic layout structures are given. Layouts of CMOS, diode, BJT and passive devices are explained with cross-sections of related devices.

Chapter 4 covers isolation schemes regarding layout. Isolation can be maintained in fabrication step and layout structures when designing layout. Various types of isolation strategies are explained in detail.

In Chapter 5 issues relating layout design are explained. These problem might cause serious functionality problem of chip. How these issues emerge and how to prevent or minimize them are given.

Chapter 6 dives into layout design. Most important type of layout design is matching between devices. This chapter explaines how matching can be done from basic to advance styles.

In Chapter 7 analog blocks of buck converter are explained briefly and layouts of these blocks given in detail with applies layout strategies explained in previous chapters.

Chapter 8 explains a specific tool used to analyse metallization of buck converter in detail.

Finally, Chapter 9 summaries the overall work done in this thesis and suggests future works to improve more.

### 1.2 The Purpose of Thesis

The aim of this thesis is to create an idea of what "layout" is, why it is needed and how to do as correct and best as possible. This includes basic principles of production flow which produces IC. Production limitations, unwanted side-effects of process, offsets which can be systematic or random will all be covered and solutions to minimize or get rid of these effects will be explained. At the end, techniques to solve these issues will lead to a proper and advanced layout knowledge.

#### 2. MANUFACTURING OF A MOSFET

#### 2.1 Fabrication

CMOS integrated circuits are fabricated on thin circular slices of silicon called wafers. Each wafer contains hundreds or even thousands of individual chips or "die" (Fig. 1.1). For production purposes, each die on a wafer is usually identical. Wafer sizes also differ from 150mm – 300mm. The most common wafer size (diameter) in production is 300mm (12 inch) and 200mm (8 inch) is in second place. In addition to existing wafer sizes, 450mm wafer size production is projected to come alive in following years [2].

The production of silicon wafers constitues only the first step in the fabrication of ICs. Many of the remaining steps deposit materials on the wafer or etch them away. A technique called photolithography allows photographic reproduction of patterns that can be used to selectively block depositions or etches. IC fabrication makes extensive use of photolithography.

A CMOS integrated circuit is fabricated by repetitively applying photolithography to build the necessary structural layers which creates the layout and at the end the chip. Photolithography begins with the application of a photosensitive emulsion called a photoresist (PR). PR is sensitive to certain wavelengths of light. First, the wafer is coated with PR then mask which defines a particular area is applied on PR with using ultraviolet light. Areas on PR exposed to UV can become polymerized depending on the type of PR applied. When the wafer is flooded with solvent, desired areas wash away and other areas remain coated with PR. This technique allow certain areas to be implanted while protecting undesired area with PR [3]

Every layer in the fabrication is done on the same basis by applying PR, exposing UV light, Repetation of this process builds the necessary structural layers.

#### 2.2 CMOS Fabrication Process

Different type of production flows exit but this thesis will consider state of art techniques to fabricate CMOS.

If we analyze CMOS processes, we find that there are four basic layer types [3-13]:

1-Conductors: These layers are conducting layers in that they are capable of carrying signal voltages or currents. Diffusion areas, metal and polysilicon layers, and well layers fall into this category.

2-Isolation layers: These layers are the insulator layers that isolate each conductor layer from each other in vertical and horizontal directions. This isolation is required in both the vertical and horizontal direction to avoid "short circuits" between separate electrical nodes.

3-Contacts or vias: These layers define cuts in the insulation layer that separates conducting layers and allow the upper layer to contact down through the cut or "contact" hole. If this cut connects two same material of conductor then it is called "via". If cut connects different type of conductor material, it is called contact. For example, connection between metal1 to metal2 is called "via" if metal1 and metal2 is made up of copper. Openings in the passivation layer for pads are called "contact" because it connects copper to aluminium. At the end, both "via" and "contact" serve the same purpose, connecting one layer to another.

4- Implant layers: These layers do not explicitly define a new layer or contact, but customize or change existing conductor propriety. For example, diffusion or active areas for PMOS and NMOS transistors are defined simultaneously. A P+ mask is used to create P+ implant areas that define certain diffusion areas to P-type by the use of a P-type implant.

Using a combination of these four types of layers, transistor devices, resistors, capacitors, and interconnections are created.

Fabrication process can be summarized briefly as below:

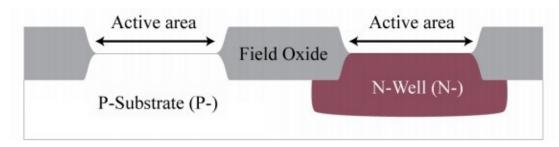

Well formation stage: Implants n-type impurities into the wafer followed by diffusing the impurities deep into the substrate to form the N-Wells. For CMOS process, the silicon substrate is usually p-type. (Figure 2.1)

Figure 2.1: Well formation stage [14].

Active & isolation stage: Thick oxide is grown outside the active areas. Active areas are defined as areas where the CMOS transistors are fabricated. Thick oxide (TOX) is also known as field oxide (FOX). Field oxides isolate the transistors from one another. (Figure 2.2)

**Figure 2.2 :** Active and isolation stage [14].

The first two steps describe a formation of a conventional well. The depth and doping profile of a conventional well are controlled by the diffusion drive-in at high temperature. A better way to form the well is usually used in  $0.25\mu m$  and smaller process technologies (A process technology of  $0.25\mu$  means that the shortest channel length (L) of a transistor is  $0.25\mu m$ .). It is called ion implamentation. It is done by very high energy implantation. The depth and doping profile of a well are controlled by implantation energy and impurity dose. This is formed after the field oxide. Since this does not require diffusion drive-in, it has smaller lateral diffusion and a more ideal doping profile.

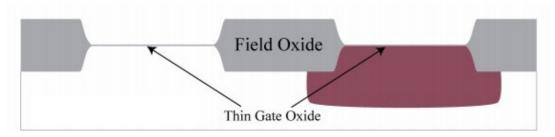

Gate oxide formation stage: A thin gate oxide is grown across the wafer. Gate oxide of only tens of silicon oxide atoms thick is created during the fabrication process with the current technology. Gate oxide is the insulator between the transistor's gate

and its channel. Gate oxide refers to the "O" in "MOS" which stands for Metal-Oxide Semiconductor. (Figure 2.3)

Figure 2.3: Gate oxide formation stage [14].

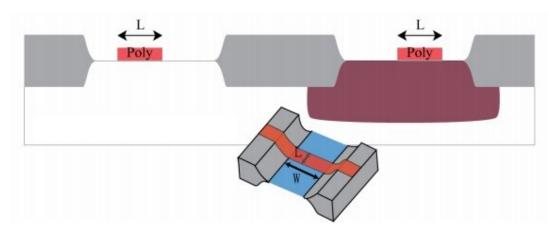

Gate formation stage: Poly (i.e. poly-silicon) is deposited on the wafer. The poly that are deposited on the gate oxides are the gates of the transistors which are usually known as gate poly. The gate poly will incline upward when it extends over the field oxide. The gate oxide in the active area that are not covered by the gate poly will be etched away to form the source and the drain of the transistor. (Figure 2.4)

**Figure 2.4 :** Gate formation stage [14].

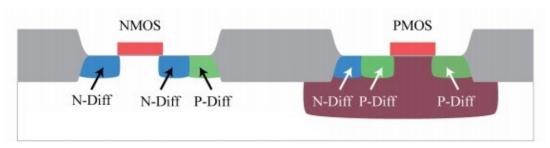

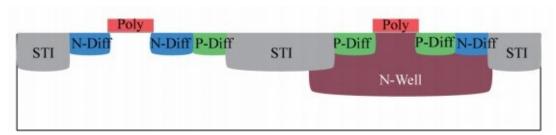

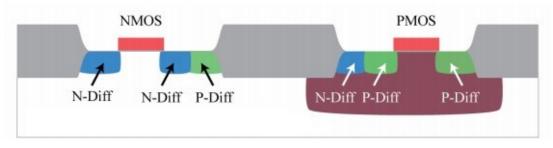

Source and drain formation stage: P-type and n-type impurities are implanted into the active areas. The impurities are diffused into the silicon to form the source terminals and the drain terminals. As the impurities diffuse both vertically and laterally, the gate poly will slightly overlap the sources and the drains which will result in gate overlap capacitances. The diffusions for the sources and the drains of NMOS and PMOS are N-diffusion (N-diff) and P-diffusion (P-diff) respectively. (Figure 2.5)

**Figure 2.5 :** Source drain formation stage.

P-diff in p-substrate is known as p-tap, while n-diff in N-well is known as n-tap. Connections from the metal routings to the substrate and the Nwells are made through the p-tap and the n-tap. This is necessary to ensure the wells are properly tied down and the transistors are isolated. The p-substrate should be biased to the lowest voltage potential while the N-well should be biased to the highest voltage potential. In this way, all the P-N junctions are reverse biased and hence the transistors are electrically isolated from one another

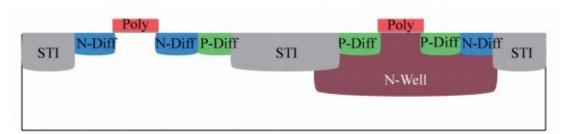

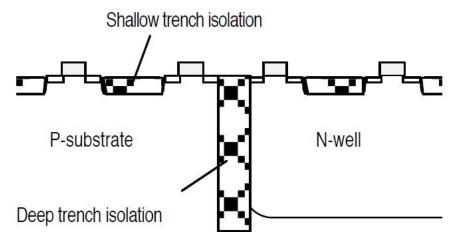

Isolating the transistors with the thick field oxide is commonly found in 0.35µm and larger process technologies. For 0.25µm and smaller process technologies, shallow trench isolation (STI) shown in the diagram below is more commonly used to isolate the transistors. (Figure 2.6) In STI fabrication, trenches are etched into the wafer and filled with silicon oxide to isolate the islands of transistor active area.

**Figure 2.6:** Shallow trench isolation.

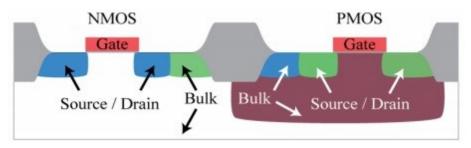

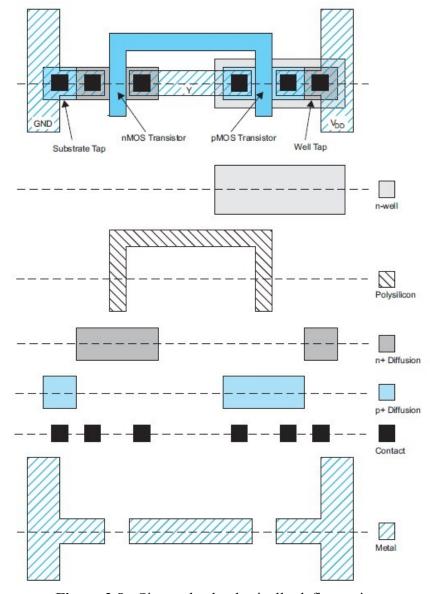

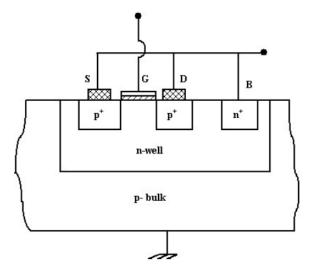

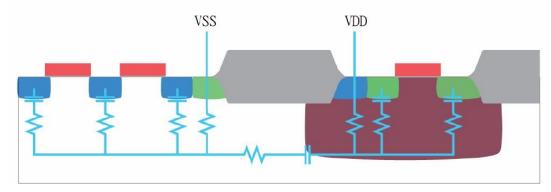

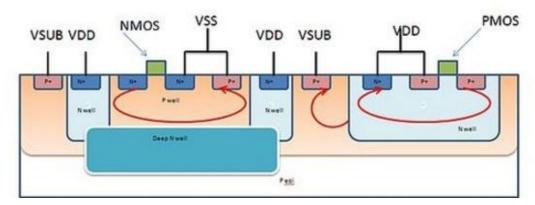

Following the basic process steps, it can be concluded that the drain and the source are fabricated in the same way. In Figure 2.7, overall CMOS layout structure which contains NMOS and PMOS can be observed. With this observation, The bulk of all the NMOS are connected together. The bulk of all the PMOS in the same N-well are connected together.

Figure 2.7: NMOS and PMOS layout cross section.

Figure 2.8 shows simple mask steps that creates an inverter.

Figure 2.8: Six masks that basically define an inverter.

#### 3. BASIC LAYOUT STRUCTURES

## 3.1 CMOS Layout Structure

In a schematic view of a basic inverter, with its input, output, substrate, supply and ground pins. Input pin means that a signal is entering the designated circuit or block. Output is the result of the circuit after it does its job. Substrate pin is generally serves same as ground pin. In contrast, its purpose is separation of ground and substrate paths, so any parasitics do not couple through ground. Ground is the lowest potential in the circuit, block or chip. In general its notations are VSS, AVSS (Analog VSS), DVSS (Digital VSS), GND. Supply pin is the highest potential in the circuit, block or chip. Its notations vary differently but most common types are VDD, AVDD (Analog VDD), DVDD (Digital VDD) or small letters of same notations. Naming convention of ground and supply pins should be consistent all over chip and subblocks but depending on purpose, more than one supply or ground can exist.

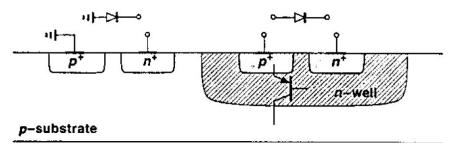

### 3.2 PN Diode Layout

Two types of PN junctions can be formed in a standart CMOS technology: one in the p-substrate and another in an n-well in Figure 3.1. PN junction done by using p-substrate itself is not possible to use as diode. To allow current to flow, PN diode needs to work in forward biased mode. Forward biased PN diode in p-substrate means current is injected to substrate. This will cause substrate potential to rise which leads to unexpected, uncontrolled malfunctions in chip [7].

Figure 3.1: Pn-diode structures.

The diode formed in an n-well also faces difficulties if forward biased. P<sup>+</sup> region in the n-well, the n-well itself, and the p-substrate constitute a bipolar pnp transistor whose collector is typically grounded. Thus, if the pn junction in the n-well is forward biased, substantial current flows from the p<sup>+</sup> terminal to the substrate. In other words, the structure must not be viewed as merely a two-terminal floating diode.

### 3.3 BJT Layout

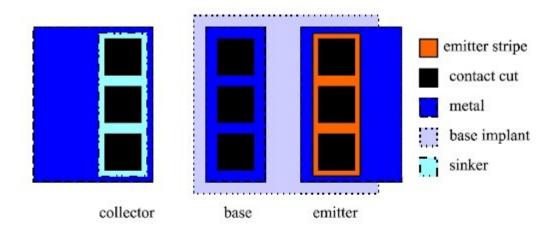

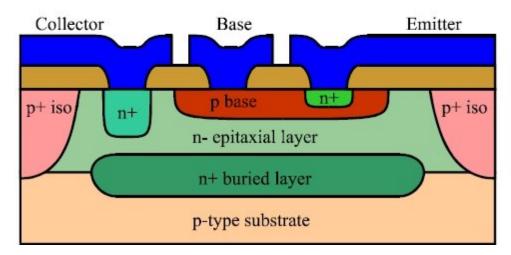

Since this thesis only considers CMOS technology, other types of transistors are not explained. However, it is good to have brief layout knowledge about BJT since BJT and MOSFET have similar but not identical operational behaviours. In Figure 3.2, top-view of BJT and cross-section of it can be analysed. Structure heavily relies on pn structures as one level of layer on top of other.

Figure 3.2: Top view and cross-section of BJT layout.

### 3.4 Resistor Layout

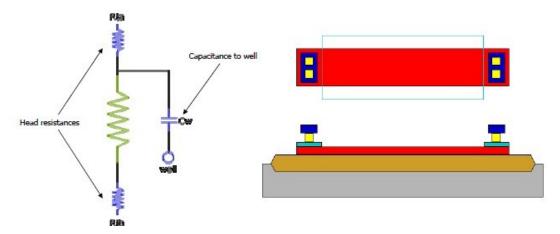

A CMOS process may be modified so as to provide resistors suited to analog design. A common method is to selectively "block" the silicide layer that is deposited on top of polysilicon, thereby creating a region having resistivity of the doped polysilicon, in Figure 3.3. This means the fabrication requires an additional mask and corresponding lithography sequence [15]

The use of silicide on the two ends of the resistor results in a much lower contact resistance than that obtained by directly connecting the metal layer to doped polysilicon. Also polyresistors typically exhibit much less capacitance to substrate than other types.

Other types of resistor structures are double poly resistor (which is not used in modern fabrication process because only one poly options are available), metal resistor which relies on sheet resistance of metal line hence having low resistance values compared to poly resistor. Nwell resistor is also available but its resistivity may vary large with process so not used in applications where resistor value is critical. Depletion region formed between n-well and p-substrate, nwell resistors suffer from large parasitic capacitance

**Figure 3.3:** Resistor model (left), top-view (top) and layout (bottom) of a resistor.

### 3.5 Capacitor Layout

Capacitors prove indispensable in most of today's analog CMOS circuits. Several parameters of capacitors are critical in analog design: nonlinearity (voltage dependence), parasitic capacitance to the substrate, the series resistance and capacitance per unit area (density). In CMOS technologies modified for analog design, capacitors are fabricated as metal-insulator-metal capacitor (MIM), metal-on-metal capacitor (MOM) and mosfet's used as capacitor by drain and source are connected together to form one side plate and gate forms the other side plate.

## 3.5.1 MOS capacitor

Metal-oxide semiconductor capacitor (MOSCAP) as name implies made by using either PMOS or NMOS transistors. It is done by connecting drain and source to same net and voltage and gate to another. Thin oxide under polysilicon (gate) and channel that it formed underneath it by drain and source side can be used as a capacitor. In order to form channel, transistors has to be biased in accumulation or strong inversion mode [16].

MOS capacitor has a structure that drain, source and bulk (D, S, B) of a PMOS transistor tied together (D=S=B) corresponds to one plate, while the polysilicon gate creates the other plate. This structure depends on the gate-bulk voltage  $V_{BG}$ . The MOS capacitor is shown in Figure 3.4. In the case of PMOS capacitor, an inversion channel with mobile holes builds up for  $V_{BG} > |V_T|$ , where  $|V_T|$  is the threshold voltage of the transistor.  $V_{BG} >> |V_T|$  guarantees the MOS capacitor works in the strong inversion region. However, for the value of the voltage  $V_G > V_B$ , the device enters the accumulation region, where the voltage at the interface between gate oxide and semiconductor is positive and high enough to allow electrons to move freely. The value of the MOS capacitance, CMOS in the strong inversion and accumulation region is at its maximum, and is equal to

$$C_{ox} = \varepsilon_{ox} \left( \frac{L.W}{t_{ox}} \right) \tag{3.1}$$

where LxW is the transistor channel area and  $t_{ox}$  is the gate oxide thickness.

**Figure 3.4 :** MOSCAP layout cross-section [16].

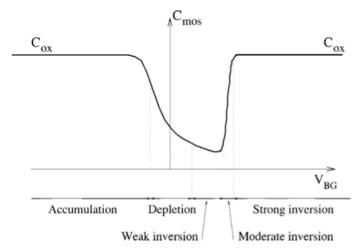

Three more regions exist for the intermediate values of  $V_{BG}$ : moderate inversion, weak inversion, and depletion. In these regions there are few or very few mobile carriers at the gate oxide interface that decreases the capacitance of the MOS device. Capacitive versus  $V_{BG}$  characteristics of a MOS capacitor is shown in Figure 3.5.

**Figure 3.5 :** Capacitive versus V<sub>BG</sub> characteristics of a MOS capacitor [16].

Benefit of using MOSCAP is; process does not require additional masks to produce so makes it cost effective and can be placed everywhere as it does not need any special care in contrast to analog block layouts.

Downside of using MOS transistor as a capacitor is MOS capacitors have high parasitic resistance. This resistance comes from both channel resistance and the resistance of the metal plates. Other drawback of using MOS cap is as explained before; in order to achive a capacitance value, MOS transistor has to be biased in

accumulation or strong inversion modes and design should guarentee that these biasing does not change.

### 3.5.2 MIM capacitor layout

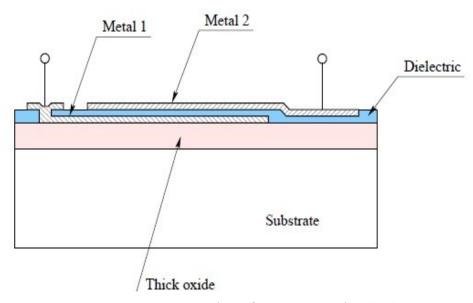

A MIM capacitor consists of two metal layers (plates) separated by a deposited dielectric layer. A cross section of a MIM capacitor is shown in Figure 3.6. A thick oxide layer is typically deposited on the substrate, reducing the parasitic capacitance to the substrate. The parasitic substrate capacitance is also lowered by utilizing the top metal layers as plates of a MIM capacitor. The capacitance density can be increased by reducing the dielectric thickness and employing high-k dielectrics [17-19].

**Figure 3.6 :** Cross section of a MIM capacitor [17]

In today's IC fabrication, MIM capacitors are done on top metal and one metal below top metal, to reduce substrate capacitance which is undesired. In addition to this, by using extra process steps and masks MIM cap is created in to special layers which are not used as metal in design. They are called Capacitor Top Metal (CTM) and Capacitor Bottom metal (CBM). In order to do that additional process step and masks are required which increases the fabrication cost of a chip. Figure 3.7 and Figure 3.8 depicts widely used MIM capacitor cross-section.

Figure 3.7: MIM capacitor consisting of CTM and CBM layers [18]

Figure 3.8: Another view of MIM capacitor.

# 3.5.3 Metal - on - metal (MOM) capacitor layout

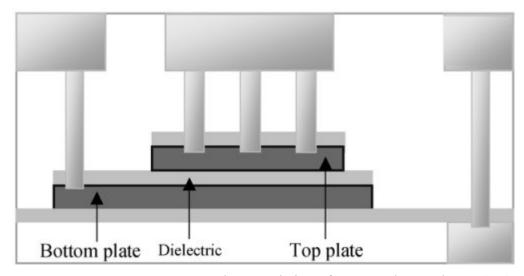

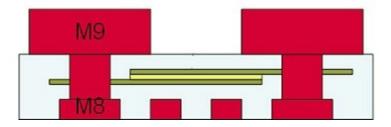

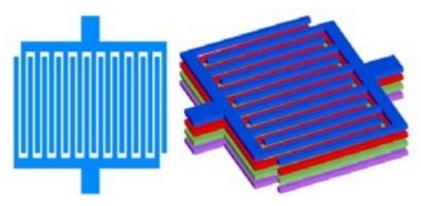

The total capacitance per unit area can be increased by using more than one pair of interconnect layers. Current technologies offer up to ten metal layers, increasing the capacitance nine times with a sandwich structure. The capacitance is further increased by exploiting the fringe capacitance between the adjacent metal lines within a special interconnect layer. In scaled technologies, the adjacent metal spacing (on the same level) shrinks faster than the spacing between the metal layers (on different layers), resulting in substantial lateral coupling. It is same in vertical capacitance between two metal layers, Figure 3.9 gives top and angled view of MOM capacitors.. By using fingered and stacked metals from bottom to allowed top metal, we can increase capacitance as much as possible.

Figure 3.9: MOM capacitor view [20].

## 3.6 Electromigration

Electromigration is the gradual displacement of metal atoms in a semiconductor. It occurs when the current density is high enough to cause the drift of metal ions in the direction of the electron flow, and is characterized by the ion flux density. This density depends on the magnitude of forces that tend to hold the ions in place, i.e., the nature of the conductor, crystal size, interface and grain-boundary chemistry, and the magnitude of forces that tend to dislodge them, including the current density, temperature and mechanical stresses [21]

In another way, under the conditions of high current densities and high temperatures in metals, there is momentum transfer between conducting electrons and diffusing metal atoms. This causes gradual drift of the ions in the metal in the direction of electron flow and result in mass transport. This process of material transfer is called Electromigration(EM).

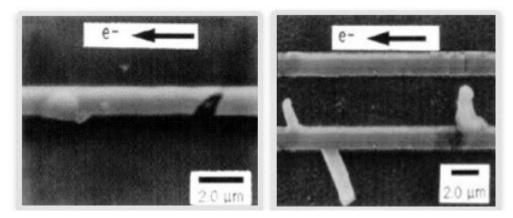

The effect of EM in integrated circuits is open circuit(void) or short circuit(Hillock) failures shown in Figure 3.10.

The mean time to failure(MTTF) of an interconnect is the expected time that it will operate before the first failure. MTTF of the interconnect under constant current stress and temperature, subjected to EM affects, is given by Black's equation as

$$MTTF = \frac{A}{J^n} e^{(\frac{E_a}{kT})}$$

(3.2)

where

$E_a \rightarrow$  Activation energy for failure(0.5 to 0.7 eV for Al)

$A \rightarrow$  Constant based on the cross-sectional area of the interconnect

$J \rightarrow$ Current density in the metal interconnect

$n \rightarrow$ Constant vary between  $1 \sim 7$  (usually set to 2 acording to Black)

$k \rightarrow Boltzmann constant$

$T \rightarrow \text{Temperature in Kelvin } (K^{\circ})$

Figure 3.10: EM failure types, open circuit (left), short circuit (right) [21].

The formula indicates that temperature and current density are the key factors that contribute to electromigration mechanism. The temperature of the conductor appears in the exponent, i.e. it strongly affects the MTTF of the interconnect. For an interconnect to remain reliable as the temperature rises, the maximum tolerable current density of the conductor must necessarily decrease.

Electromigration, eventually determines the current capability of an interconnect metal in process. A quote taken from one of the foundaries' design rule document states that " $I_{max}$  is the maximum DC current allowed for metal lines, vias,, or contacts. Imax is based on 0.1% point of measurement data at a 10% resistance increase after 100K hours of continuous operation at  $110^{0}$ C." [22].

To explain more in depth, failure level of an interconnect is set to 10% increase in resistance and this must be achieved at least 100.000 hours of continuous operation with temperature in  $110^{0}$ C. If design requires a working temperature more or less than  $110^{0}$ C, then foundary gives a rating factor to convert standart  $110^{0}$ C  $I_{max}$  value to desired temperature.

Rating factor of  $I_{max} \rightarrow 2.33$  (at  $\le 85^{\circ}$ C), 1.38 (at  $100^{\circ}$ C), 1.17 (at  $105^{\circ}$ C), 1 (at  $110^{\circ}$ C), 0.735 (at  $120^{\circ}$ C), 0.633 (at  $125^{\circ}$ C)

For instance:  $I_{max}$  (at  $125^{\circ}C$ ) =  $0.633xI_{max}$ (at  $110^{\circ}C$ )

There is also a term called  $I_{peak}$  exits.  $I_{peak}$  is the current at which a metal line undergoes excessive Joule heating and can begin to melt. Thus,  $I_{peak}$  should not be a limit to current density as reaching  $I_{peak}$  value means interconnect metal will not work and cause vital errors.  $I_{peak}$  value can vary 30-60 mA per width. Detailed information about this can be found in foundary's design rule document.

The  $I_{peak}$  rule applies to periodical AC or pulsed DC signals that has a pulse width of less than 1msec.

$I_{peak}$  of contact and vias are not included because the heating in contacts and vias is negligible and is usually determined by metal or substrate.

### 3.7 Electromigration Dependency On Physical Effects

### 3.7.1 Temperature

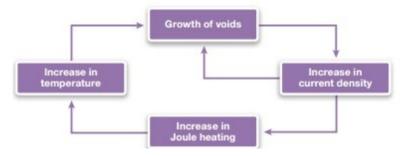

From Black's equation, it is clear that failure due to electromigration is dependent on temperature; however, there is a more sinister dependence on temperature that accelerates failures due to voids. Figure 3.11 highlights a cyclical positive feedback loop that ultimately ends in failure

**Figure 3.11 :** Electromigration dependency on temperature [21].

Once a void begins to develop in a metal wire, the wire itself becomes narrower at that point. Due to the reduction in width, the current density increases and, therefore, the interconnect temperature increases due to Joule heating. Joule heating is a result of root-mean square (RMS) current. As the temperature of the wire increases, the growth of the void accelerates, and eventually an open circuit occurs. This is why it is critical to also take RMS current into account when performing EM analysis

### 3.7.2 Wire width and current density

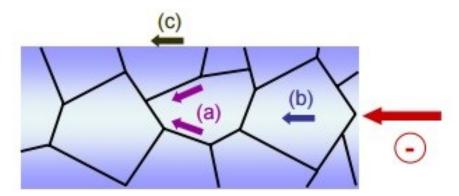

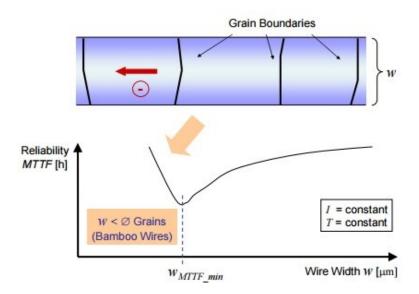

Current density is the primary factor influencing electromigration. Wider metal lines have lower current density for the same current, hence have high resistance to electromigration. There is one exception to this rule and that is when the wire width falls below the average grain size of the interconnect material. This apparent contradiction is caused by the position of the grain boundaries (Figure 3.12), which in such narrow wires lie perpendicular to the width of the whole wire. Because the grain boundaries in these so-called "bamboo structures" are at right angles to the current, the boundary diffusion factor is excluded, and material transport is correspondingly reduced (Figure 3.13) [23].

Figure 3.12: Illustration of various diffusion processes within the lattice of an interconnect: (a) grain boundary diffusion, (b) bulk diffusion, and (c) surface dissusion [23]

**Figure 3.13 :** Reduced wire width below the avarage grain size increases the reliability of the wire with regard to electromigration [23]

So-called bamboo wires are characterized by grain boundaries which lie perpendicular to the direction of the electron wind and thus permit only limited grain boundary diffusion.

However, the maximum wire width possible for a bamboo structure is usually too narrow for signal lines of large-magnitude currents in analog circuits or for power supply lines. In these circumstances, slotted wires are often used, whereby rectangular holes are carved in the wires. Here, the widths of the individual metal structures in between the slots lie within the area of a bamboo structure, while the resulting total width of all the metal structures meets power requirements.

## 3.7.3 Wire length

There is also a lower limit for the length of the interconnect that will allow electromigration to occur. It is known as "Blech length", and any wire that has a length below this limit (typically in the order of 10-100 µm) will not fail by electromigration. Here, a mechanical stress buildup causes a reversed migration process which reduces or even compensates the effective material flow towards the anode. Specifically, a conductor line is not susceptible to electromigration if the product of the wire's current density J and the wire length l is smaller than a process technology-dependent threshold value (J·l)

#### 3.8 IR Drop

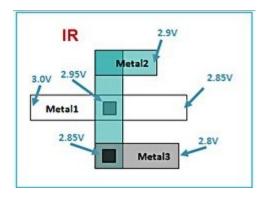

The Power supply in the chip is distributed uniformly through metal layers (Vdd & Vss) across the design. These metal layers have finite amount of resistance. When voltage is applied to this metal wires current starts flowing through the metal layers and some voltage is dropped due to that resistance of metal wires and current. this drop is called as IR drop. Highest and one below highest metal are used for power and ground routing in chip level layout. These metals are thicher and wider than lower metals thus reducing metal resistance for power rails or inductors.

IR drop is an unwanted drop in voltage caused by current through a metal wire. It is so named because voltage (V) = current (I) \* resistance (R). An unexpected voltage drop on an instance or a device can cause a functional failure because the lowered voltage supply may not be strong enough to switch the instance, or may switch it too slowly.

IR drop is signal integrity (SI) effect caused by wire resistance and current drawn off from power(Vdd) and ground (Vss) grids. According to ohms law, V=IR. If wire resistance is too high or the current passing through the metal layer is larger than the predicted, an unacceptable voltage drop may occur. Due to this unacceptable voltage drop, the power supply voltage decreases. That means the required power across the design is not reaching to the cells. This results in increased noise susceptibility and poor performance.

The design may have different types of gates with different voltage levels. As the voltage at gate decreased due to unacceptable voltage drop in supply voltage, the gate delays are increased non-linearly. This may lead to setup time and hold time violations depending on which path these gates are residing in the design.

As technology node shrinking, there is decreased in the geometries of the metal layers and the resistance of this wire increased which lead to decrease in power supply voltage during CTS, the buffers and inverters are added along the clock path to balance the skew. The voltage drop on the buffers and inverters of clock path will cause the delay in arrival of clock signal, resulting hold violation.

Signal carries both voltage and current, however depending on signal type, voltage value or current might be more important than other might. This affects the layout of the circuit. If current is more crucial, layout need some calculations whether metal line that carries current is enough wide to handle that much of current. If voltage is critical than IR drop is needed to be taken into consideration, Figure 3.14. Note that voltage equals current times resistance (V= I\*R). In addition to that if signal is sensitive some shielding strategies should be applied. These will be explained later in thesis.

**Figure 3.14 :** IR drop in layout.

#### 4. ISOLATION SCHEMES

Isolation techniques protect circuit from noise or prevents noise to couple other blocks or devices. First part is isolation of device itself. In that part, isolation is achieved on fabrication process.

As different circuits/blocks behave differently and prone to different effects, an isolation strategy should be build to protect them which is explained in second part, isolation in layout

#### 4.1 Isolation of Device in Fabrication Process

To avoid electrical shorts between the closely placed MOS transistors, the electrical isolation of the MOS from all sides is a must. Usually, silicon dioxide (SiO2) is used for this purpose. SiO2 has the advantage that it can be easily etched, besides being process compatible; and it can be grown or deposited easily compared to other dielectric materials. There are many oxide-based isolation schemes, but the three most popular oxide isolation schemes, namely, thick oxide isolation, Local Oxidation of Silicon (LOCOS) isolation and shallow trench isolation.

Thich Oxide isolation suffers from high vertical oxide step at the edge of the field-oxide and active areas. This sharp vertical oxide step creates proclems for subsequent MOS fabrication steps. In additon, the silicon area is more consumed then other two schemes. Furthermore, in the thick oxide isolation scheme, the transistrs are isolated from the top of the wafer surface, but not from bottom of the silicon wafer. For these reasons, the thick oxide isolation scheme is not used in MOS fabrication process.

#### 4.1.1 Local oxidation of silicon (LOCOS)

LOCOS has been used extensively for  $0.35\mu$  or larger minimum linewidth CMOS technologies.

A thick oxide layer is grown by the oxidation process [24]. The thick oxide is called Field Oxide (FOX). These FOX areas are used for MOS isolation. By laying nitride film on top of active areas, oxygen atoms cannot diffuse through the nitride film;

thus, no oxide is formed in the active areas. This eventually leads to the local oxidation of the silicon wafer. That is why process called local oxidation of silicon (LOCOS). FOX is not sharp vertical, but slanted inside the active.

In the LOCOS isolation scheme, the MOS transistors are isolated form the top as well as bottom of the wafer to some extend. The LOCOS oxide has gentle slope between the FOX and the active areas with less oxide height [25].

Unfortunately, the LOCOS scheme suffers from loss of silicon due to a "bird's beak" formation, Figure 4.1. The bird's beak is formed due to lateral diffusion of oxygen atoms inside the active regions, resulting in the oxidation of the silicon. The bird's beak encroaches into the active area, thereby reducing the achievable circuit packing density. The effective channel width of the transistor is affected by the bird's beak. Moreover, LOCOS requires a long, high-temperature process, which can result in significant diffusion of previously introduced dopants.

Figure 4.1: Bird's beak and its effect on device width [14].

Figure 4.2: LOCOS formation in NMOS and PMOS cross-section.

In Figure 4.1 can be seen that due to oxide growth in LOCOS, expansion is upwards and downwards through substrate and Figure 4.2 shows FOX with NMOS and PMOS layout cross-section.

#### 4.1.2 Shallow trench isolation

Shallow trench isolation (STI), is an integrated circuit feature which prevents electric current leakage between adjacent semiconductor device components. STI is generally used on CMOS process technology nodes of 0.25µ and smaller [26-31].

STI is created early during the semiconductor device fabrication process, before transistors are formed. The key steps of the STI process involve etching a pattern of trenches in the silicon, depositing one or more dielectric materials (such as silicon dioxide) to fill the trenches, and removing the excess dielectric using a technique such as chemical-mechanical planarization (CMP).

Advantage of using STI is deeper isolation between devices. Filled trenches also called Field oxide. Disadvantage of STI is mechanical stress on device which affects the performance. This effect is called STI Proximity effect or Length of Diffusion (LOD) effect which will be explained in further chapters.

Figure 4.3: STI formation of NMOS and PMOS cross-section.

The mechanical stress of STI on device is first noticed in  $0.13\mu$  node and later on smaller nodes this became a dominant factor, in order to to balance or minimize STI proximity effect some layout structures are used. These will be explained in further chapter.

Figure 4.3 shows STI formation, this formation has more planar surface than LOCOS formation with help of CMP.

## **4.2** Isolation in Layout

Analog design performances are sensitive to electrical disturbance as known as noise. Disturbance (noise) in the substrate should be minimized as much as possible. Two common types of substrate disturbance are

- Disturbance from minority carrier

- Substrate coupling noise

Above subject discusses about noise in terms of layout and further subjects are explained to reduce noise susceptibility.

There are different types and structures for isolation. Nearly all of them can be utilized in layout to achieve best protection, however applying all types and structures come with a cost in either area consumption or additional mask need in fabrication which means more expensive production cost

# 4.2.1 Disturbance from minority carrier

Minority carriers are injected into substrate from source diffusion and the drain diffusion when

- The source potential or the drain potential of NMOS is below the subtrate potential

- The source potential or the drain potential of PMOS is above the N-well potential

There are several possibilities for the above conditions to happen. Examples are

- Inductive ground path causes the ground in the substrate to bounce

- Resistive power and ground path from the power pins to the subtrate and the n-well

- Fast switching with significant overshoot

The drifting of the minority carriers in the substrate and the n-well create a potential difference that can affect the performance of the circuit or trigger a latch-up.

### 4.2.2 Substrate coupling noise

A reverse biased diode has the electrical properties of a capacitor. Circuit signals can be coupled through the substrate as illustrated in the diagram below, Figure 4.4.

Figure 4.4: Substrate coupling noise.

To prevent this coupling guard rings should be utilized. Below, how they work explined and configuration to implement showed.

### 4.2.3 Guard rings

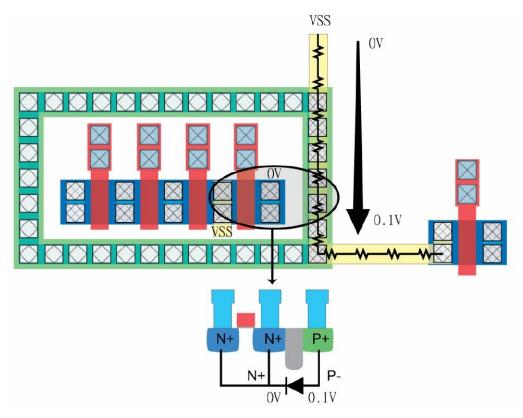

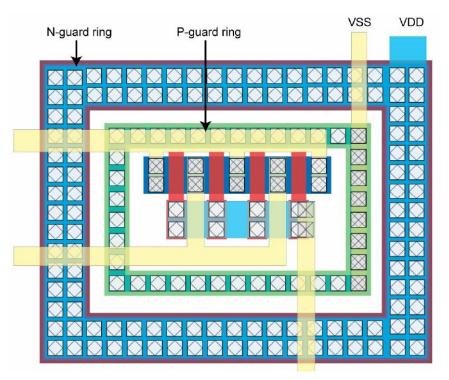

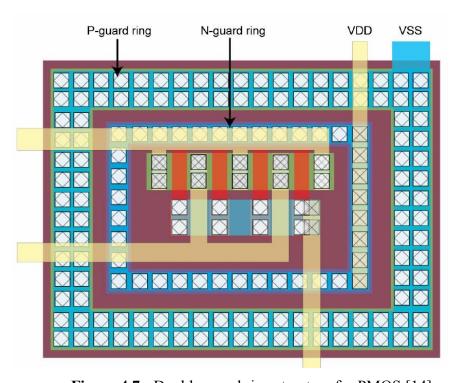

To reduce substrate coupling noise, one may use guard ring in the following configuration around critical transistors.

- Surround NMOS in the p-substrate with p-tap guard ring that is connected to ground.

- Surround PMOS in n-well with n-tap guard ring that is connected to VDD.

To reduce disturbances from minority carrier, one may use guard ring in the following configuration around noisy transistors.

- Surround NMOS in the p-substrate with n-well guard ring. Tie the n-well guard ring to VDD. The n-diffusions from the NMOS could inject stray electrons into substrate. These stray electrons could be collected efficiently by the n-well guard ring that is biased to VDD to attract the electrons.

- Surround the PMOS in the n-well with p-diffusion guard ring. Tie the p-diffusion guard ring to ground. P-diffusions from the PMOS inject stray holes into the n-well. These stray holes could be collected efficiently by the p-diffusions guard ring that is biased to ground to attract the holes.

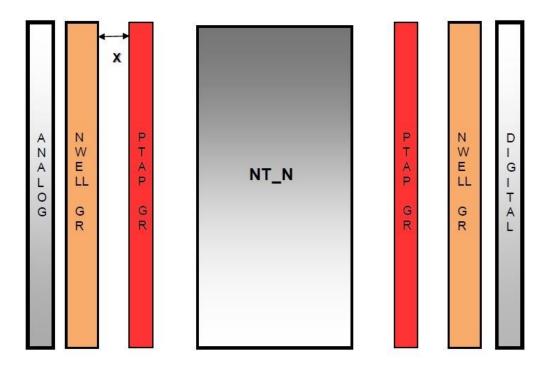

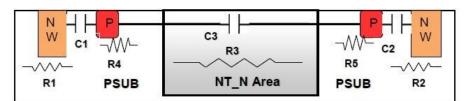

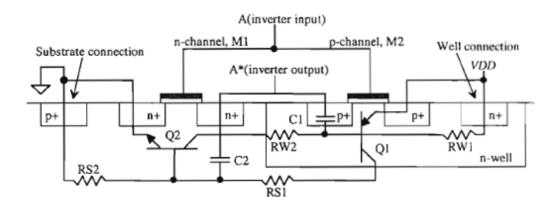

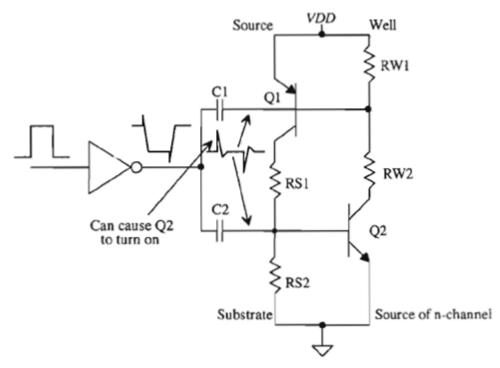

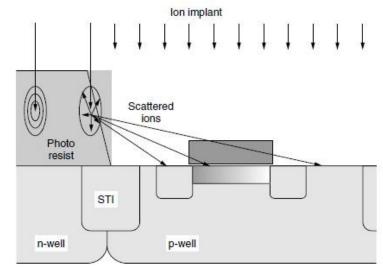

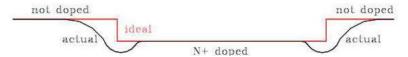

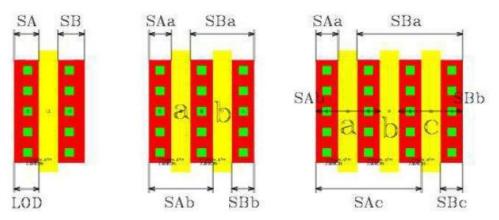

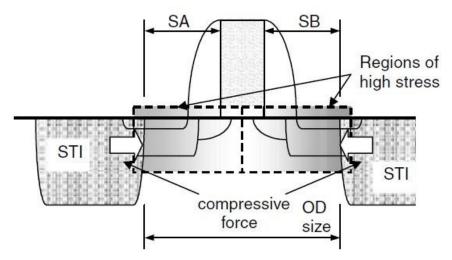

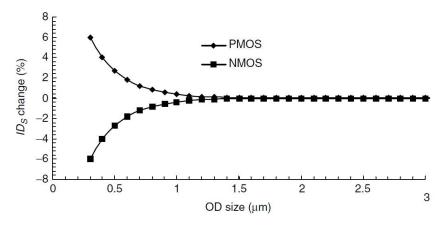

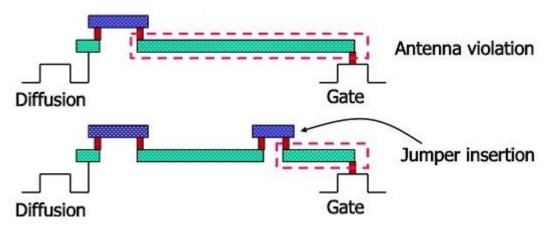

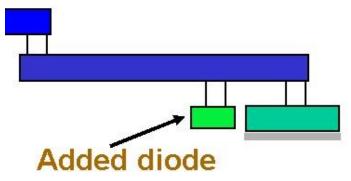

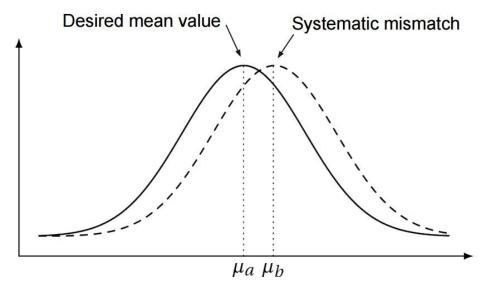

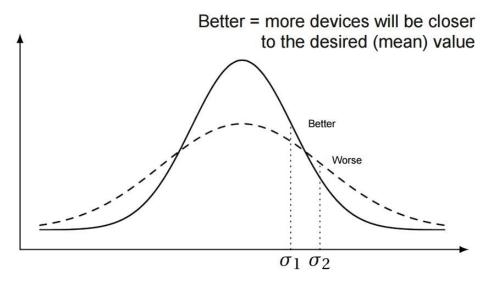

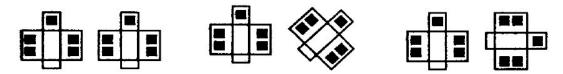

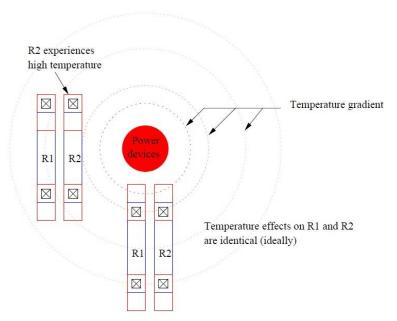

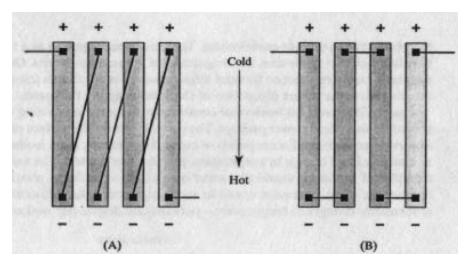

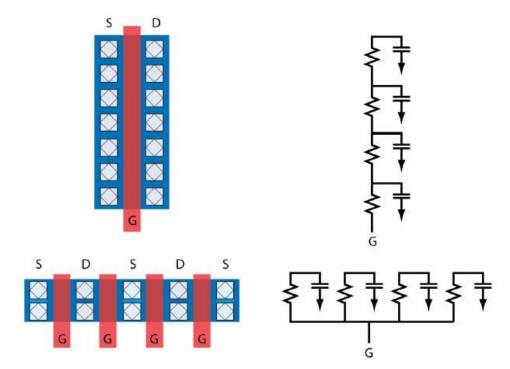

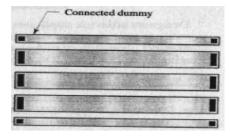

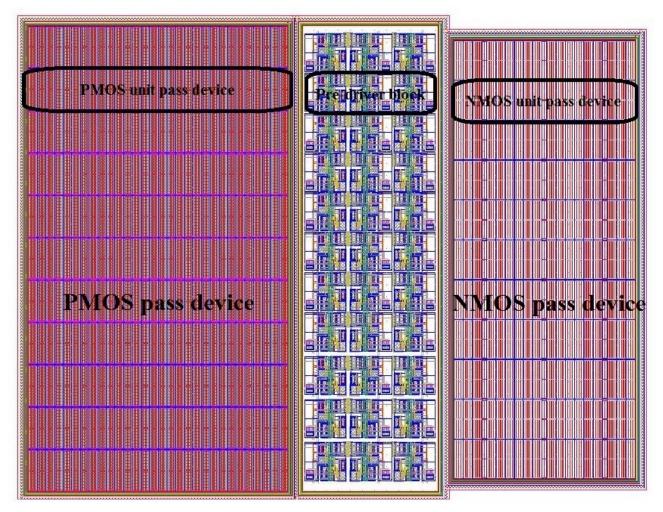

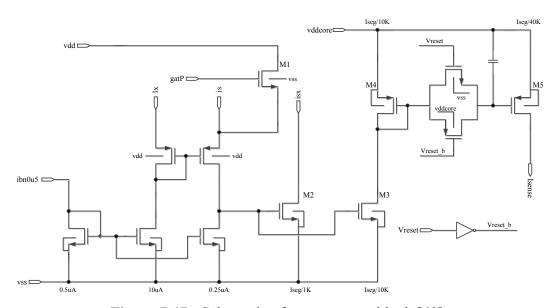

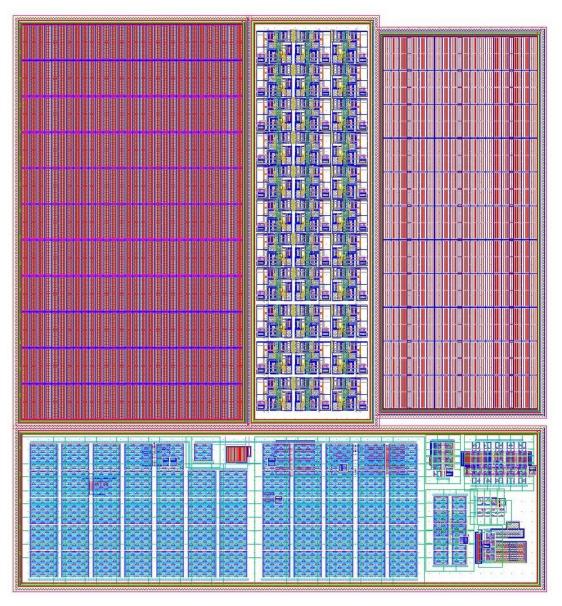

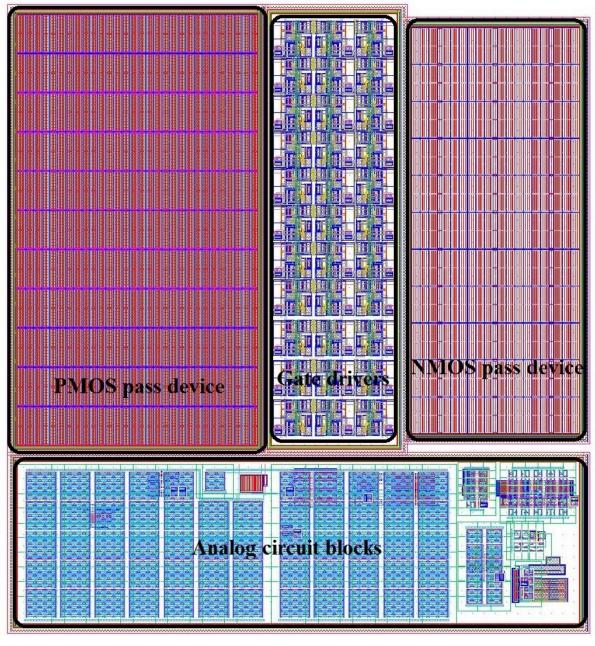

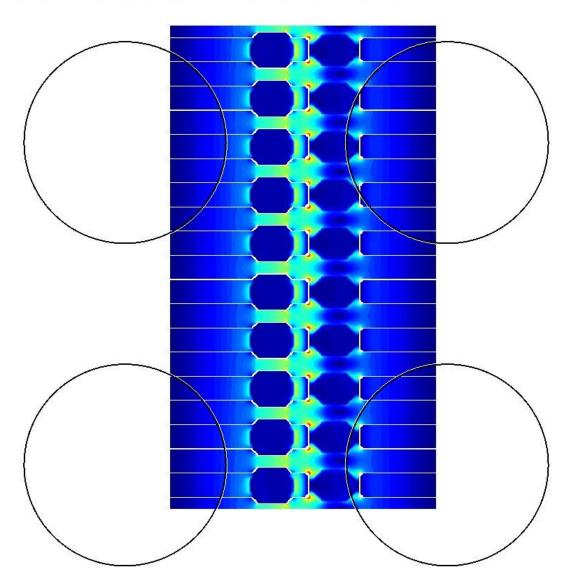

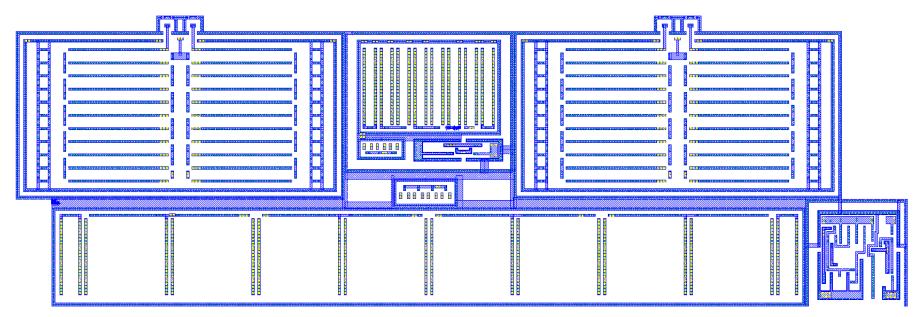

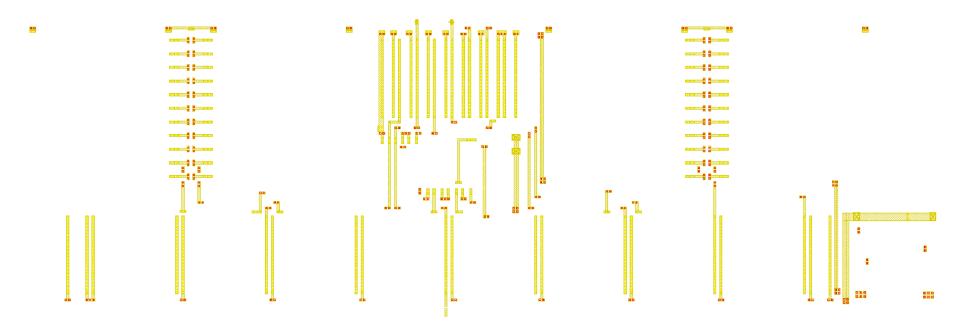

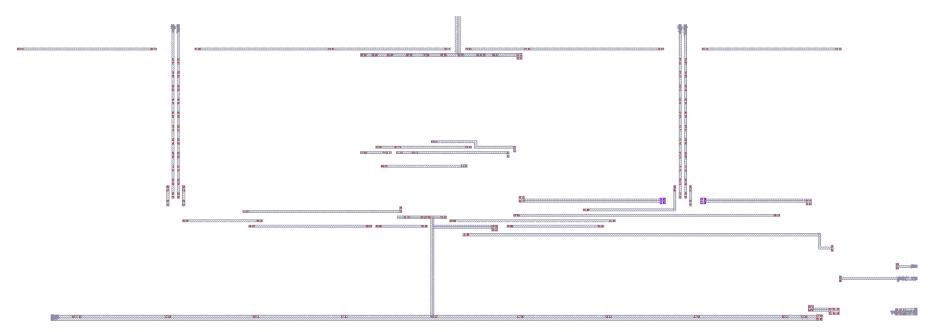

For the guard rings to be effective, the resistance in the path from noise source to the guard ring and then to the voltage source (either VDD or VSS) must be kept as low as possible. Hence guard ring should be made as wide as possible to decrease resistance. Wider guard ring helps to reduce ~5dB extra isolation [76]. Ideally, the guard rings should be placed as closely to the noise sources as possible, closer the guard ring better noise isolation achieved (~7dB better isolation) [76]. The guard rings are also placed around the critical transistors to minimize stray electrons and stray holes from affecting the critical transistors [32]