# <u>İSTANBUL TECHNICAL UNIVERSITY ★ INSTITUTE OF SCIENCE AND TECHNOLOGY</u>

### DESIGN OF A 2.4 GHz LOW POWER LC VCO IN UMC 0.18u TECHNOLOGY

M.Sc. Thesis by Volkan ORHAN, B.Sc.

Department :Electronics and<br/>Communication EngineeringProgramme:Electronics Engineering

**NOVEMBER 2007**

## <u>İSTANBUL TECHNICAL UNIVERSITY ★ INSTITUTE OF SCIENCE AND TECHNOLOGY</u>

### DESIGN OF A 2.4 GHz LOW POWER LC VCO IN UMC 0.18u TECHNOLOGY

M.Sc. Thesis by Volkan ORHAN, B.Sc. 504051223

Date of submission : 31 August 2007 Date of defence examination: 02 November 2007

Supervisor (Chairman): Members of the Examining Committee Prof.Dr. Osman PALAMUTÇUOĞULLARI Prof.Dr. Ali ZEKİ Prof.Dr. Sıddık YARMAN (İ.Ü.)

NOVEMBER 2007

# <u>İSTANBUL TEKNİK ÜNİVERSİTESİ ★ FEN BİLİMLERİ ENSTİTÜSÜ</u>

# 2.4 GHz DÜŞÜK GÜÇLÜ LC VCO TASARIMI

YÜKSEK LİSANS TEZİ Müh. Volkan ORHAN 504051223

### Tezin Enstitüye Verildiği Tarih : 31 Ağustos 2007 Tezin Savunulduğu Tarih : 02 Kasım 2007

| Tez Danışmanı :    | Prof.Dr. Osman PALAMUTÇUOĞULLARI |  |

|--------------------|----------------------------------|--|

| Diğer Jüri Üyeleri | Prof.Dr. Ali ZEKİ                |  |

|                    | Prof.Dr. Sıddık YARMAN (İ.Ü.)    |  |

KASIM 2007

### ACKNOWLEDGEMENTS

I would like to express my gratitude to my supervisor Prof. Dr. Osman PALAMUTÇUOĞULLARI who gave me the possibility to do my thesis in the cooperation with Swiss Federal Institute of Technology-Lausanne (EPFL) and supported me with his guidance and understanding. I am deeply indebted to my other supervisor that is responsible for the RF ICs group at Laboratory LEG of EPFL; Dr. Catherine DEHOLLAIN whose help, stimulating suggestions and encouragement helped me in all the time of research for and writing of this thesis. I would also like to thank to Prakash Thoppay EGAMBARAM for his valuable advice and technical support.

August 2007

Volkan ORHAN

# CONTENTS

| ABBREVIATIONS                                          | vi        |

|--------------------------------------------------------|-----------|

| LIST OF TABLES                                         | vii       |

| LIST OF FIGURES                                        | viii      |

| LIST OF SYMBOLS<br>ÖZET                                | xi<br>xii |

| SUMMARY                                                | xiv       |

| 1. INTRODUCTION                                        | 1         |

| 1.1 Motivation Behind the Work                         | 1         |

| 1.2 VCO Spec-sheet                                     | 2         |

| 1.3 The Design Specifications of the Proposed VCO      | 4         |

| 2. OSCILLATOR BASICS                                   | 5         |

| 2.1 Oscillator as a Feedback System                    | 5         |

| 2.2 Ring Oscillators                                   | 6         |

| 2.3 LC Oscillators                                     | 8         |

| 2.3.1 LC tank                                          | 8         |

| 2.3.2 One-port view of an LC oscillator                | 9         |

| 2.3.3 Cross-coupled LC oscillator                      | 10        |

| 2.3.3.1 NMOS cross-coupled LC oscillator               | 11        |

| 2.3.3.2 CMOS cross-coupled LC oscillator               | 13        |

| 2.3.4 Colpitts Oscillator                              | 15        |

| 3. OSCILLATOR NOISE                                    | 20        |

| 3.1 General Definition                                 | 20        |

| 3.2 Impact of Phase Noise on Transceiver Architectures | 21        |

| 3.3 Phase Noise Models                                 | 22        |

| 3.3.1 Leeson's phase noise model                       | 22        |

| 3.3.2 Lee and Hajimiri's phase noise model             | 26        |

| 3.3.3 F-parameter extraction                           | 32        |

| 3.4 Phase Noise Sources in Cross-Coupled LC VCO        | 32        |

| 3.4.1 Transistor generated noise                       | 33        |

| 3.4.1.1 MOSFET noise sources                           | 33        |

| 3.4.1.2 AM-PM conversion mechanisms                    | 36        |

| 3.4.1.3 Bias generated noise                           | 38        |

| 3.4.1.4 Noise in the switching pair                    | 39        |

| 3.4.2 Tank generated noise                                | 40 |

|-----------------------------------------------------------|----|

| 4. IC INDUCTORS                                           | 42 |

| 4.1 Bond Wire Inductors                                   | 42 |

| 4.2 On-chip Inductors                                     | 42 |

| 4.2.1 On-chip inductor types                              | 43 |

| 4.2.2 Modeling of on-chip inductor                        | 43 |

| 4.2.2.1 Physical model                                    | 44 |

| 4.2.2.2 Narrowband inductance model                       | 45 |

| 5. VARACTORS                                              | 47 |

| 5.1 Diode Varactors                                       | 47 |

| 5.2 MOS Varactors                                         | 48 |

| 5.2.1 General concept of MOS varactors                    | 48 |

| 5.2.2 Inversion mode MOS varactors                        | 50 |

| 5.2.3 Accumulation mode MOS varactors                     | 51 |

| 5.3 Switched Capacitor Array Varactor                     | 52 |

| 6. VCO DESIGN                                             | 54 |

| 6.1 Comparison of Three Cross-coupled Topologies          | 54 |

| 6.1.1 A simple comparison                                 | 54 |

| 6.1.2 A more detailed comparative study                   | 58 |

| 6.1.2.1 Design methodology                                | 58 |

| 6.1.2.2 CMOS cross-coupled LC VCO                         | 59 |

| 6.1.2.3 NMOS cross-coupled LC VCO                         | 62 |

| 6.1.2.4 PMOS cross-coupled LC VCO                         | 63 |

| 6.1.3 On the selection of the convenient topology         | 64 |

| 6.2 Design of the Chosen Topology                         | 65 |

| 6.2.1 Inductor selection                                  | 65 |

| 6.2.2 Bias circuitry design                               | 67 |

| 6.2.3 Tuning circuitry design                             | 68 |

| 6.3 NMOS LC VCO with Resistor Biasing                     | 74 |

| 6.4 Implementation of a Filtering Technique               | 75 |

| 6.5 NMOS LC VCO with Resistive and Inductive Tail Biasing | 77 |

| 6.6 Self-biased NMOS LC VCO                               | 79 |

| 6.7 Implementation of Bias Level Shifting Technique       | 83 |

| 6.8 Differential Colpitts Implementation                  | 86 |

| 6.9 Self-biased Gm Boosted Differential Colpitts VCO      | 88 |

| 6.10 Buffer Design                                        | 89 |

| 6.11 Layout    | 90  |

|----------------|-----|

| 7. CONCLUSIONS | 93  |

| REFERENCES     | 95  |

| APPENDIXES     | 98  |

| RESUME         | 102 |

|                |     |

# **ABBREVIATIONS**

| RF     | : Radio Frequency                                   |

|--------|-----------------------------------------------------|

| IC     | : Integrated Circuit                                |

| LO     | : Local Oscillator                                  |

| VCO    | : Voltage Controlled Oscillator                     |

| MOS    | : Metal Oxide Semiconductor                         |

| NMOS   | : N- Type Metal Oxide Semiconductor                 |

| CMOS   | : Complementary Metal Oxide Semiconductor           |

| PMOS   | : P-Type Metal Oxide Semiconductor                  |

| MOSFET | : Metal Oxide Semiconductor Field Effect Transistor |

| AM     | : Amplitude Modulation                              |

| PM     | : Phase Modulation                                  |

| FM     | : Frequency Modulation                              |

| AC     | : Alternative Current                               |

| DC     | : Direct Current                                    |

| IMOS   | : Inversion Mode Metal Oxide Semiconductor          |

| AMOS   | : Accumulation Mode Metal Oxide Semiconductor       |

| PVT    | : Process Voltage Temperature                       |

| LTV    | : Linear Time Variant                               |

| LTI    | : Linear Time Invariant                             |

| PA     | : Power Amplifier                                   |

| PLL    | : Phase Locked Loop                                 |

| Q      | : Quality Factor                                    |

| ISF    | : Impulse Sensitivity Function                      |

| CAD    | : Computer Aided Design                             |

| PSS    | : Periodic Steady State                             |

| SCA    | : Switched Capacitor Array                          |

|        |                                                     |

# LIST OF TABLES

### Page No

| Table 1.1.         | Phase noise specification values for Bluetooth4                      | ł  |

|--------------------|----------------------------------------------------------------------|----|

| Table 6.1.         | CMOS cross-coupled LC Oscillator device dimensions                   | 50 |

| Table 6.2.         | NMOS cross-coupled LC Oscillator device dimensions                   | 53 |

| Table 6.3.         | PMOS cross-coupled LC Oscillator device dimensions                   | 54 |

| Table 6.4.         | Performance comparison of all designed circuits in this section6     | 54 |

| Table 6.5.         | Inductor parameter comparison                                        | 56 |

| Table 6.6.         | Guaranteed operating points of several MOSCAPs for a 0.5V swing.     | 59 |

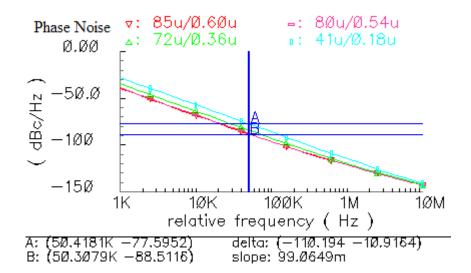

| Table 6.7.         | Phase noise performances vs. bias current                            | 12 |

| Table 6.8.         | Phase noise degradation for the worst case                           | 13 |

| Table 6.9.         | Comparison of top current source biased and resistor biased NMOS     |    |

|                    | LC VCO                                                               | 15 |

| <b>Table 6.10.</b> | Specifications of NMOS LC VCO with res. and ind. tail biasing 7      | 78 |

| <b>Table 6.11.</b> | Phase noise degradation with respect to several control voltages for |    |

|                    | the worst case                                                       | 30 |

| Table 6.12.        | Specifications of self-biased NMOS LC VCO                            | 31 |

| <b>Table 6.13.</b> | Specifications of self-biased NMOS LC VCO with noise optimized       |    |

|                    | Ŵ/L                                                                  | 33 |

| <b>Table 6.14.</b> | Specifications of NMOS LC VCO with bias level shifting               | 35 |

| Table 6.15.        | Specifications of NMOS LC VCO with bias level shifting after         |    |

|                    | noise optimized W/L                                                  | 36 |

| <b>Table 6.16.</b> | Specifications of Gm boosted Colpitts VCO for several capacitive     |    |

|                    | divider ratio values                                                 | 38 |

| Table 6.17.        | Specifications of self-biased Gm boosted Colpitts VCO for N=1/5 8    | 39 |

# LIST OF FIGURES

### Page No

| Figure 1.1     | : A phase locked loop with a voltage controlled oscillator (VCO),    |     |

|----------------|----------------------------------------------------------------------|-----|

|                | frequency divider, phase detector (PD), charge pump (CP) and         |     |

|                | lead-lag loop filter                                                 | 2   |

| Figure 1.2     | : Trade-off between crucial VCO specifications                       | 4   |

| Figure 2.1     | : Feedback model of an oscillator                                    |     |

| Figure 2.2     | : Ring oscillator implementation; (a) differential topology, (b)     |     |

| -              | single-ended topology                                                | 6   |

| Figure 2.3     | : Current starved inverter                                           | 7   |

| Figure 2.4     | : Differential cell with symmetric load                              | 7   |

| Figure 2.5     | : Conversion of the series resistances of an LC tank into a parallel |     |

| -              | resistance                                                           | 8   |

| Figure 2.6     | : Magnitude and phase spectrum of an LC tank                         | 9   |

| Figure 2.7     | : One-port view of an LC oscillator                                  | 10  |

| Figure 2.8     | : Bottom biased NMOS cross-coupled LC oscillator with series         |     |

|                | losses and parallel losses                                           |     |

| Figure 2.9     | : Analysis of an NMOS cross-coupled LC oscillator                    | 11  |

| Figure 2.10    | : Output voltage saturation                                          | 12  |

| Figure 2.11    | : Current waveform of a switching transistor in NMOS cross-          |     |

|                | coupled LC oscillator in time and frequency domain                   | 13  |

| Figure 2.12    | : Top biased CMOS cross-coupled LC oscillator                        | 14  |

| Figure 2.13    | : Single ended Colpitts Oscillator                                   |     |

| Figure 2.14    | : Negative Gm Analysis of Colpitts oscillator                        | 16  |

| Figure 2.15    | : Differential Colpitts oscillator                                   |     |

| Figure 2.16    | : Current shifting differential Colpitts Oscillator [6]              |     |

| Figure 2.17    | : Gm Boosted differential Colpitts oscillator [7]                    |     |

| Figure 3.1     | : Phase noise in time and frequency domain                           |     |

| Figure 3.2     | : Spectrums of output waveforms of an ideal and a real oscillator .  |     |

| Figure 3.3     | : Effect of phase noise in receivers                                 |     |

| Figure 3.4     | : Effect of phase noise in transmitters                              |     |

| Figure 3.5     | : One-port view of LC oscillator with noise sources                  |     |

| Figure 3.6     | : Phase noise spectrum of an actual oscillator                       |     |

| Figure 3.7     | : Ideal LC oscillator stimulated by a current pulse                  |     |

| Figure 3.8     | : Impulse effects on a sinusoidal output waveform                    |     |

| Figure 3.9     | : Damping of amplitude variation in one oscillation cycle            |     |

| Figure 3.10    |                                                                      |     |

| Figure 3.11    |                                                                      | 29  |

| Figure 3.12    | : Block diagram describing the response of a current impulse on      | • • |

| <b>TI C</b> 15 | output wave                                                          |     |

|                | : Block diagram of ISF decomposition                                 |     |

| 0              | : Evolution of current noise into phase noise                        |     |

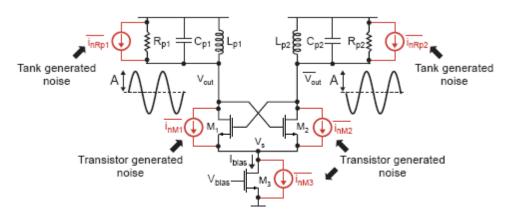

| Figure 3.15    | : Noise generators in a cross-coupled LC VCO                         | 32  |

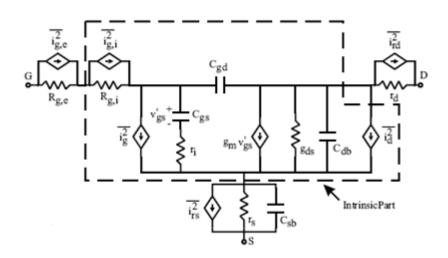

| Figure 3.16 | : Lumped noise model of a MOSFET                                    | 33   |

|-------------|---------------------------------------------------------------------|------|

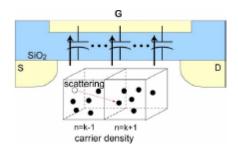

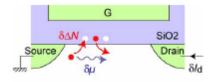

| Figure 3.17 | : Illustration of channel drain noise and induced gate noise        |      |

| Figure 3.18 |                                                                     |      |

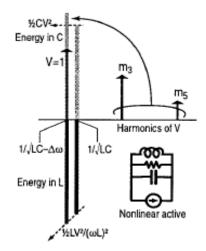

| Figure 3.19 | : Impact of output harmonics on reactive power of an LC tank        | . 36 |

| Figure 3.20 | : Different control voltages applied to IMOS varactor with AC       |      |

| -           | component                                                           | . 38 |

| Figure 3.21 | : Upconversion of flicker noise in switching pair                   | 40   |

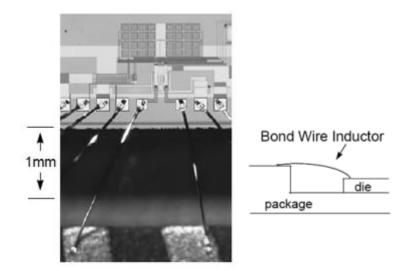

| Figure 4.1  | : Die photo and cross-sectional view of a bond wire inductor        |      |

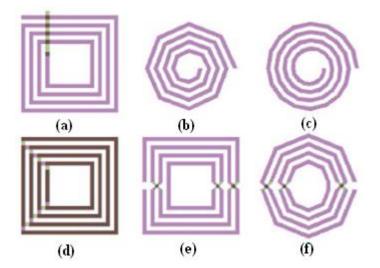

| Figure 4.2  | : Different types of inductors (a) square spiral with cross-under,  |      |

| _           | (b) octagonal spiral, (c) circular spiral, (d) multi-layer series-  |      |

|             | joined square spiral, (e) symmetric center-tapped square spiral,    |      |

|             | (f) symmetric center-tapped octagonal spiral                        | 43   |

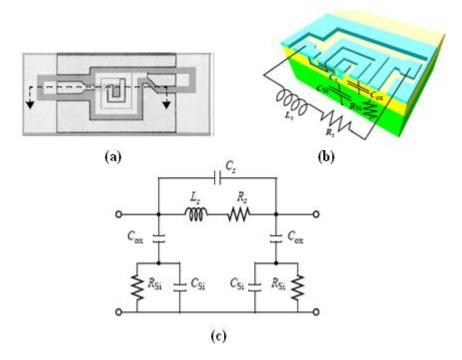

| Figure 4.3  | : (a) Top view, (b) cut-away view, and (c) the physical model of    |      |

| -           | an on-chip spiral inductor                                          | 44   |

| Figure 4.4  | : Physical model of an on-chip spiral inductor and its parallel     |      |

| C           | equivalent network                                                  | . 45 |

| Figure 4.5  | : Layout of inductor in UMC 0.18u design kit                        | 46   |

| Figure 5.1  | : Cross-sectional area of a diode varactor                          | 47   |

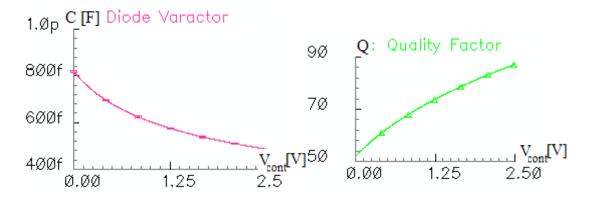

| Figure 5.2  | : Voltage-capacitance characteristics and quality factor of RF      |      |

| -           | diode varactor in UMC 0.18u design library                          | 48   |

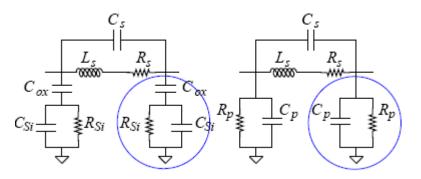

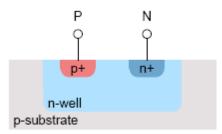

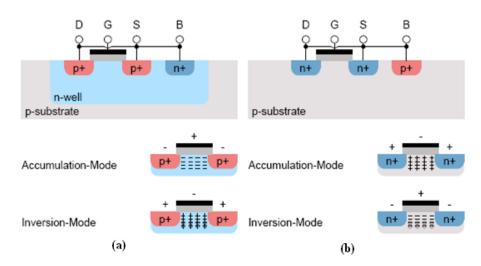

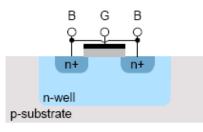

| Figure 5.3  | : Cross-sections and definitions of accumulation and inversion      |      |

| -           | mode of (a) PMOS and (b) NMOS varactor                              | . 48 |

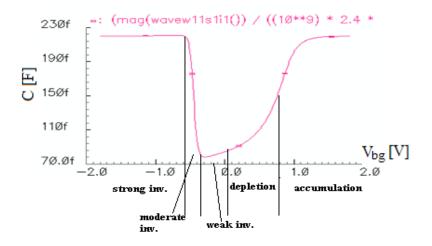

| Figure 5.4  | : Operating modes of PMOS varactor in UMC 0.18u design              |      |

| -           | library                                                             | . 49 |

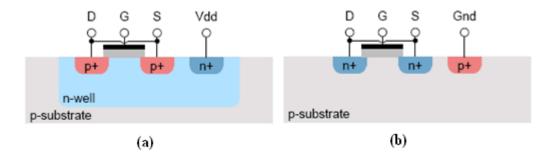

| Figure 5.5  | : Cross-sections of an inversion mode (a) PMOS and (b) NMOS         |      |

|             | varactor                                                            | 50   |

| Figure 5.6  | : Variation of Cvmax/Cvmin with respect to channel length in        |      |

|             | IMOS varactors                                                      | 51   |

| Figure 5.7  | : Cross-section of an accumulation mode PMOS varactor               | 51   |

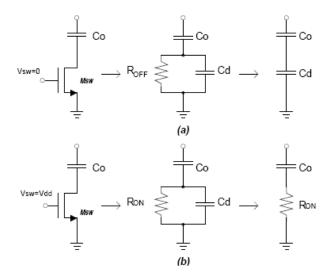

| Figure 5.8  | : NMOS as a RF switch                                               | 52   |

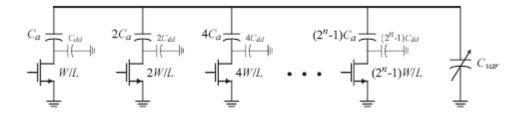

| Figure 5.9  | : Varactor implementation of switched capacitor array               |      |

| Figure 5.10 | : Differential Switch                                               |      |

| Figure 5.11 | : Circuit schematic of the differential SCA [26]                    |      |

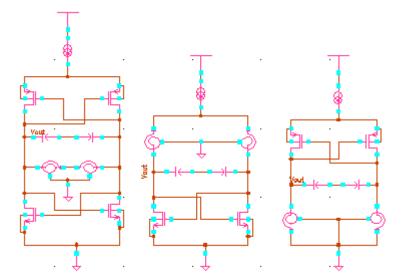

| Figure 6.1  | : Schematics of three cross-coupled topologies                      |      |

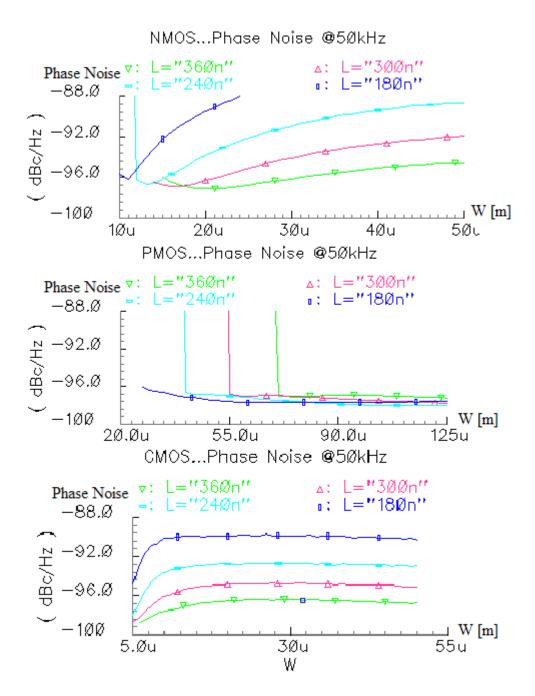

| Figure 6.2  | : Phase Noises of three topologies at 50kHz offset                  |      |

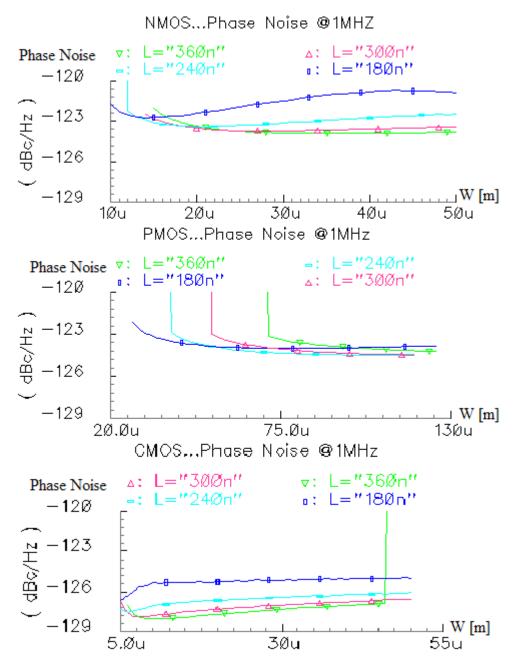

| Figure 6.3  | : Phase Noises of three topologies at 1 MHz offset                  |      |

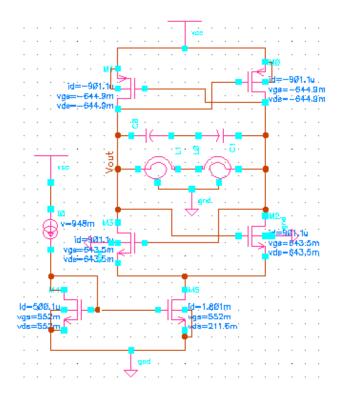

| Figure 6.4  | : CMOS cross-coupled LC oscillator with NMOS bias circuitry         | . 59 |

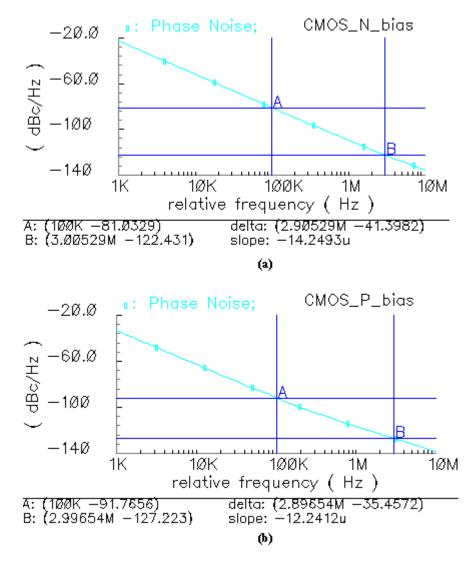

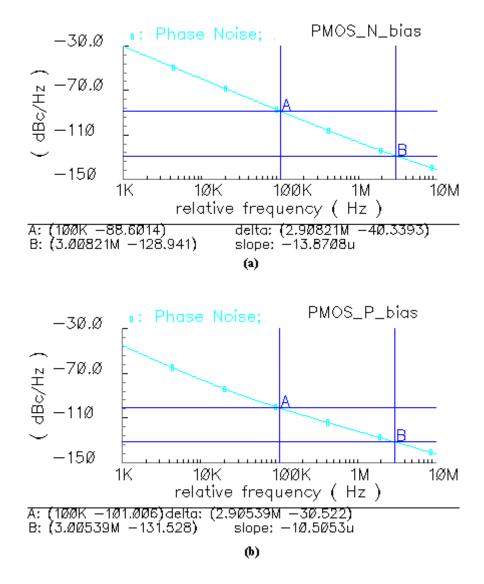

| Figure 6.5  | : Phase noise spectrum of CMOS topology with (a) NMOS and           |      |

|             | (b) PMOS bias circuitry                                             |      |

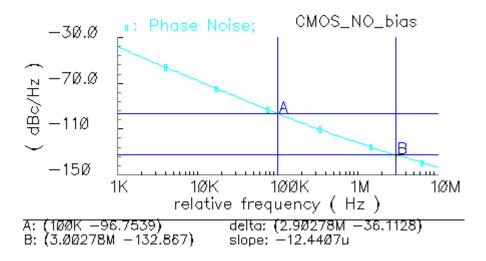

| Figure 6.6  | : Phase noise spectrum of self biased CMOS topology                 | 61   |

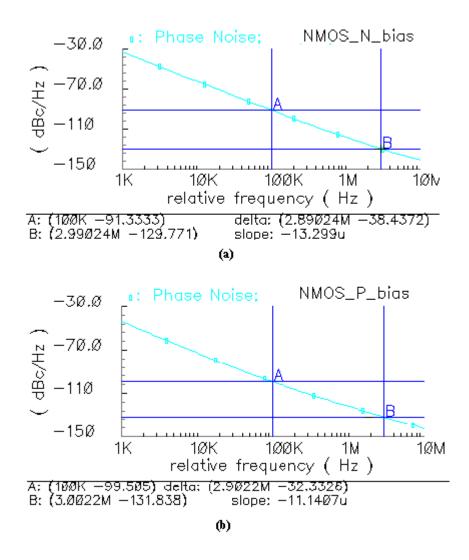

| Figure 6.7  | : Phase noise spectrum of NMOS topology with (a) NMOS and           |      |

|             | (b) PMOS bias circuitry                                             | 62   |

| Figure 6.8  | : Phase noise spectrum of PMOS topology with (a) NMOS and           |      |

|             | (b) PMOS bias circuitry                                             |      |

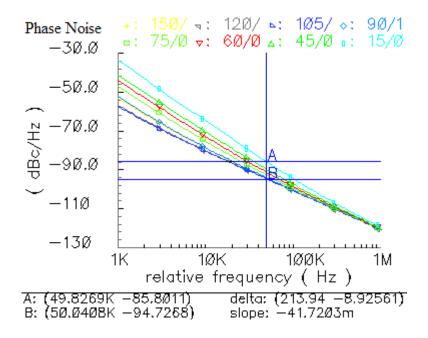

| Figure 6.9  | : Effect of bias transistor dimension on phase noise performance .  | 67   |

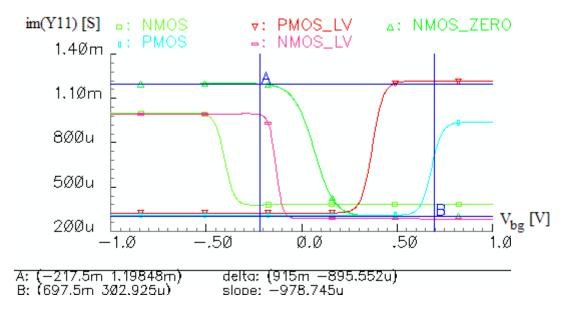

| Figure 6.10 | : Y11 imS: Cmax/Cmin ratio of several IMOS varactors in UMC         |      |

|             | 0.18u library                                                       |      |

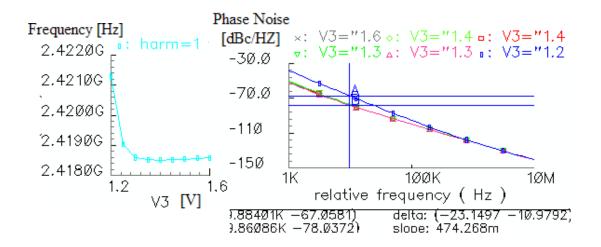

|             | : Effect of digital control voltage on phase noise performance      |      |

|             | : Fine and course tuning varactor schematics                        |      |

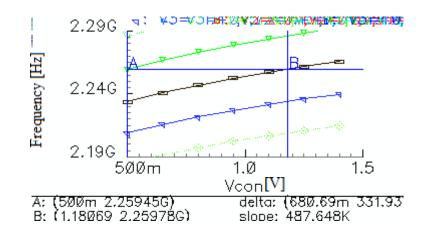

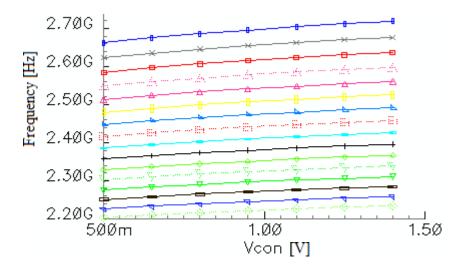

| Figure 6.13 | : Fine tuning: frequency variation with respect to control voltage. | 71   |

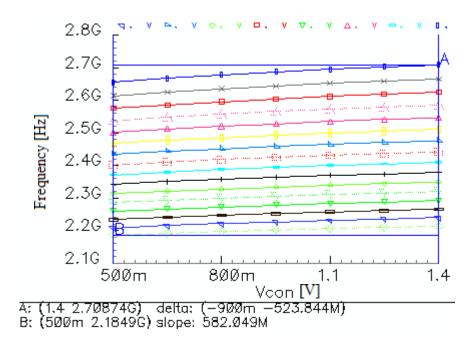

| Figure 6.14  | : Coarse tuning: frequency variation with respect to digital control bits | 72 |

|--------------|---------------------------------------------------------------------------|----|

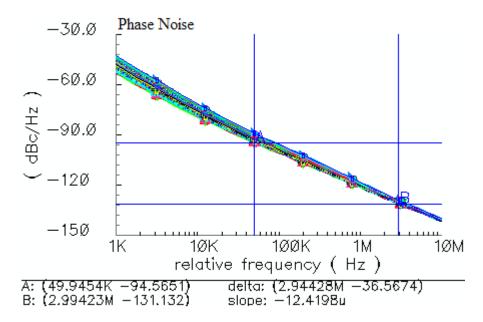

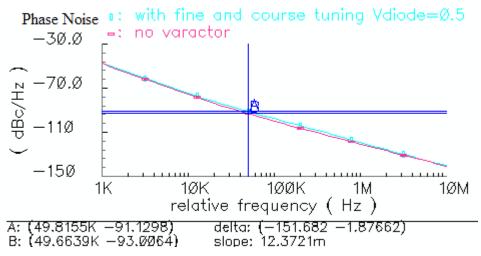

| Figuro 6 15  | : Phase noise spectrum of overall frequency tuning range                  |    |

|              |                                                                           | 15 |

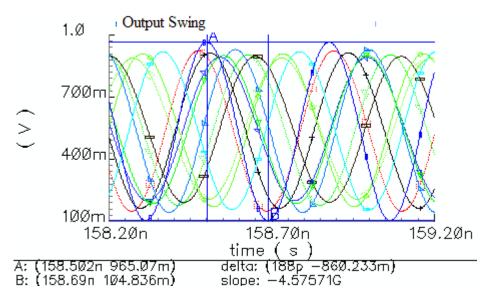

| rigure 0.10  | : Output waveforms from "0000" to "1111" at 0.5V fine tuning              | 70 |

|              | 0                                                                         | 73 |

| Figure 6.17  | : Phase noise degradation after the addition of 4bit IPMOS array          |    |

|              | and diode varactor at 2.45Ghz                                             |    |

| Figure 6.18  | : Implementation of filtering technique                                   | 76 |

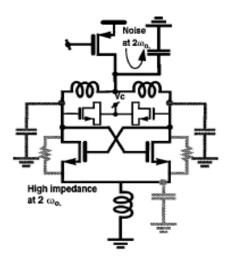

|              | : Suppression of second harmonic via noise filter                         |    |

| 0            | : Schematics of an NMOS cross-coupled LC VCO with Resistive               |    |

| 8            | and Inductive Tail Biasing                                                | 78 |

| Figure 6.21  | : 4-bits differential SCA varactor with capacitive coupling diode         |    |

| 8            | varactor                                                                  | 79 |

| Figure 6.22  | : Phase noise spectrum for several transistor dimensions                  |    |

| 0            | providing equal bias current at a fixed f <sub>0</sub>                    | 81 |

| Figure 6.23  | : Effect of noise filter and 4 bits SCA varactor on phase noise at        |    |

| ingui e oize | 2.4GHz                                                                    | 82 |

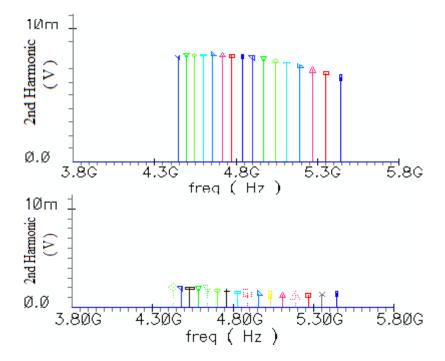

| Figuro 6 24  | : Frequency spectrum after the addition of 4 bits SCA varactor            | 02 |

| Figure 0.24  | structure                                                                 | on |

| <b>D</b> '   |                                                                           | 02 |

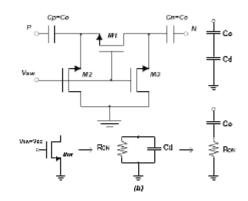

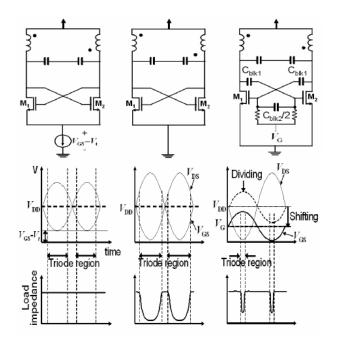

| Figure 6.25  | : Waveforms and load impedances ( <i>Rload</i> ) of LC VCO (a) with       |    |

|              | current source, (b) without current source, and (c) using gate            |    |

|              | voltage dividing and bias level shifting techniques                       |    |

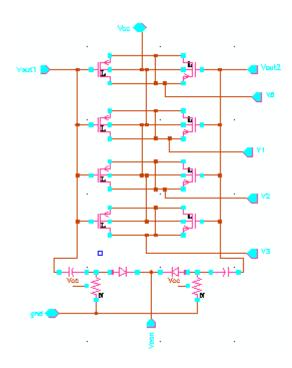

| Figure 6.26  | : Circuit schematics of Gm boosted differential Colpitts VCO              | 87 |

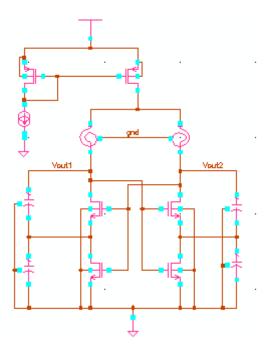

| Figure 6.27  | : Schematic of buffer                                                     | 90 |

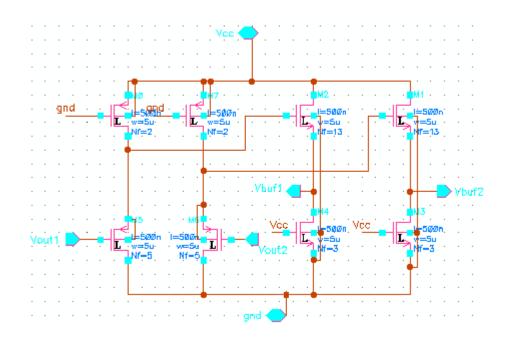

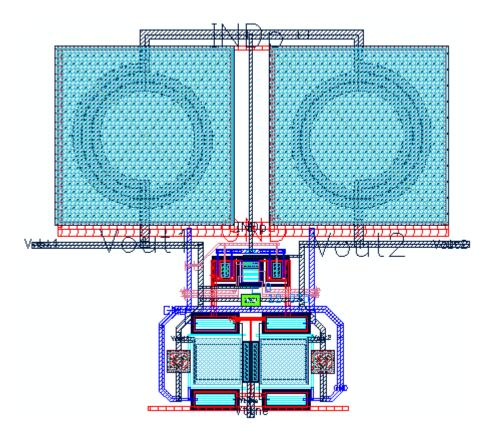

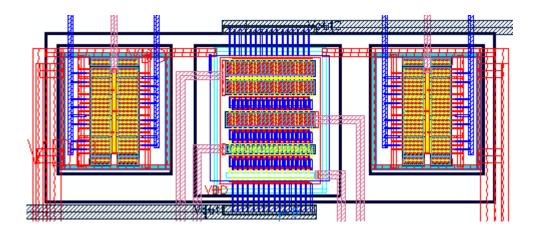

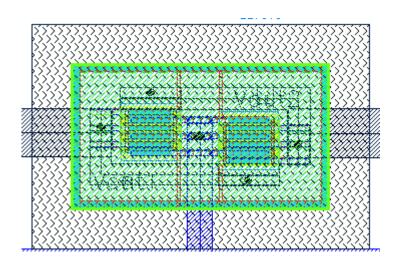

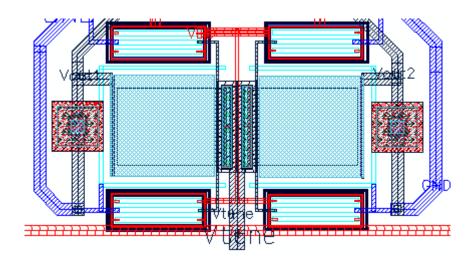

| Figure 6.28  | : Layout of VCO                                                           | 91 |

| 0            | 5                                                                         |    |

### LIST OF SYMBOLS

- : Time t

- : Frequency f

- π : Pi constant

- ${\it \Omega}$ : Ohm

- : Thermal Noise Coefficient γ

- F : Phase Noise Fitting Parameter

- : Large Signal Transistor Transconductance  $G_m$

- : Small Signal Transistor Transconductance  $g_m$

- : Width W

- : Length L

- : Supply Voltage : Quality Factor  $V_{dd}$

- Q

- : Conductance Loss  $g_l$

# 2.4 GHz DÜŞÜK GÜÇLÜ LC VCO TASARIMI

# ÖZET

Bu tez çalışmasında, Bluetooth standardında çalışabilen çeşitli gerilim kontrollü LC osilatör devreleri UMC 0.18u prosesinde tasarlanmıştır. Bluetooth uygulamalarının düşük güç gereksinimi göze alınarak çalışmanın ikinci hedefi düşük güçlü devre çözümleri olarak belirlenmiştir. İlaveten, PLL'e tam uygunluk sağlanması amacıyla dışarıdan devreye bağlanacak olan gerilim değerlerinin toprakta ya da besleme gerilimine eşit olması sağlanmıştır.

Çalışmada ilk olarak temel osilasyon teorisi anlatılmıştır. Sağlanan bu altyapının üzerine entegre osilatörler anlatılmış, özellikle RF entegre osilatörleri olarak sıkça kullanılan negatif Gm ve Colpitts osilatör yapılarının detaylı analizleri yapılmıştır. Bunun yanı sıra birbirlerine olan üstünlükleri ve eksiklikleri de belirtilmiştir.

İkinci olarak, GKO faz gürültüsü ele alınmıştır. Faz gürültüsü ve alıcı-vericiler üzerindeki etkileri üzerinde kısaca durulmuş ve bundan sonra iki faz gürültüsü modelinin çıkarımı, altında yatan temel prensiplerle birlikte adım adım anlatılmıştır. Bu faz gürültüsü ifadeleri üzerine yorumlar yapılarak tasarım kısmında gürültünün kaynakları hakkında temel bir bakış açısı edinilmesi amaçlanmıştır. Bölümün son kısmında çapraz bağlı bir LC GKO devresindeki her elemanın sebep olduğu faz gürültüsü analiz edilmiştir. 'Pasif ya da aktif elemanların gürültüleri nasıl faz gürültüsüne dönüşür?' ya da 'Hangi mekanizmalar faz gürültüsüne sebep olur?' gibi soruların cevapları her faktörün sebep olduğu faz gürültüsünün nasıl düşürülebileceği anlatılarak verilmiştir.

Üçüncü olarak, entegre devrelerde kullanılan varaktör ve endüktans çeşitleri anlatılmıştır. Endüktansın fiziksel modelinde bulunan elemanlar kısaca açıklanmış ve darbant modelinin dönüşüm ifadeleri verilmiştir. Bu eşitlikler sayesinde endüktansın kalite faktörü veya iletkenlik kaybı gibi önemli parametrelerinin yazılan Matlab koduyla elde edilmesi sağlanmıştır.

Tasarım kısmında başlangıç noktası olarak 3 temel çapraz bağlı osilatör yapısının faz gürültüsü performansları düşük güç tüketimi göz önüne alınarak karşılaştırılmıştır. Bundan sonra en uygun osilatör seçilmiş ve yüksek *figure of merit* sağlaması amacıyla optimize edilmiştir. Optimizasyonda amaç faz gürültüsü mekanizmalarının etkisini azaltmaktır. Bu sebeple, varaktör yapısı üzerindeki AM-PM dönüşümünün en aza indirilmesi amacıyla frekans ayarlamasının kaba ve ince ayar olmak üzere ikili olması kararlaştırılmıştır. Kaba ayar devresi 4 bitlik sayısal kontrollü varaktör yapısı olarak tasarlanmıştır. Devrenin fizibilitesini göz önünde bulundurarak kontrol bitlerine uygulanacak gerilim değerlerinin toprakta olması ya da beslemeye bağlanması farz edilmiştir. Bunu sağlamak amacıyla çeşitli tranzistörler denenmiş ve sadece düşük eşik gerilimli PMOS tranzistörün uygulanabileceği görülmüştür. İnce ayar devresi olarak kapasite bağlı diyot varaktör devresi seçilmiş ve rezonatörü yüklemeyecek şekilde tasarlanmıştır. Aynı şekilde diyotun maksimum kontrol gerilimi de besleme gerilimine eşit tutulmuştur. Sonuç olarak verilen faz gürültüsü sınır değerlerinin en kötü durumda bile 5dBc/Hz aşağısında değerler elde edilmiştir. Bu devreye ilaveten daha düşük gerilimlerde çalışabilen yine çapraz bağlı topolojisine dayanan çeşitli GKO'ların tasarımı yapılmıştır. Çok düşük gerilim değerlerinde IMOS varaktörün sayısal kontrolu imkansız olduğundan 4 bitlik farksal anahtarlamalı kapasite dizisi tasarlanmıştır. Simulasyonlar neticesinde birçok devrenin Bluetooth standardını filtre görevi üstlenen bir endüktans ile sağladığı görülmüştür. Sonuç olarak düşük gerilimli çözümler istenilen faz gürültüsü değerlerini geniş bir alan kaybıyla ödeyerek kazanmıştır. Tasarım bölümünün son kısmında üç değişik farksal Colpitts devrelerinin akım değerleri diğerler devrelerle aynı tutularak tasarlanmasına çalışılmıştır fakat sadece Gm yükseltilmiş Colpitts devresinin salınıma başlatılabildiği gözlemlenmiştir. Bu devrenim faz gürültüsü performansının tasarlanan ilk çapraz bağlı devreden daha düşük olduğu görülmüştür.

### DESIGN OF A 2.4 GHZ LOW POWER LC VCO IN UMC 0.18u TECHNOLOGY

### SUMMARY

In this work, several LC oscillators were designed to meet the specifications of Bluetooth standard in UMC 0.18u technology. Taking into account that low power consumption is demanded for Bluetooth applications, another target of the work was decided to focus on low power circuit implementations. Also, to provide a full integration to a PLL, the external voltages applied to the oscillator were kept below or equal to supply voltage as much as possible.

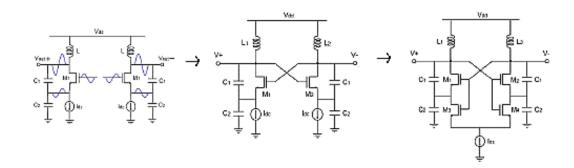

Firstly, basic oscillation theory including the feedback system approach and two single-port view was explained. After attaining fundamental knowledge on oscillators, three IC oscillator types; the ring, the negative Gm and the Colpitts oscillator were described. Since mostly preferred RF IC VCOs are the cross-coupled and the Colpitts oscillators, they were analyzed in details and their superiorities and drawbacks were given.

Secondly, the specification that makes the oscillator design crucial, the oscillator phase noise, was focused on. After a brief definition of the phase noise and its effect on RF transceivers, the expressions of two phase noise models were obtained via a step by step transformation methodology, also, by explaining the underlying approaches; LTV and LTI. The phase noise expressions were commented to provide practical conclusions so that the phase noise sources in the designed oscillators could be understood. This topic ended with a very detailed and useful analysis of the phase noise sources in a cross-coupled LC VCO. The questions such as "how the noise of the active and passive devices is translated to phase noise?" and "which mechanisms cause the phase noise?" were answered through giving the techniques to reduce the phase noise produced by each factor.

Thirdly, the varactor and the inductor types employed in IC process were discussed. The elements in the physical model of the inductor were described briefly and its narrowband model conversion equations were expressed. With the aid of these equations, the physical model of the inductor in UMC 0.18um design kit was converted via a Matlab code in order to obtain the important parameters such as the conductance loss and the quality factor.

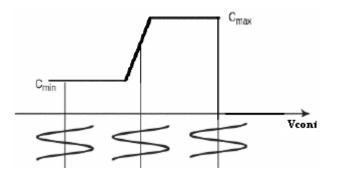

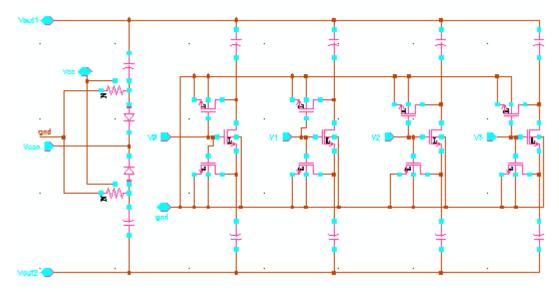

As a starting point to the design section, three basic cross-coupled LC oscillators were compared due to low power consumption. After choosing the most suitable topology, the oscillator was optimized by minimizing the effect of the phase noise generating mechanisms to achieve a high figure of merit circuit. For this reason, the AM-PM conversion, which degrades the phase noise at least 10dBc/Hz when only an IMOS varactor is employed, was reduced by recognizing the frequency tuning in two ways; the fine and the coarse tuning. In the coarse tuning circuitry, a 4 bits digitally controlled varactor structure was designed. Considering the feasibility of the circuit, the voltage values applied to control bits were assumed to be ground and supply

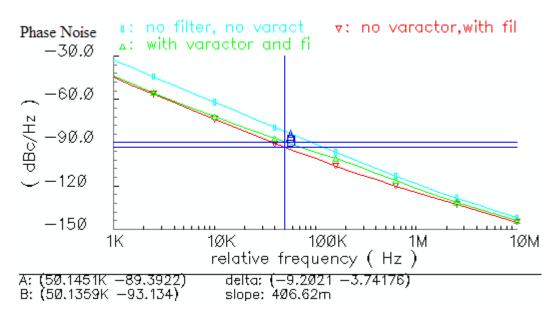

voltage for on or off state of varactors. To accomplish that, low-V<sub>th</sub> PMOS transistor was selected after examining the possibility of several MOS transistors. In fine tuning circuitry, a capacitor coupled diode varactor topology was properly implemented without degrading the quality factor of the tank and again the maximum value was kept equal to supply voltage for high integration. As a result, the phase noise requirement was attained with a 5dBc/Hz phase noise margin for the worst case. In addition to the oscillator described above, several LC voltage controlled oscillators based on cross-coupled topology were designed in order to lower the power consumption as well as to satisfy the phase noise specification. To make a fair comparison, in most cases, their bias current was kept the same. It was not possible to digitally control an IMOS varactor in an ultra low voltage range (from ground to <1V), therefore the digital control topology was replaced with a 4 bits binary weighted differential SCA array to be able to apply the supply voltage as the digital control voltage. After the phase noise simulations, most of the circuits met the phase noise requirement of the Bluetooth standard with the use of a filtering inductor. In the last part of the design section, three differential Colpitts structure were targeted to design with respect to the same current, but only Gm boosted Colpitts topology achieved to start-up the oscillation. However, this topology had a worse phase noise performance compared to the first oscillator design.

#### **1. INTRODUCTION**

#### **1.1 Motivation behind the Work**

As the time passes, people are taking a closer interest on the technological developments in communication systems. They demand more and different features at a reasonable cost. For instance, while purchasing a cell phone, they seek for not only a good camera resolution, high purity mp3 sound and a variety of menu options, but also a stylish design -mostly slim and compact design- and a long lasting battery. This increasing pressure for lower power, higher integration and lower cost in the mobile communication market drives the industry to on-chip solutions and CMOS technology. Among different fabrication technologies such as GaAs and SiGe, CMOS provides high integration levels, mixed analog/digital compatibility, capability for low voltage operation, mature fabrication technology, successful scaling characteristics, and the combination of complementary MOSFETs yielding low power CMOS circuits. For these reasons, in a transceiver the baseband blocks such as high speed ADC/DAC, DSPs and memories are mostly manufactured in CMOS technology and this constrains RF blocks to be also implemented in the same technology. However, the integration between them is an important issue because RF blocks generally need external passive components such as front-end SAW filters to accomplish their mission which is to carry the desired signal from the antenna to the baseband blocks with a minimum loss in the receiver path and to generate high purity signals with high efficiency in the transmitting path. Bringing the signal off-chip and then on-chip again complicates the transceiver design because proper matching at the output and input terminals is required. This also increases the power consumption of the transceiver because it takes more power to drive an off-chip load than to keep the signal completely on the same integrated circuit. Generally, taking the signal off and then on-chip results in signal power loss accompanied by an undesirable increase in noise figure. Taking these drawbacks into account, a fully integrated RF front-end and surely an RF transceiver is desirable despite the fact that passive IC devices have poorer quality factor than their discrete counterparts.

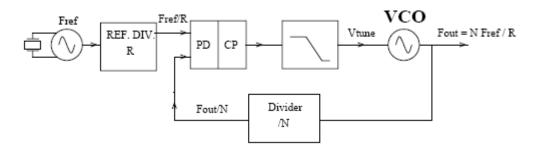

Indirect frequency synthesis techniques based on a phase-locked-loop (PLL) are preferred to generate programmable carriers and RF frequencies that many communications applications require. In a PLL structure as depicted in Fig. 1.1, a less accurate RF oscillator whose frequency can be controlled with a control signal is embedded in a feedback loop and its output frequency is locked to an accurate low frequency reference. In general, this control signal is a DC voltage and so the RF oscillator is called a voltage controlled oscillator (VCO). Hence, a VCO generates the local oscillator (LO) signal to upconvert the input baseband signal and to downconvert the RF signal. In addition to the frequency translation duty, they are also used in clock recovery circuits. Despite being researched continually, it is still a bottleneck and one of the most critical and challenging parts of a transceiver due to some severe parameters that will be explained below.

**Figure 1.1:** A phase locked loop with a voltage controlled oscillator (VCO), frequency divider, phase detector (PD), charge pump (CP) and lead-lag loop filter; the VCO's output frequency Fout is set to a multiple of the reference oscillators frequency Fref depending on the divider ratios (N & R).

### 1.2 VCO Spec-sheet

In each VCO design, several requirements must be fulfilled regarding the application of interest such as GSM, ZigBee or other communication protocols. These specifications are composed of the following entries:

**Center Frequency:** is the oscillation frequency of the VCO where the control voltage takes its center value. It is denoted in [Hz] and its angular frequency equivalent is in [rad/s]. The application determines its value.

**Tuning Range:** is the interval of output frequencies where the VCO operates over the whole range of the control voltage. Due to process variations, the tuning range provided by the application is generally increased by %20.

**Tuning Sensitivity:** is the variation in output frequency per unit change in the control voltage, typically expressed in [Hz/V]. VCOs usually have a nonlinear relationship between the control voltage and the oscillation frequency so that several values are quoted or min/max boundaries are given.

**Power Consumption:** specifies the DC power used up by the oscillator. In some applications, power dissipation has a vital importance among all specifications.

**Spectral Purity:** can be specified depending on the application, in the time domain in terms of jitter or in the frequency domain in terms of phase noise or carrier/noise ratio. The factors affecting the purity of the LO output waveforms will be discussed in chapter 3.

**Load Pulling:** quantifies the sensitivity of the output frequency to changes in its output load. In some applications the output load of the VCO is switched while the VCO must remain at the same frequency to avoid frequency errors.

**Supply Pulling:** defines the sensitivity of the output frequency to changes in the power supply voltage and is expressed in [Hz/V]. The power up or down of other circuits in a transceiver can generate abrupt changes in the power supply voltage so the VCO frequency can shift up or down.

**Output Power:** is the power delivered to a specified load by the VCO. A low change in output power with respect to different control voltage values is desirable.

**Harmonic suppression:** specifies the ratio of the harmonics of the output signal to the fundamental wave voltage in [dBc].

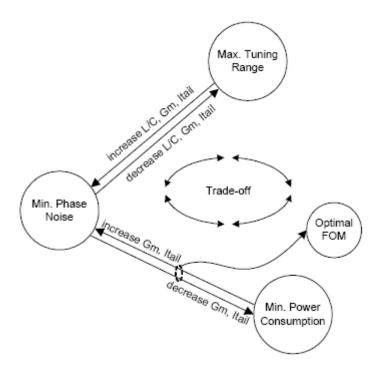

Among these specifications, low phase noise, low power dissipation and large tuning requirements are usually the dominant terms and the trade-off between them makes the VCO design challenging.

Figure 1.2: Trade-off between crucial VCO specifications [1]

#### 1.3 The Design Specifications of the Proposed VCO

In this project, a VCO is intended for Bluetooth application. Bluetooth is a wireless communication technology using short-range radio links to connect portable and/or fixed electronic devices. Its key features are robustness, low complexity, low power and low cost. Designed to operate in noisy frequency environments, the Bluetooth radio uses a fast acknowledgement and frequency hopping scheme to make the link robust. Bluetooth radio modules operate in the unlicensed industrial, scientific and medical (ISM) band at 2.4GHz to 2.485GHz and the signal hops among 79 frequencies at 1MHz intervals to a new frequency after transmitting or receiving a packet. The ISM band is available and unlicensed in most countries.

**Table 1.1:** Phase noise specification values for Bluetooth

| Offset                    | 50kHz | 3MHz | Noise floor |

|---------------------------|-------|------|-------------|

| Max. phase noise [dBc/Hz] | -84   | -123 | -145        |

The phase noise specification is provided by Nokia as depicted in Table 1.1. Since it is not stringent, the VCO is proposed to consume as low power as possible. Taking process variations into account, the targeted frequency range is between 2.2GHz and 2.7GHz with a center frequency of 2.45GHz.

### 2. OSCILLATOR BASICS

In this chapter, basic oscillation theory including the feedback system approach and two single-port view is explained. Three IC oscillator types; the ring, the negative Gm and the Colpitts oscillator are described. Since mostly preferred RF IC VCOs are the cross-coupled and the Colpitts oscillators, they are analyzed in details and their superiorities and drawbacks are given.

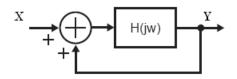

#### 2.1 Oscillator as a Feedback System

An oscillator can be modeled as a feedback circuit. The overall transfer function of the feedback network depicted in Fig. 2.1 is expressed as

$$G(jw) = \frac{Y(jw)}{H(jw)} = \frac{H(jw)}{1 - H(jw)}$$

(2.1)

At a frequency of  $\omega_0$ , if H(j $\omega_0$ )=1 where the closed loop gain goes to infinity, the system causes its own noise to grow and generates a periodic signal. The oscillation reaches its steady state when H(j $\omega_0$ ) is purely imaginary [2]. In practice, the small-signal loop gain must have a value of at least two to guarantee the oscillation start up because this value is reduced and equals to one as the amplitude increases due to the nonlinearity of the active device. Therefore, two conditions must be met for steady oscillations at  $\omega_0$ :

$$|H(j\omega_o) = 1| \tag{2.2a}$$

$$arg(H(j\omega_o)) = 0^{\circ} \tag{2.2b}$$

The latter expression can be modified to a value of 180° for a negative feedback system. These expressions are called Barkhausen's criteria. However, for some cases Barkhausen's criteria is necessary but not sufficient. For instance, if the phase shift at dc level is zero, even though the loop gain is enough to start oscillation, the output voltage goes to supply voltage or zero rather than oscillate. A cascade amplifier

which contains two single common-source stage transistors with a feedback from the drain of the second transistor to the gate of the first one is a good example of this case. The output latches because overall phase shift is also 360° at zero frequency.

Figure 2.1: Feedback model of an oscillator

Today, there are many topologies used to realize oscillation feedback systems answering the two conditions mentioned above. In general, ring oscillators and LC oscillators are commonly preferred in RF IC oscillator design.

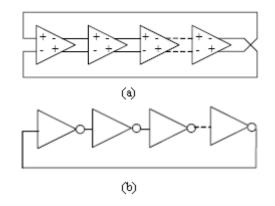

#### 2.2 Ring Oscillators

Ring oscillators comprise N amplifiers with an odd number of inversions connected in a feedback loop. Each amplifier stage acts as an inverter and total delay of each inverter cell determines the large-signal oscillation frequency below:

$$f_o = \frac{1}{2 N t_d} \tag{2.3}$$

The number of stages (N) is mainly chosen due to the power dissipation and the phase-noise performance. There are two main topologies for the ring-oscillator: the differential and the single-ended one (Fig. 2.2).

Figure 2.2: Ring oscillator implementation; (a) differential topology, (b) single-ended topology

In single-ended topology Barkhausen criteria is always fulfilled since the inverter cells have high small-signal gain. The single-ended topology has to be implemented

with an odd number of cells because each delay cell has a large-signal phase shift of 180°. The current is only consumed during transitions of the inverters. This constant current generated by the transistor when "on" charges and discharges the intrinsic capacitances of transistors; therefore, it defines the delay time of each cell, so the higher current leads to a faster transition and higher oscillation frequency. It is possible to control the frequency with voltage sources by adding two transistors as shown in Fig. 2.3. This type of delay cell is called current-starved inverter.

Figure 2.3: Current starved inverter

The differential topology is composed of a load and an NMOS differential pair (Fig 2.4). The delay in the cell is set by the charge in each node and the current through the load. As load devices, resistors can be used for fixed frequency or PMOS transistors can be employed to make the oscillator tunable with external voltages. PMOS load can be implemented as symmetric or cross-coupled.

Figure 2.4: Differential cell with symmetric load

The differential ring oscillator has  $N(1+V_{char}/(R_L*I_{tail}))$  times higher phase-noise level than the single-ended ring oscillator with equal power dissipation, frequency and number of stages [3]. The single-ended topology dissipates less power than the differential topology and therefore has a better phase noise for a given power dissipation since phase noise is inversely proportional to power consumption. In digital circuits differential ring oscillators are often preferred because they have much better common noise rejection of substrate-coupled noise [3]. They also have lower noise injection into other circuits on the same chip [3]. A quadratic signal can only be obtained by using differential topology since even number of cells can be implemented.

Non-use of passive devices in ring oscillators is both advantageous and disadvantageous. The only usage of active devices makes ring oscillator easy to integrate. Furthermore, an inductor occupies a substantial amount of area in an IC oscillator. Its absence will result in less chip area. On the other hand, an inductor with a capacitor forms a band pass filter that causes the phase noise to reduce in an oscillator. As a result, ring oscillators exhibit poor phase noise performance compared to LC oscillators. They are usually used as clock recovery for serial data communications and on chip clock distribution.

### 2.3 LC Oscillators

LC oscillators comprise a resonator tank. There are mainly two LC oscillator type: Negative Gm and Colpitts oscillator. In this section, these two types are analyzed and compared.

### 2.3.1 LC Tank

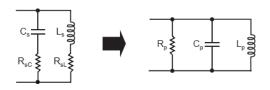

In VCO designs, LC network is widely used because of its filtering capability. The network, also called parallel resonator circuit, is composed of the parallel combination of an inductor and a capacitor. The loss of the network is compensated by an active device. The main contributors of loss in the tank are the series resistances of the passive devices. The parasitic resistances can be converted to their parallel equivalent since RF oscillators operate over a narrow band of frequencies (Fig. 2.5).

Figure 2.5: Conversion of the series resistances of an LC tank into a parallel resistance

Each term in the above figure can be expressed as

$$C_p \approx C_s$$

(2.4)

$$C_p \approx L_s$$

(2.5)

$$R_p = R_{pL} //R_{pC} \approx R_{sC} //Q_{sL}^2 R_{sL} \quad (Q_{sC} \gg 1 \& Q_{sL} \gg 1)$$

(2.6)

where  $Q_L$  and  $Q_C$  are the quality factors of the inductor and the capacitor respectively. The quality factor of the inductor is lower than that of the capacitor even if diode or MOS varactors are used so the dominant term for  $R_p$  is the former part of the Equation 2.6. Also, the filtering capability of the resonator is defined by the quality factor of the inductor. The overall quality factor of the resonator is expressed as below:

$$Q_{tank} = Q_L //Q_C \tag{2.7}$$

However, for some cases, the varactors with very poor quality factor which is close to that of the inductor can be obtained, that causes a drop in the quality factor of the tank.

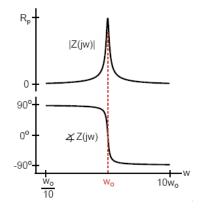

Figure 2.6: Magnitude and phase spectrum of an LC tank

The magnitude and phase characteristics of an LC parallel network are shown above. At resonance the network is purely real, in other words, behaves like a resistor. The resonant frequency is written as  $\omega_o = 1/\sqrt{LC}$ .

### 2.3.2 One-port View of an LC Oscillator

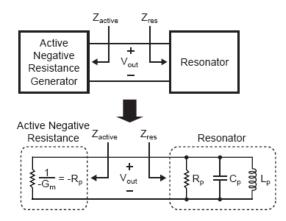

One-port view or sometimes called negative Gm approach handles the oscillator as the connection of two one-port networks (Fig. 2.7). It is especially convenient for intuitive analysis of LC oscillators.

Figure 2.7: One-port view of an LC oscillator

Remembering from Fig. 2.5, the resonator circuit with the series resistive loss of each passive element can be converted to the parallel equivalent for narrow band applications. At each cycle the dissipation of some amount of stored tank's energy in  $R_p$  prevents stable oscillation. However, an active negative resistance generator that is equal to  $-R_p$ , compensates the loss of the tank, therefore, creates a lossless resonator whose parallel resistance is infinite at resonant frequency. In other words, the energy lost in  $R_p$  is regenerated by the active circuit in every cycle. That condition is met with the equation below:

$$\frac{1}{G_m} = R_p \tag{2.7}$$

Here,  $G_m$  is defined as the large signal transconductance of the active device when the oscillator is in steady-state.

#### 2.3.3 Cross-Coupled LC Oscillator

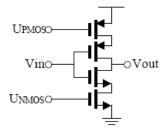

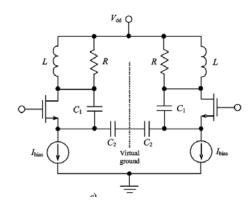

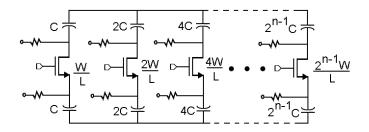

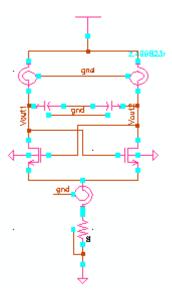

From the point of the negative Gm approach, the loss in the tank must be compensated for steady-state oscillation. In a cross-coupled topology, the transistor pair behaves like an active negative resistance generator. To guarantee oscillation start-up, negative resistance is chosen at least two times more than the parallel loss. Two advantages of this topology are the simple design and the differential implementation. There are three sorts of this topology: NMOS, PMOS and CMOS cross-coupled. Each of these types can be designed with either a current source of top-biased, bottom-biased or self biasing.

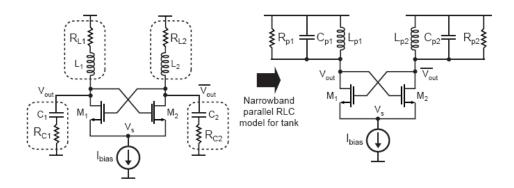

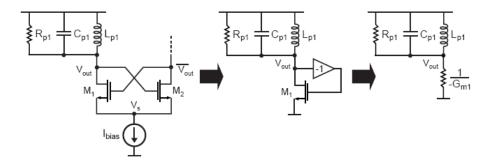

#### 2.3.3.1 NMOS Cross-Coupled LC Oscillator

Fig 2.8 depicts a bottom-biased NMOS cross-coupled LC oscillator including the losses in the tanks. It contains an NMOS differential pair and two equivalent tanks with series and parallel resistive losses, respectively.

Figure 2.8: Bottom biased NMOS cross-coupled LC oscillator with series losses and parallel losses

For the simplicity of the analysis, the circuit is split into two equal parts and it is assumed that the common-mode node is AC grounded so that the source of the transistor  $V_s$  is biased to zero. In reality, this assumption is not definitely valid due to the finite output resistance of the current source. Differential implementation enables two output voltages to have the same output swing with a phase difference of 180° so the gate of the left side transistor can be expressed as  $-V_{out}$ , then the resistance seen from  $V_{out}$  to ground through this transistor is equal to  $V_{out}/I_{d1}=V_{out}/-G_mV_{out}$ , or simply  $-1/G_{m1}$ .

Figure 2.9: Analysis of an NMOS cross-coupled LC oscillator

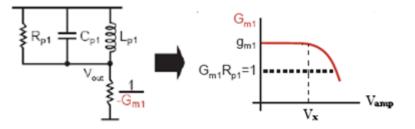

Hence, if two tanks are equal, by merging them one can get the results;  $L_p=2L_{p1}$ ,  $C_p = C_{p1}/2$ ,  $R_p = 2R_{p1}$  and also negative resistances in parallel conclude to  $-2/G_{m1}$ . The equation 2.7 can be rewritten as

$$\frac{1}{G_{m1}} = R_{p1}$$

(2.8)

for an NMOS cross-coupled LC oscillator in steady state. The oscillator must have a greater small-signal loop gain of  $\alpha$  than unity in order to grow its own noise and usually the minimum value of this gain  $\alpha_{min}$  is chosen as at least two. Hence the start-up condition is met if

$$\frac{1}{g_{m1}} \ge \alpha_{min} R_{p1} \tag{2.9}$$

It is interesting to investigate the relationship between the large-signal gain G<sub>m1</sub> and the small-signal gain  $g_{m1}$ . The small-signal gain which is  $\alpha_{min}$  times greater than  $G_{m1}$ leads the circuit's own noise to grow. As the oscillation grows, the small signal gain of the transistor will degrade and stabilize at  $G_{m1}$  due to the nonlinearity of the active device. The nonlinear behavior can be understood by observing the transistor's operation in triode region and in cut-off. While the transistor enters cut-off region, the swing of the positive output wave under bias voltage is clipped. Secondly, the large signal transconductance of an NMOS transistor in linear region is equal to  $\mu_n C_{ox}(W/L)V_{ds}$ , in other words, it is directly proportional to drain voltage. In the NMOS cross-coupled LC oscillator depicted in Fig. 2.9, since the gate and the drain voltages have a phase difference of  $\pi$ , an increment of  $\Delta V$  at  $V_{g1}$  will bring on  $V_{d1}$  or Vg2 to decrease by the same amount as a result of the nature of the differential oscillation. If  $\Delta V$  is high enough, the transistor M<sub>1</sub> to enters into linear region corresponding to Vx in Fig 2.10. At this point  $g_{m1}$  starts to degrade because the instant voltage of the negative output waveform becomes one threshold voltage greater than that of positive output waveform where  $2\Delta V \ge V_{th}$ . When this output reaches to its maxima, the loop gain stabilizes at unity.

Figure 2.10: Output voltage saturation

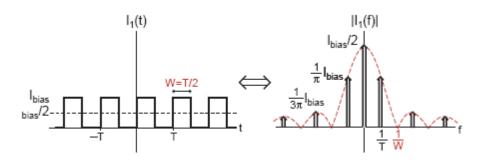

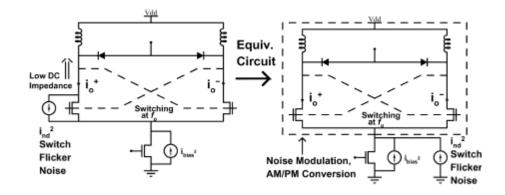

Since the output waveforms are symmetric, each NMOS transistor conducts only in half cycle so the characteristic of current can be illustrated as a square wave for each one [4]. By the Fourier series expansion, all the frequency components of the current can be obtained as depicted in Fig. 2.11. At zero frequency or DC, the value of the current corresponds to the mean value of the square waveform in time domain. The current at the fundamental frequency (1/T) of the double-sided spectrum is expressed  $(1/\pi)I_{\text{bias}}$ . DC and other harmonics of the current is filtered by the LC tank so the amplitude of the output waveforms is expressed as

$$v_o = \frac{2}{\pi} I_{bias} R_p \tag{2.10}$$

Figure 2.11: Current waveform of a switching transistor in NMOS cross-coupled LC oscillator in time and frequency domain

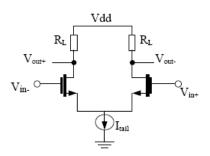

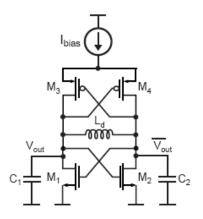

#### 2.3.3.2 CMOS Cross-Coupled LC Oscillator

CMOS cross-coupled LC oscillator comprises a PMOS differential pair additional to NMOS-only structure. This type enables the implementation of only one inductance. In this case, the inductor is driven differentially resulting in a higher quality factor than a single ended one. For the symmetry of the outputs, the parallel resistance of the tank seen from both sides must have equal values. Otherwise, the phase noise of the circuit increases. To prevent this, if the inductor provided in the design is nonsymmetrical, two inductances in series must be chosen instead.

This topology provides twice higher output voltage since the current is reused in PMOS pair. During the rise of  $V_{out}$ ,  $M_2$  eventually enters into triode and  $M_1$  goes to cut-off region and also PMOS transistors behave similarly, but conversely.  $M_4$  conducts and  $M_2$  goes off. Therefore, the current drawn from the bias transistors flows through  $M_3$  then through the LC tank and lastly through the  $M_2$  to the ground so in each half cycle, the current flows on both of two parallel loss resistances of the

tank. Hence, the output waveform is doubled compared to NMOS cross-coupled topology. According to Leeson's formula, this rise corresponds to an improvement on the phase noise at a maximum value of 6dBc/Hz.

Figure 2.12: Top biased CMOS cross-coupled LC oscillator

The PMOS switching pair also generates a negative resistance of  $2/Gm_3$  and this resistance is added to negative NMOS resistance in series. Therefore, in steady state, the CMOS structure attains a negative resistance of  $(-2/G_{m1}-2/G_{m3})$ . In order to generate symmetrical outputs, the transconductance of PMOS and NMOS transistors must be equal so the overall negative resistance equals to  $-4/Gm_1$ . Recalling the negative resistance value obtained or the NMOS cross-coupled topology the addition of PMOS pair relaxes the start-up condition by a factor of two for a given bias current.

Furthermore, the PMOS and NMOS transistors having equal transconductance result in a more symmetric waveform than in NMOS cross-coupled topology. This improvement on rise and fall time symmetry reduces the upconversion of the transistor's flicker noise to close-in frequencies [3]. Consequently, this topology achieves a better  $1/f^3$  phase noise performance than an NMOS topology. According to [5], the phase noise in  $1/f^2$  is also reduced in this topology although the PMOS pair also adds thermal noise which is the main source of the phase noise in this region. This behavior is attributed to a smaller noise coefficient  $\gamma$  because of a smaller DC voltage drop across the channels.

The main drawback of this topology is the output swing limitation. In an NMOS cross-coupled topology with an NMOS bias transistor, the output is biased at  $V_{dd}$  and taking the voltage headroom of the bias transistor into account, the maximum voltage swing at each output waveform is ( $V_{dd}$ - $V_{od}$ ). In a CMOS cross-coupled topology with

PMOS or NMOS bias transistor, the maximum output swing reduces to  $(V_{dd}-V_{od})/2$ . However, the output voltage biased at the supply voltage makes the oscillator very susceptible to the fluctuations at the supply voltage.

In CMOS topology, the addition of the PMOS transistor contributes a considerable parasitic capacitance added to the capacitor in the tank. Depending on the bias current, the ratio of PMOS to NMOS transistor dimensions may be as high as four times to equalize transconductance of the complementary transistors. Even though transconductance requirement is reduced in CMOS topology, the total intrinsic capacitance may constitute a significant part of the total capacitor of the tank. Therefore, the decline in the value of the tunable capacitor will constrain the tuning range of the oscillator.

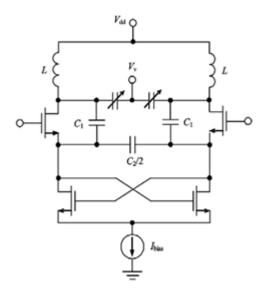

### 2.3.4 Colpitts Oscillator

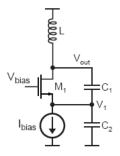

The Colpitts type is a good example of one transistor LC oscillator category. Recalling the two-port network model in Fig 3.1, one transistor whose drain is connected to an LC tank can be fed back to gate or source. Since the tank has no phase difference between its voltage and current at resonant frequency, the signal must return to the source of the transistor to accomplish a phase shift of zero in total. Hence, one transistor oscillator is realized. However, a direct feedback from the drain to the source leads to two severe problems. Firstly, the impedance seen from the source (1/g<sub>m</sub>) significantly degrades the quality factor of the tank. This impedance combines with the parallel loss resistance of the tank in parallel. The total parallel loss of the tank decreases and gets lower than 1/gm because this resistive load of the transistor is smaller than the loss of the tank. Consequently, the loaded quality factor of the tank degrades as the total parallel loss drops. Secondly, the loop gain 1/gmRploaded falls below unity showing that the start-up condition cannot be met thereby making the network impossible to oscillate. To cope with these two issues, an impedance transformer can be added to the network. One solution of transforming the impedance to a higher value is via the usage of a capacitive or inductive divider. If the tank is employed with a capacitive divider, the circuit is called a Colpitts oscillator; whereas the circuit including an inductive divider is called a Hartley oscillator. In IC technology, it is much more practical to design Colpitts type rather than Hartley to get rid of the implementation of one inductance more.

Figure 2.13: Single ended Colpitts oscillator

Fig 2.13 shows the basic structure of a Colpitts oscillator. The parallel resonant tank comprises L and the parallel combination of  $C_1$  and  $C_2$ . The loop circuit is realized with a common gate stage and the capacitors.

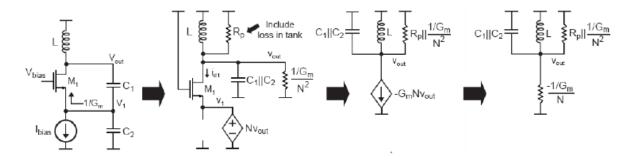

Figure 2.14: Negative Gm Analysis of Colpitts oscillator

Fig. 2.14 illustrates this transformation step by step. In a lossless step down transformer with a ratio of 1:N, the parallel resistance increases by  $1/N^2$  and in a Colpitts oscillator the capacitive divider has a ratio of

$$N = \frac{C_1}{C_1 + C_2}$$

(2.10)

Here, for the simplicity of calculations it is assumed the impedances of the capacitors are less than the source impedance  $1/g_m$  so the voltage ratio is determined only by the capacitors. The capacitive divider transforms the parallel resistance of the source impedance to  $(1+C_1/C_2)^2/g_m$ . This impedance in parallel with  $R_p$  defines the total parallel resistance of the tank. Besides, the relationship between the source (or the input) voltage  $NV_{out}$  and the drain current can be resulted to  $-G_mNV_{out}$  as the expression of output current, therefore, the output impedance is converted to a negative resistor:  $-1/G_mN$ .

On the other hand, the addition of capacitive divider concludes to a higher  $g_m$  value in order to meet oscillation start-up condition. Firstly, assuming parallel loss resistance of the tank is higher than the drain impedance of the resistance,  $R_{eq}$  is now equal to  $R_p$ . Secondly, according to [3], the ratio N is chosen as 1/5 for the best noise performance. In these cases, from one-port view of oscillators we obtain the below equation:

$$R_p = \frac{1/G_m}{N} = \frac{1/G_m}{5}$$

(2.11)

in steady-state oscillation. In other words, assuming the start-up loop gain as 2,  $g_m$  must be at least 2N times more than  $1/R_p$  to achieve sustained oscillation. This is an important drawback in oscillator design. The transistor width must be increased to get a higher  $G_m$  value for a constant bias current. This leads to higher transistor thermal noise and lower tuning range because of greater parasitic capacitances.

The differential output can be provided by combining two identical single-ended oscillators as shown in Fig 2.15. If the circuit is perfectly matched, both sides carry out of phase signals of equal amount. In this case, source to ground capacitor shared by two sides behaves like a virtual ground since the differential signals cancel each other at that midpoint. The differential operation is guaranteed unless this midpoint is connected to the ground [6]. Compared with the single ended topology the power consumption is doubled if the device values are kept.

Figure 2.15: Differential Colpitts oscillator

Because of the push-pull operation of the transistors, DC current is drawn from current sources only during a half period from current sources so they can be replaced with one current source which is able to switch the current after each half period. This can be accomplished with a pair of cross-coupled NMOS transistors. This structure shown in Fig. 2.16 provides a synchronized current switching from one side to another, and also negative resistance generated by the cross-coupled pair relaxes the oscillation start up condition.

Figure 2.16: Current shifting differential Colpitts Oscillator [6]

Similar to the above oscillator, the circuit in Fig 2.17 can also be implemented to eliminate the tough start-up condition of a conventional differential Colpitts oscillator. The idea comes from a floating gate voltage. One way to raise  $G_m$  is to increase the voltage between gate and source. Instead of an AC grounded gate, the signal as the inverted voltage of the source can be applied to the gate of the transistor. If one replica of one transistor is added and the gate terminals of these blocks are coupled crosswise,  $G_m$  requirement will be relaxed. In this new differential Colpitts topology, negative conductance is increased by a factor of  $(2+C_2/C_1)$  or 1+A where A is called  $G_m$  boosting factor of the proposed Colpitts oscillator [7]. Two current sources can be combined using two transistor added in cascade way. Their gates are connected to the outputs of the oscillator in order to relax voltage headroom requirements.

Figure 2.17: Gm Boosted differential Colpitts oscillator [7]

# **3. OSCILLATOR NOISE**

In this chapter, the oscillator phase noise is focused on. After a brief definition of the phase noise and its effect on RF transceivers, the expressions of two phase noise models are obtained via a step by step transformation methodology, also, by explaining the underlying approaches; LTV and LTI. The phase noise expressions are commented to provide practical conclusions. This topic ends with a very detailed and useful analysis of the phase noise sources in a cross-coupled LC VCO.

# 3.1 General Definition

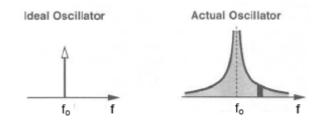

There are two kinds of noise classes affecting the response of a voltage controlled oscillator. The extrinsic noise is generated by the other blocks that are working with VCO such as the loop filter producing the control voltage of a VCO and the frequency divider in a PLL. The intrinsic noise is created by the physical structure and the process dependency of the active and passive devices in the oscillator. The noise injected from both types may disturb both the frequency and the amplitude of the output signal. The noise in the amplitude is generally negligible because the non-linearity characteristic of the active device stabilizes the amplitude's noise. The phase noise, on the other hand, is essentially a random deviation in frequency which can also be viewed as a random variation in the zero crossing points of the time-dependent oscillator waveform. It is also one of the main determinants on the VCO specifications. In time domain, phase noise is defined as jitter. Fig 3.1 shows the phase noise and its correspondence in time domain.

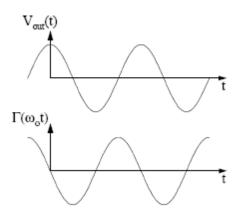

Figure 3.1: Phase noise in time and frequency domain

Let  $x(t) = \operatorname{Acos}[\omega_o t + \varphi_n(t)]$  where A is the noiseless oscillator amplitude,  $\omega_o$  is the oscillation frequency,  $\varphi_n(t)$  is the phase noise, x(t) is the sinusoidal oscillator output signal. x(t) can be extracted as  $\operatorname{A}[\cos(\omega_o t)\cos(\varphi_n(t))-\sin(\omega_o t)\sin(\varphi_n(t))]$  and for very small values of  $|\varphi_n(t)|$ ,  $x(t)\approx\operatorname{Acos}(\omega_o t)-\operatorname{A}\varphi_n(t)$  since  $\cos(\varphi_n(t))\approx\cos(0)=1$  and  $\sin(\varphi_n(t))\approx\sin(0)=\varphi_n(t)$ . Therefore, the spectrum of phase noise is translated to the oscillation frequency. However, the tank in the oscillator can filter the out of band signals only to some degree. Its filtering capability increases as the signals move farther from the oscillation frequency  $\omega_o$ . Consequently, the phase noise around the oscillation frequency is shaped like skirts in the frequency domain (Fig. 3.2).

Figure 3.2: Spectrums of output waveforms of an ideal and a real oscillator

To measure the phase noise, the noise at a distance or an offset of  $\Delta \omega$  away from the carrier frequency integrated over a 1Hz bandwidth is defined. The ratio of this noise power to the carrier power in logarithmic scale gives the phase noise at  $\Delta \omega$  offset.

$$L(\Delta\omega) = 10 \log\left(\frac{P_{tone}(\Delta\omega, 1Hz)}{P_{carrier}}\right)$$

(3.1)

where  $P_{tone}(\Delta \omega, 1Hz)$  represents the unity bandwidth noise power at  $\Delta \omega$  and  $P_{carrrier}$  is the power of the carrier.  $L(\Delta \omega)$  denoted by dBc/Hz simply points out how many dB this noise power is below the carrier power.

### **3.2 Impact of Phase Noise on Transceiver Architectures**

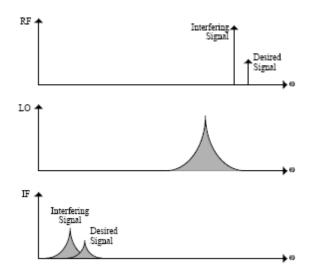

In a front-end part of a transceiver, the signal delivered from the antenna is downconverted to a lower intermediate frequency without any change in shape by the local oscillator. In the presence of a strong interferer standing close to the desired signal, the local oscillator downconverts both. The phase noise skirts of the LO modulates onto the strong interferer and this cause the overlapping of two signals at IF as depicted in Fig. 3.3, thereby, this reduces the signal-to noise ratio (SNR) of the desired signal at IF. This effect is also called the reciprocal mixing.

Figure 3.3: Effect of phase noise in receivers

In the transmitter part, the phenomenon is quite similar. A strong interferer modulated by the local oscillator attains a widening spectrum as the offset increases since it is amplified by the PA. Its skirts extend over the desired signal in the receiver part and corrupt it. This effect also causes an extravagant consumption of out of band energy.

Figure 3.4: Effect of phase noise in transmitters

## 3.3 Phase Noise Models

In literature, there exist two phase noise models depending on different system approaches for oscillators.

# 3.3.1 Leeson's Phase Noise Model

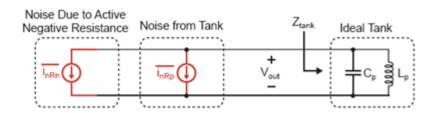

Considering one-port view of an oscillator, the intrinsic noise sources can be put in two categories; the noise of the resonator and the noise of the active negative resistance generator. The loss of the passive elements in the tank falls into the first category. The thermal and the flicker noise of the active device are the main sources of the latter category. However, only the thermal noise of the active part is attributed to this category since it is assumed as a negative resistance in the model of two oneport.

Figure 3.5: One-port view of LC oscillator with noise sources

The one port view of an LC oscillator with noise sources can be illustrated as in Fig. 3.5 to determine how these categories affect the phase noise of the oscillator. Here, the tank is realized as an ideal one because the loss of the tank is compensated by the active circuitry.

The input impedance of the tank at the frequency  $\omega$  is simply expressed as

$$Z(\omega) = \frac{j\omega L_p}{1 - \omega^2 j\omega L_p C_p}$$

(3.2)

The above expression can be rewritten for the frequency  $\omega = \omega_o + \Delta \omega$  where  $\omega_o$ , the oscillation frequency is equal to  $1/\sqrt{L_p C_p}$  and  $\Delta \omega$  is the offset frequency

$$Z(\Delta\omega) = \frac{j(\omega_o + \Delta\omega)L_p}{1 - (\omega_o + \Delta\omega)^2 j\omega L_p C_p}$$

(3.3)

After the expansion of the square term in the denominator part, we get

$$Z(\Delta\omega) = \frac{j(\omega_o + \Delta\omega)L_p}{1 - \omega_o^2 L_p C_p - 2\Delta\omega(\omega_o L_p C_p) - \Delta\omega^2 L_p C_p}$$

(3.4)

Since  $1 - \omega_o^2 L_p C_p = 0$  and  $\Delta \omega^2 L_p C_p$  is negligible, the expression can be simplified to

$$Z(\Delta\omega) \approx \frac{j(\omega_o + \Delta\omega)L_p}{-2\Delta\omega(\omega_o L_p C_p)}$$

(3.5)

Taking into account that  $\omega_o \gg \Delta \omega$ , the numerator part of the expression can be simplified to

$$Z(\Delta\omega) \approx -\frac{j}{2} \frac{1}{C_p} \left(\frac{\omega_o}{\Delta\omega}\right)$$

(3.6)

The quality factor of the tank due to the parallel resistance  $R_p$  is equal to  $\omega_o R_p C_p$  so we can parameterize the ideal tank impedance in terms of Q of the actual tank as

$$Z(\Delta\omega) \approx -\frac{j}{2} \frac{R_p}{Q} \left(\frac{\omega_o}{\Delta\omega}\right)$$

(3.7)

By squaring both sides we reach the expression below in terms of  $\Delta \omega$  away from center frequency;

$$|Z_{tank}(\Delta\omega)|^2 \approx \left(\frac{R_p}{2Q}\frac{\omega_o}{\Delta\omega}\right)^2$$

(3.8)

At this point, it is possible to derive an expression for the total output noise with respect to offset frequency

$$\frac{\overline{v_{out}^2}}{\Delta\omega} = \left(\frac{\overline{i_{nRp}^2}}{\Delta\omega} + \frac{\overline{i_{nRn}^2}}{\Delta\omega}\right) |Z_{tank}(\Delta\omega)|^2$$

(3.9)

The above expression includes both the amplitude and phase noise of the oscillator. After arranging the expression we get,

$$\frac{\overline{v_{out}^2}}{\Delta\omega} = \frac{\overline{i_{nRp}^2}}{\Delta\omega} \left( 1 + \frac{\overline{i_{nRn}^2}}{\Delta\omega} / \frac{\overline{i_{nRp}^2}}{\Delta\omega} \right) |Z_{tank}(\Delta\omega)|^2$$

(3.10)

The term in large brackets called  $F(\Delta \omega)$  is defined by

$$F(\Delta\omega) = \left(1 + \frac{\overline{i_{nRn}^2}}{\Delta\omega} / \frac{\overline{i_{nRp}^2}}{\Delta\omega}\right) = \frac{\text{total noise in tank at } \Delta\omega}{\text{noise in tank due to tank loss at } \Delta\omega}$$

(3.11)

Since  $i_{nRp}^2/\Delta\omega$  equals to  $4kT/R_p$  for the single-sided spectrum, the output noise spectrum density due to tank loss is

$$\frac{\overline{v_{out}^2}}{\Delta\omega} = \frac{\overline{i_{nRp}^2}}{\Delta\omega} F(\Delta\omega) |Z_{tank}(\Delta\omega)|^2 = 4kTF(\Delta\omega)R_p \left(\frac{1}{2Q}\frac{\omega_o}{\Delta\omega}\right)^2$$

(3.12)

According to equipartition theorem, if the output signal is a sinusoidal wave, the noise impact splits equally into amplitude and phase [8].

$$\frac{\overline{v_{out}^2}}{\Delta\omega}\Big|_{PHASE} = 2kTF(\Delta\omega)R_p \left(\frac{1}{2Q}\frac{\omega_o}{\Delta\omega}\right)^2$$

(3.13)

From the above equation, the phase noise is expressed as:

$$L(\omega) = 10 \log(S_{noise}(\Delta \omega)/P_{sig}) = 10 \log\left(\frac{1}{R_p} \frac{\overline{v_{out}^2}}{\Delta \omega}\Big|_{PHASE} / P_{sig}\right)$$

(3.14)

$$L(\omega) = 10 \log \left( \frac{2kTF(\Delta\omega)}{P_{sig}} \left( \frac{1}{2Q} \frac{\omega_o}{\Delta\omega} \right) \right)^2$$

(3.15)

The two noise contributors have the same phase noise spectral density since they have equal absolute resistance values. Hence,  $F(\Delta \omega) = 2$  and the system's phase noise is defined by

$$L(\omega) = 10 \log \left( \frac{4kT}{P_{sig}} \left( \frac{1}{2Q} \frac{\omega_o}{\Delta \omega} \right) \right)^2$$

(3.16)

The above equation corresponds to -20dBc/Hz change of phase noise per decade. In reality, this is not completely true because the noise of the active negative resistance generator is more sophisticated. In the derivation of the equation, since switching transistors are modeled as resistors, they only generate thermal noise. However, recalling a cross-coupled topology, firstly, the flicker noise of all transistors must also be considered. Secondly, the noise of the bias transistor is modulated on to the output voltage. Thirdly, the noise is influenced during switching operation of cross-coupled transistors. Fourthly, and last, these transistors while operating in triode region may have low output impedance and therefore, result in a drop-off on the quality factor of the tank.

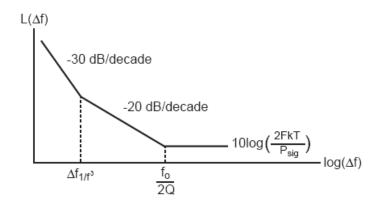

Figure 3.6: Phase noise spectrum of an actual oscillator

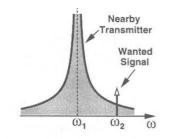

The phase noise spectrum of an actual oscillator is shown above. At low offset frequencies, the phase noise degrades -30 dB/decade. Then, for a wide range of offset frequency, the slope is fixed to -20 dB/decade. At a very high offset, the noise floor forms and the slope flattens.

Leeson proposes a semi-emprical formula of the phase noise satisfying both the basic phase noise equation 3.16 and the characteristic of the phase noise spectrum of an oscillator. He assumes that  $F(\Delta \omega)$  is independent of frequency and describes F as an empirically-determined parameter.

$$L(\omega) = 10 \log\left(\frac{2kTF}{P_{sig}}\left(1 + \left(\frac{1}{2Q}\frac{\omega_o}{\Delta\omega}\right)^2\right)\left(1 + \frac{\Delta\omega_{1/f^3}}{|\Delta\omega|}\right)\right)$$

(3.17)

where  $\Delta \omega_{1/f^3}$  is the boundary frequency between  $1/f^2$  and  $1/f^3$  regions. It is assumed that this parameter is equal to noise corner frequency of the device.

Examining (3.17), it is indicated that the phase noise is inversely proportional to the average power dissipated in the tank resistance and second order of the quality factor. Therefore, the phase noise performance can be improved by increasing the oscillation voltage amplitude and choosing higher Q inductors among possible alternatives.

## 3.3.2 Lee and Hajimiri's Phase Noise Model

It is clear that the Lesson's model does not reveal the impact of all noise sources on phase because this model is based on empirical fitting parameters such as F and  $\Delta \omega_{1/f^3}$ . In general,  $\Delta \omega_{1/f^3}$  is not equal to 1/f corner frequency, thus it should be measured before calculating the phase noise. Furthermore, in the case of more than

one active device contributing 1/f noise, no information is mentioned about whose 1/f corner frequency will determine  $\Delta \omega_{1/f^3}$ . Also, according to Leeson's formula higher Q values lead to a better phase noise performance, but boosting Q of the tank increases F factor as well [9]. As a result of these drawbacks, Leeson's phase noise equation needs to be revisited. Lee and Hajimiri first observed the impulse response of an ideal oscillator in order to model the noise of an oscillator (Fig. 3.7).

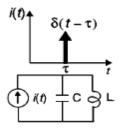

Figure 3.7: Ideal LC oscillator stimulated by a current pulse

Fig. 3.8 shows how an impulse of current affects the response of a lossless resonator at different times. If an impulse is injected at the peak of the signal, it only causes a change in the amplitude with an amount of  $\Delta V=\Delta Q/C$  where  $\Delta Q$  denotes the total charge variation across the resonator; no variation in phase. On the other hand, if an impulse is injected at the zero crossing of the signal, there occurs an influence only in the phase, not in the amplitude. The injection of current pulse during any other time period impacts the amplitude of the output signal and also shifts the zero crossing point of the oscillation. The amount of phase disturbance for a given injected impulse depends on the time in which when the injection occurs; an oscillator is therefore a periodically time-varying (LTV) system [9]. It is also linear since the amount of amplitude disturbance depends on the amplitude of the impulse current [10].

Figure 3.8: Impulse effects on a sinusoidal output waveform

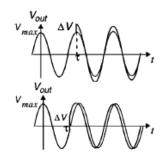

As mentioned earlier, the amplitude variations are generally ignored because the gain control mechanism of the oscillator, as a result of nonlinearity, alleviates them over time as depicted in Fig. 3.9.

Figure 3.9: Damping of amplitude variation in one oscillation cycle

Therefore, according to this theory, for a minimal phase noise, any noise impulse must coincide in time with the peaks of the output voltage.

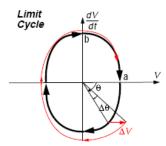

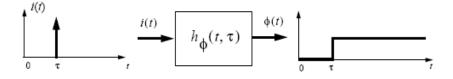

Figure 3.10: Characteristic of an impulse response in time domain

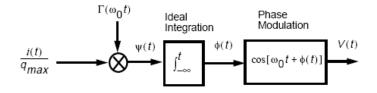

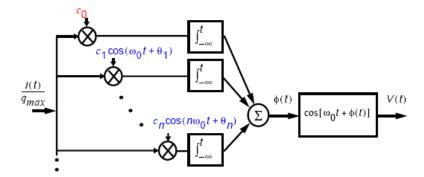

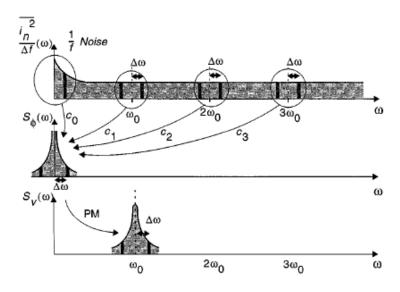

Fig 3.10 depicts the impulse response in time domain. Since an impulse produces a step change in phase, the phase impulse response of the oscillator can be expressed as

$$h_{\varphi}(t,\tau) = \frac{\Gamma(\omega_0 \tau)}{q_{max}} u(t-\tau)$$

(3.18)

where u(t) is the unit function.  $\Gamma(x)$  is called impulse sensitivity function (ISF). It is an amplitude and frequency independent, dimensionless function periodic in  $2\pi$ . It describes how much phase change occurs from applying an impulse at time: t=T·x/2 $\pi$ . It is roughly equal to the derivative of the output voltage waveform as seen in Fig 3.11 illustrating the ISF function of an LC oscillator.