# **ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL**

# APPROXIMATE ARTIFICIAL NEURAL NETWORK HARDWARE AWARE SYNTHESIS TOOL

Ph.D. THESIS

Mohammadreza ESMALI NOJEHDEH

**Department of Electronic & Communication Engineering**

**Electronic Engineering Programme**

**JULY 2021**

# **ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL**

# APPROXIMATE ARTIFICIAL NEURAL NETWORK HARDWARE AWARE SYNTHESIS TOOL

## **Ph.D. THESIS**

## Mohammadreza ESMALI NOJEHDEH (504162212)

**Department of Electronic & Communication Engineering**

**Electronic Engineering Programme**

Thesis Advisor: Assoc. Prof. Dr. Mustafa ALTUN

**JULY 2021**

# <u>İSTANBUL TEKNİK ÜNİVERSİTESİ ★ LİSANSÜSTÜ EĞİTİM ENSTİTÜSÜ</u>

# YAKLAŞIK YAPAY SİNİR AĞI İÇIN DONANIMA DUYARLI SENTEZ ARACI

# DOKTORA TEZİ

## Mohammadreza ESMALI NOJEHDEH (504162212)

Elektronik ve Haberleşme Mühendisliği Anabilim Dalı

Elektronik Mühendisliği Programı

Tez Danışmanı: Assoc. Prof. Dr. Mustafa ALTUN

**TEMMUZ 2021**

Mohammadreza ESMALI NOJEHDEH, a Ph.D. student of ITU Graduate School student ID 504162212, successfully defended the dissertation entitled "APPROXIMATE ARTIFICIAL NEURAL NETWORK HARDWARE AWARE SYNTHESIS TOOL", which he prepared after fulfilling the requirements specified in the associated legislations, before the jury whose signatures are below.

| Thesis Advisor : | Assoc. Prof. Dr. Mustafa ALTUN<br>Istanbul Technical University            |  |

|------------------|----------------------------------------------------------------------------|--|

| Jury Members :   | <b>Prof. Dr. Sıddıka Berna ÖRS YALÇIN</b><br>Istanbul Technical University |  |

|                  | Asst. Prof. Dr. Tuba AYHAN<br>MEF University                               |  |

|                  | Assoc. Prof. Dr. Burcu ERKMEN<br>Yıldız Technical University               |  |

|                  | Asst. Prof. Dr. İsmail ÇEVİK                                               |  |

Istanbul Technical University

Date of Submission : 26 May 2021 Date of Defense : 2 July 2021

## FOREWORD

My most sincere and special gratitude goes to my supervisor Assoc. Prof. Dr. Mustafa ALTUN. Thank you for the continuous support and extraordinary supervisory to my PhD study. It was my fortune and honor to have the great supervision from you. I would also like to thank Dr. Levent AKSOY, a friend and colleague who changed my way of thinking, my attitudes to this world and my vision to the future. I also wish to thank the members of the thesis committe; Prof. Dr. Sıddıka Berna ÖRS YALÇIN and Asst. Prof. Dr. Tuba AYHAN for their comments and valuable advice. Last but by no means least, I would give my special gratitude to my families, especially my parents. They have sacrificed so much to support my life and study. I cannot express my thankful heart to them with bare language.

July 2021

Mohammadreza ESMALI NOJEHDEH

# **TABLE OF CONTENTS**

# Page

| FOREWORDix                                                                      |

|---------------------------------------------------------------------------------|

| TABLE OF CONTENTSxi                                                             |

| ABBREVIATIONS xiii                                                              |

| LIST OF TABLES xv                                                               |

| LIST OF FIGURES xvii                                                            |

| SUMMARY xix                                                                     |

| ÖZET xxi                                                                        |

| 1. INTRODUCTION                                                                 |

| 2. APPROXIMATE COMPUTING                                                        |

| 2.1 Background and Preliminary Works                                            |

| 2.2 Ripple-Carry Adder Design                                                   |

| 2.2.1 1-bit full adder design                                                   |

| 2.2.2 n-bit ripple-carry adder design                                           |

| 2.3 Approximate Multiplier Design                                               |

| 2.3.1 Design of 1-bit approximate full adder (APFA) and half adder (APHA). 21   |

| 2.3.2 n-bit wallace-tree multiplier design                                      |

| 2.4 Experimental Results                                                        |

| 2.4.1 Area, power, delay, and energy versus average error                       |

| 2.4.2 Image processing: peak signal to noise ratio (PSNR) versus area saving 32 |

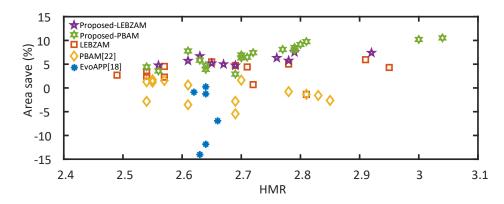

| 2.4.3 Neural network: misclassification rate versus area saving                 |

| 3. ANN HARDWARE REALIZATION                                                     |

| 3.1 Introduction                                                                |

| 3.2 Background                                                                  |

| 3.2.1 ANN basics                                                                |

| 3.2.2 Multiplierless constant multiplications                                   |

| 3.2.3 Related work                                                              |

| 3.3 Design Architectures                                                        |

| 3.3.1 Parallel design                                                           |

| 3.3.2 Time-Multiplexed design                                                   |

| 3.3.2.1 SMAC_NEURON ARCHITECTURE                                                |

| 3.3.2.2 SMAC_ANN ARCHITECTURE                                                   |

| 3.4 Finding the Minimum Quantization Value                                      |

| 3.5 ANNs Under the Shift-Adds Architecture                                      |

| 3.5.1 Multiplierless ANN design under the parallel architecture                 |

| 3.5.2 Multiplierless ANN design under the time-multiplexed architectures 46     |

| 3.6 SIMURG: The CAD Tool                                                        |

| 3.7 Experimental Results                                                        |

| 4. EFFICIENT HARDWARE REALIZATION OF ANNS BY APPROXI- |    |

|-------------------------------------------------------|----|

| MATE BLOCKS                                           | 55 |

| 4.1 Introduction                                      | 55 |

| 4.2 Approximate Blocks for ANN                        | 56 |

| 4.2.1 Approximate adders                              | 56 |

| 4.2.2 Approximate multipliers                         |    |

| 4.2.3 Approximate level                               |    |

| 4.2.3.1 SMAC_NEURON                                   |    |

| 4.2.3.2 <i>SMAC_ANN</i>                               |    |

| 4.3 Experimental Results                              |    |

| 4.3.1 Pen-digit problem                               |    |

| 4.3.2 MNIST problem                                   |    |

| 5. CONVOLUTION LAYER                                  |    |

| 5.1 Introduction                                      | 75 |

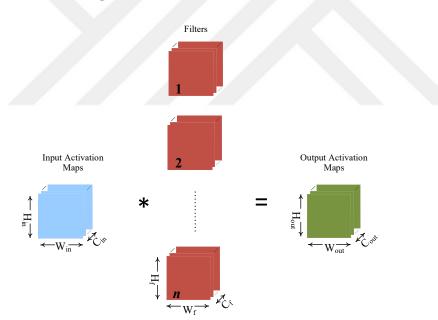

| 5.1.1 Convolution layer                               | 76 |

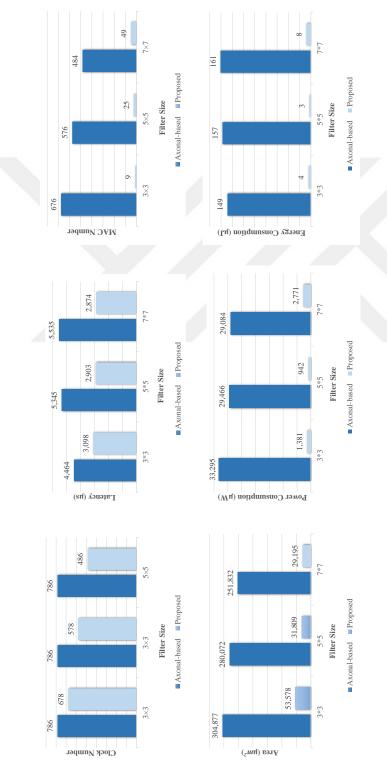

| 5.2 Experimental Results                              | 81 |

| 6. CONCLUSIONS                                        |    |

| REFERENCES                                            | 87 |

|                                                       | 95 |

# ABBREVIATIONS

| AAL    | : Adders Approximation Level                 |

|--------|----------------------------------------------|

| ANN    | : Artificial Neural Network                  |

| APAD   | : Approximate Adder                          |

| ASIC   | : Application-Specific Integrated Circuit    |

| BNN    | : Binary Neural Networks                     |

| BHA    | : Behavioral Accuracy                        |

| CAD    | : Computer Aided Design                      |

| CAVM   | : Constant Array-Vector Multiplication       |

| Cin    | : Carry In                                   |

| CMVM   | : Constant Matrix-Vector Multiplication      |

| CMOS   | : Complementary Metal-Oxide Semiconductor    |

| CNN    | : Convolutional Neural Networks              |

| Cout   | : Carry Out                                  |

| CPU    | : Central Processing Unit                    |

| CSD    | : Canonical Signed Digit                     |

| DBR    | : Digit-Based Recoding                       |

| EAAED  | : Estimated Average Absolute Error Distance  |

| EXAD   | : Exact Adder                                |

| FA     | : Full Adder                                 |

| FPGA   | : Field Programmable Gate Array              |

| GPU    | : Graphics processing Unit                   |

| HA     | : Half Adder                                 |

| HAC    | : Hardware Accuracy                          |

| HMR    | : Hardware Misclassification Rate            |

| ΙΟΤ    |                                              |

| LEBZAM | 8                                            |

| LLS    | : Largest Left Shift value                   |

| MAC    | : Multiply Accumulate unit                   |

| MCM    | : Multiple Constant Multiplication           |

| MLP    | : Multilayer Perceptrons                     |

| MR     | : Misclassification Rate                     |

| PBAM   | : Probabilistic Based Approximate Multiplier |

| PDP    | : Power-Delay Product                        |

| PSNR   | : Peak Signal-to Noise Ratio                 |

| RNN    | : Recurrent Neural Networks                  |

| SCM    | : Single Constant Multiplication             |

| SLS    | : Smallest Left Shift value                  |

| SMAC   | : Single Multiply Accumulate unit            |

| SMAC   |                                              |

| SNAC   | : Static Random-Access Memory                |

# LIST OF TABLES

# Page

| Table 2.1         | : Truth table of sample approximate adders                              | 7  |

|-------------------|-------------------------------------------------------------------------|----|

| Table 2.2         | : Truth tables of exact and approximate 1-bit adders                    | 13 |

| Table 2.3         | : Calculation of $E_i$ for example 1                                    |    |

| Table 2.4         | : Values of $E_i$ 's for different APAD combinations                    | 17 |

| Table 2.5         | : Synthesis of 8-bit adders                                             |    |

| Table 2.6         | : Truth table of the proposed approximate full Adder APFA               | 23 |

| Table 2.7         | : Truth table of the proposed approximate half adder APHA               | 24 |

| Table 2.8         | : 1-Bit adder results.                                                  |    |

| Table 2.9         | : 8-Bit adder results.                                                  | 30 |

| <b>Table 2.10</b> | : 8-Bit×8-Bit multiplier results                                        | 31 |

| <b>Table 2.11</b> | : Neural network misclassification rates for different area savings     | 34 |

| Table 3.1         | : Details of ANNs on training and hardware design.                      | 49 |

| Table 4.1         | : SMAC_NEURON using approximate multipliers                             | 65 |

| Table 4.2         | : SMAC_NEURON using approximate multipliers and adders                  | 66 |

| Table 4.3         | : SMAC_ANN using approximate multipliers                                | 67 |

| Table 4.4         | : SMAC_ANN using approximate multipliers and adders                     | 68 |

| Table 4.5         | : SMAC_ANN for 668-128-10 structure.                                    | 72 |

| Table 4.6         | : SMAC_NEURON for 668-128-10 structure                                  | 73 |

| Table 4.7         | : SMAC_NEURON for 668-256-256-256-10 structure                          | 74 |

| Table 5.1         | : The <i>axonal-based</i> model data flow for convolutional computation | 79 |

| Table 5.2         | : The proposed method data flow for convolutional computation           | 80 |

# LIST OF FIGURES

# Page

| Figure 2.1  | : Ripple carry adder structure                                      | 7    |

|-------------|---------------------------------------------------------------------|------|

| Figure 2.2a | : APAD1                                                             | . 12 |

| Figure 2.2b | : APAD2                                                             | . 12 |

| Figure 2.2c | : APAD3                                                             | . 12 |

| 0           | : APAD4                                                             |      |

| Figure 2.2  | : Karnough Maps of APADs.                                           | . 12 |

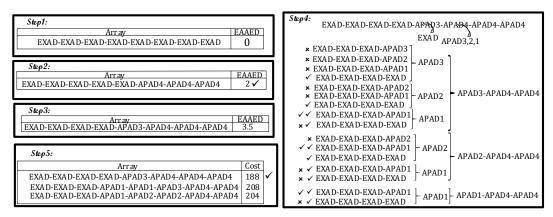

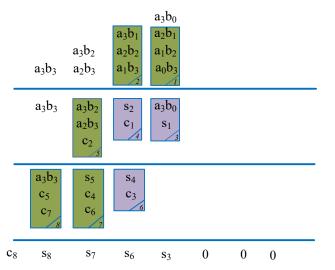

| Figure 2.3  | : Demonstration of steps for example 3                              | . 18 |

|             | : 4×4 bit exact wallace-tree multiplier                             |      |

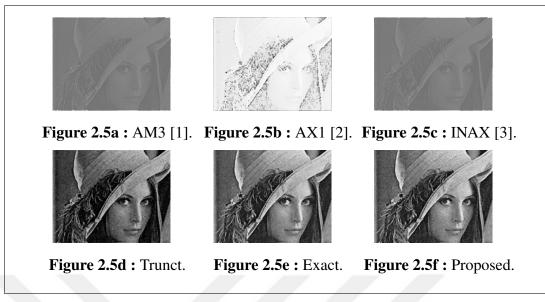

| Figure 2.5a | : AM3 [1]                                                           | . 33 |

|             | : AX1 [2].                                                          |      |

| Figure 2.5c | : INAX [3].                                                         | . 33 |

| Figure 2.5d | : Trunct.                                                           | . 33 |

| Figure 2.5e | : Exact.                                                            | . 33 |

| Figure 2.5f | : Proposed.                                                         | . 33 |

| Figure 2.5  | : Mean filter results.                                              | . 33 |

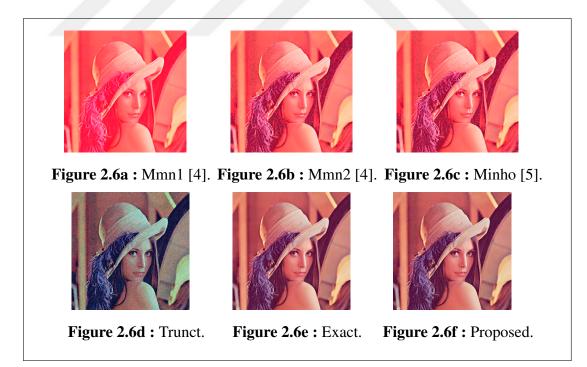

| Figure 2.6a | : Mmn1 [4].                                                         | . 33 |

| Figure 2.6b | : Mmn2 [4].                                                         | . 33 |

| Figure 2.6c | : Minho [5].                                                        | . 33 |

| Figure 2.6d | : Trunct.                                                           | . 33 |

| Figure 2.6e | : Exact.                                                            | . 33 |

| Figure 2.6f | : Proposed.                                                         | . 33 |

| Figure 2.6  | : Results for blending of two images.                               | . 33 |

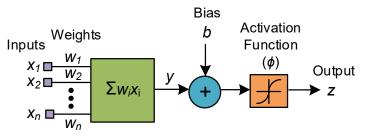

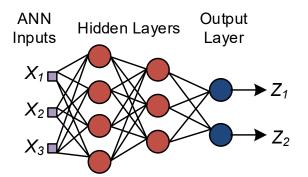

| Figure 3.1  | : Artificial neuron                                                 | . 36 |

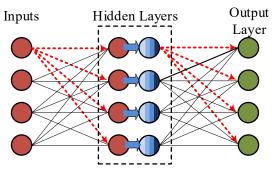

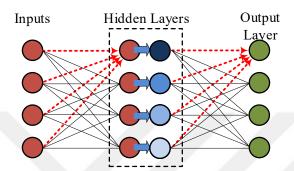

| Figure 3.2  | : ANN with two hidden layers.                                       | . 37 |

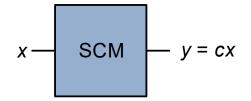

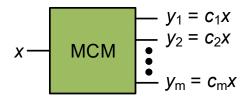

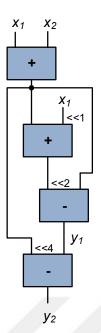

| Figure 3.3  | : Single constant multiplication (SCM).                             | . 38 |

| Figure 3.4  | : Multiple constant multiplication (MCM).                           |      |

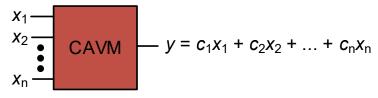

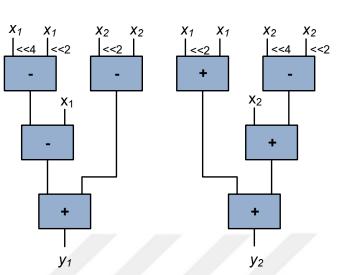

| Figure 3.5  | : Constant array vector multiplication (CAVM)                       | . 39 |

| Figure 3.6  | : Consant matrix vector multiplication (CMVM).                      | . 39 |

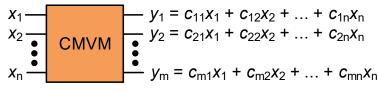

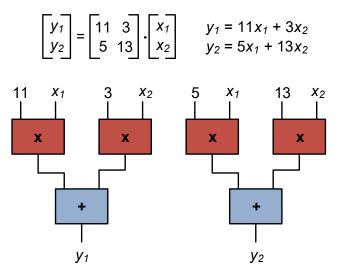

| Figure 3.7  | : Implementation of a CMVM operation.                               | . 40 |

| Figure 3.8  | : DBR method [6]                                                    | . 41 |

| Figure 3.9  | : The algorithm of [7] optimizing the number of operations.         | . 42 |

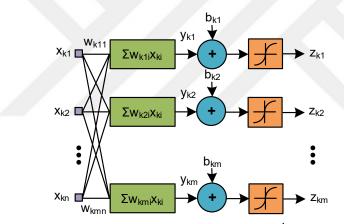

| Figure 3.10 | : Neuron computations at the $k^{th}$ layer of ANN                  | . 42 |

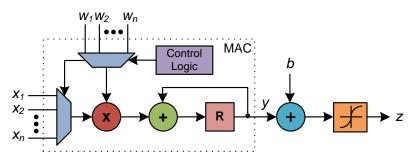

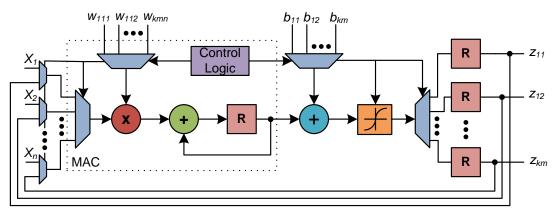

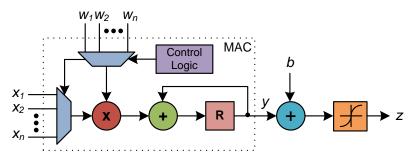

| Figure 3.11 | : Multiply-accumulate (MAC) block in the neuron computation.        | . 43 |

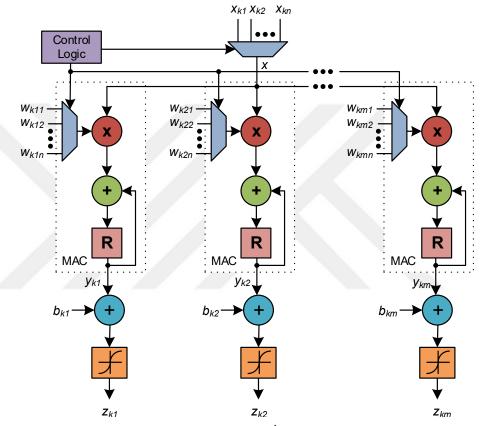

| Figure 3.12 | : Neuron computations at the $k^{th}$ layer of ANN using MAC blocks | . 43 |

| Figure 3.13 | : ANN design using a single MAC block                               | . 45 |

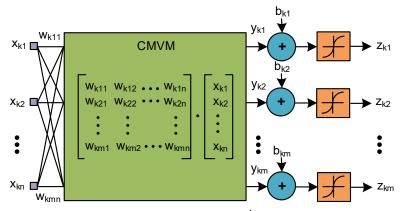

| Figure 3.14 | : Neuron computations at the $k^{th}$ layer using a CMVM block      | . 46 |

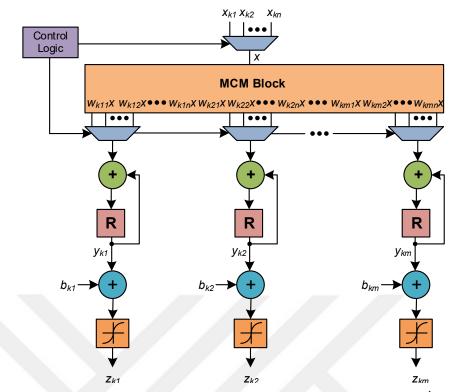

| Figure 3.15 | : Multiplierless realization of neuron computations                 | . 47 |

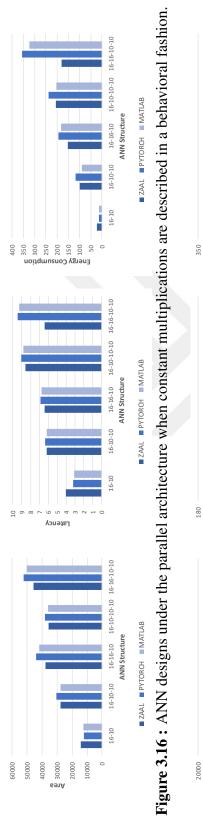

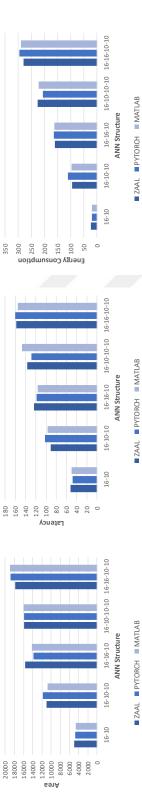

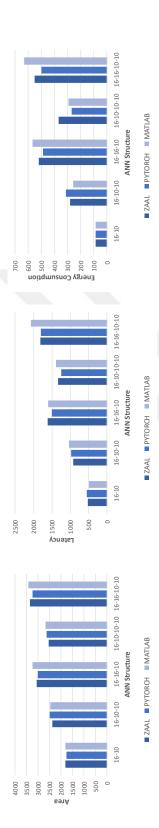

| Figure 3.16 | : ANN designs under the parallel architecture                       | . 52 |

| Figure 3.17 | : ANN designs under the SMAC_NEURON architecture            | . 52 |

|-------------|-------------------------------------------------------------|------|

| Figure 3.18 | : ANN designs under the SMAC_ANN architecture               | . 53 |

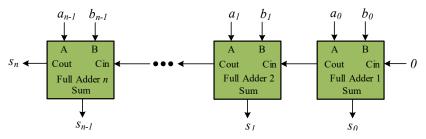

| Figure 4.1  | : Ripple carry adder                                        | . 56 |

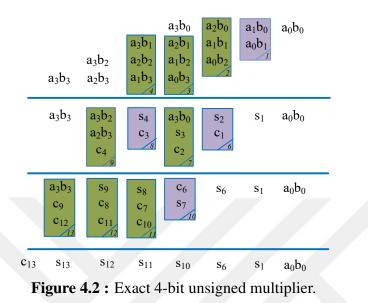

| Figure 4.2  | : Exact 4-bit unsigned multiplier                           | . 58 |

| Figure 4.3  | : Approximate 4-bit unsigned multiplier                     | . 58 |

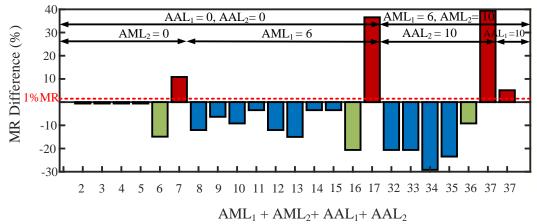

| Figure 4.4  | : Misclassification rate for SMAC_NEURONarchitecture        | . 61 |

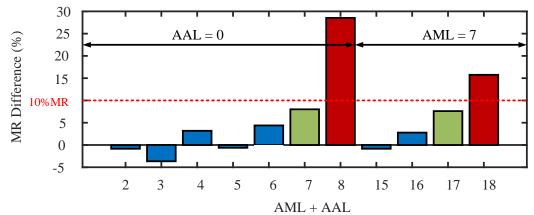

| Figure 4.5  | : Misclassification rate for SMAC_ANNarchitecture.          | . 62 |

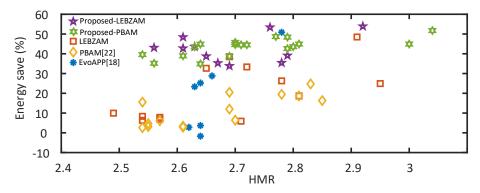

| Figure 4.6  | : Energy save percentages.                                  | . 70 |

| Figure 4.7  | : Area save percentages of ANN.                             | . 71 |

| Figure 5.1  | : Multiply-accumulate (MAC) block in the neuron computation | . 77 |

| Figure 5.2  | : Axonal-based model.                                       | . 78 |

| Figure 5.3  | : Dendritic-based model.                                    | . 78 |

| Figure 5.4  | : The computation of convolutional layer.                   | . 78 |

| Figure 5.5  | : The computation of convolutional layer.                   |      |

| Figure 5.6  | : Experimental results                                      |      |

## APPROXIMATE ARTIFICIAL NEURAL NETWORK HARDWARE AWARE SYNTHESIS TOOL

## SUMMARY

In the previous decade, artificial neural networks (ANNS) have attracted considerable attention from researchers in many areas and have become a favorite method; from business to aerospace applications.

We live in the information age where this information feeds artificial intelligence (AI). According to Forbes' estimate, over the last two years alone 90 percent of the data in the world was generated. At first glance, processing more information may seem like a dissipation of more power in central processing units(CPUs) and graphic processing units (GPUs) or spending more time to obtain the results, but for the portable systems due to limitations in battery capacity, power, and hardware area limitations, different concerns emerge. For example, less consumption of energy is vital to extend the battery supporting time for mobile devices.

The problem starts to be bold when software engineers regardless of the hardware sources (especially for portable devices) develop different ANNs architecture, where they intend to achieve a network with the best performances. Similarly, hardware engineers' AI knowledge is limited and any change within hardware design in lack of this knowledge may yield a catastrophic defect in the expected performance. As a result, this uninformed state yields a gap between the hardware and software sides of ANNs. The emerged gap provides a pitch to hardware and software researchers to play their best performance, where more information about the rival side makes their performance more eye-catching.

By obtaining this gap, the co-design method or hardware-aware training methods become prevalent recently. The object of this dissertation is also to develop a methodology to realize the ANNs with minimum hardware cost by regarding the software performance.

Limitation in hardware cost, consumed energy, and dissipated power for devices leads designers to find new architectures and approaches. Approximate computing is one of them, where this method is an useful technique for error essence systems. By leveraging the approximate level, a trade-off between the output accuracy and hardware cost is attainable. For example, assume a 1-bit exact adder costs 18 transistors, and by removing 3 transistors, a new approximate adder by 15 transistors is achievable, but the new approximate adder generates inexact results when the input is (0,0), and suppose that the results for the rest set of the inputs((0,1),(1,0),(1,1)) are correct. Therefore, the approximate adder saves 3 transistors at the cost of 1 inexact result.

Generally, approximate computing is apple of designers' eye in applications with error tolerance capability, consequently, error tolerance inherence of ANNs nominates approximate computing as a potential method to reduce the hardware complexity of ANNs. Since multipliers and adders are fundamental building blocks of ANNs, in this thesis, by introducing novel approximate multipliers and adders we replace them with exact adders and multipliers. As mentioned earlier, approximate computing is a trade-off between accuracy and hardware cost, to adjust this trade-off, we synthesized the proposed approximate blocks based on the desired error metric. Also, we proposed an equation to calculate the mean absolute error of the introduced approximate multiplier and adders. Based on our best knowledge, the proposed approximate blocks are the only ones which are synthesized based on the mean error value.

In next step, we introduced a new error metric called the approximate level to evaluate the performance of the proposed approximate blocks in ANNs. On the other hand, ANNs are made up of a lot of multipliers and adders, where the search space for the best combination of these blocks grows with the increase of bit-width or neuron numbers. To tackle this problem and by exploiting the proposed error metric, we introduce a new search algorithm to find the appropriate combination of the approximate and exact versions of the arithmetic blocks by taking into account the expected accuracy of ANNs.

Also, in this thesis we realized ANNs under different synthesis techniques to obtain the pros and cons of each approach. Since the parallel architecture requires a large area we considered the time-multiplexed architecture as the main architecture method, where computing resources are re-used in the multiply-accumulate (MAC) blocks.

As an application, the MNIST and Pen-digit database are considered. To examine the efficiency of the proposed method, various architectures and structures of ANNs are realized. Our experimental results show that exploiting the proposed approximate multipliers yields smaller area and power consumption compared to those designed using previously proposed prominent approximate multipliers. Also, according to these results, concurrent use of approximate multipliers and adders provides remarkable results in terms of hardware cost, where we obtain 60% and 40% reduction in energy consumption and occupied area of the ANN design with the same or better hardware accuracy compared to the exact adders and multipliers.

To demonstrate the proposed method's scalability, we propose an efficient method to realize a convolution layer of convolution neural networks (CNNs). Inspired by the fully-connected neural network architecture, we introduce an efficient computation approach to implement convolution operations.

## YAKLAŞIK YAPAY SİNİR AĞI İÇIN DONANIMA DUYARLI SENTEZ ARACI

## ÖZET

Yapay Sinir Ağları (YSA) geçtiğimiz on yılda pek çok alanda araştırmacılar ve yatırımcılar tarafından büyük ilgi görüyor. Forbes'in tahminine göre "Yalnızca son iki yılda dünyadaki verilerin yüzde 90'ının üretildiği" bilgi çağında yaşıyoruz. İlk bakışta, daha fazla bilginin işlenmesi CPU'larda ve GPU'larda daha fazla gücün harcanması veya sonuç elde etmek için daha fazla zaman harcanması gibi görünüyor, ancak taşınabilir sistemler için kısıtlı pil kapasitesi, güç ve donanım alanı sınırlamalar nedeniyle farklı endişeler ortaya çıkıyor. Bu sınırlamaları göz önünde bulundurarak tasarımcılar yeni mimarilere yönleniyorlar, mesela pil destek süresini uzatmak için daha az enerji tüketimi hayati önem taşır ve kullanılan mimari en az güç tüketecek şekilde tasarlanıyor.

Geleneksel olarak, bir devre veya sistem bloğunun tasarımında olası uygulamalar gözetilerek en kötü durum analizi yapılır ve sadece en yüksek doğruluk istenen uygulamaya göre tasarım yapılır. Uygulamaların ayrı ayrı gerektirdiği minimum işlem doğrulukları gözetilmez. Örnek vermek gerekirse, telefonlarımızda sıklıkla kullandığımız hesap makinesi ve fotoğraf iyileştirme/küçültme uygulamalarının ikisi için de aynı aritmetik mantık birimi (AMB) kullanılır. Oysaki hesap makinesi için AMB'nin hatasız işlem yapması elzemken, fotoğraf uygulaması için yüksek doğruluk şart değildir ve bu işlem yaklaşık hesaplama yapan bir AMB ile de yapılabilir. Böylece güç tüketimi önemli ölçüde azaltılabilir.

Önerilen tezde yaklaşık hesaplama yapabilen ve düşük güç tüketimli aritmetik devre blokları tasarlanacaktır ve bu bloklar yapay sınır ağlarında farklı doğrulukta kullanılmak üzere değişik mimarilerde kullanım özelliklerine sahip olacaktır.

Bir üst seviyede, yani sistem seviyesinde, tasarlanacak devre bloklarının seçilen mimaride nasıl en verimli şekilde kullanılacağının/yapılandırılacağının belirlenmesi gerekmektedir ve bu oldukça zor bir problemdir. İçerisinde n adet aritmetik işlem bloku bulunan ve her bir işlem blokunun m adet yapılandırılabilir seviyesi olan bir sistem için, optimum çözüm en kötü halde  $m^n$  değişik durumu gözetilerek bulunur. Çözüm bulmak için brute-force (kaba kuvvet) yaklaşımı kullanmak pratik limitlerin oldukça uzağındadır. Bu çalışmada, optimum çözümlere yakın çözümler bulabilen hiyerarşik bir yaklaşım geliştirilmektedir. Önerdiğimiz yaklaşım, sistemden istenen doğruluk veya kalite seviyesine göre, her bir devre blokunun sağlaması gereken doğruluk performansını belirlemektedir ve sonuç olarak sistemin güç tüketimi minimize edilmektedir.

Bu tezde hesaplama devreleri toplama ve çarpma devreleri olarak iki ayrı kolda incelenip, ilk adımda farklı güç, alan ve hata profillerine sahip temel toplama ve çarpma devreleri lojik olarak sentezlenmektedir. Bu aşamada temel toplama devresinden kasıt, 1 bitlik tam toplayıcı devresidir; temel çarpıcı devresi ise çarpıcı mimarisine göre değişiklik gösterir. Aritmetik işlem devresinden beklenen hata profilini sağlayacak N bitlik toplayıcıya/çarpıcıya ise farklı temel aritmetik işlem blokları birleştirilerek ulaşılmaktadır. Birleştirme aşamasında, yeni bir algoritma önererek en düşük güç tüketimi ile istenen hatanın altında kalmayı başaran aritmetik işlem devreleri sentezlenmektedir.

Bu tezde, bir öğrenme ağı, yaklaşık aritmetik işlem devrelerinin hatalarını tolere edebilecek şekilde kurulması hedeflenmektedir. Farklı ağ mimarilerinin yaklaşık hesaplamaya duyarlılığı analiz edilerek, yaklaşık hesaplamaya uygun, değişen paradigmaları takip edebilen, kısmen veri gürültüsüne karşı dayanıklı bir öğrenme tekniği seçilecektir.

Sistemin başarımı öğrenme ağı ve algoritmasının parametrelerine (katman sayısı, öğrenme adımı vs.) hassasiyetle bağlıdır. Bu öğrenme parametrelerinin, hata profilleri belli düşük güç tüketimli aritmetik işlem devreleri ile birlikte optimize edilmesi hedeflenmektedir.

Alan ve güç verimliliğini dikkate alarak farklı toplayıcı ve çarpıcı mimarileri arasında, Ripple Carry toplayıcı ve Wallace-Tree çarpıcı, devre sentezlerinde kullanılmaktadır.

Yaklaşık Rıpple Carry toplayıcı ile ilgili çalışmaların incelenmesinde, geleneksel hatasız tasarım metodolojisine bir eğilim görüyoruz. Bu tasarımlarda n-bitlik toplayıcının toplam performansı belirlemek için 1- bitlik toplayıcının ölçümleri toplanıyor. Her ne kadar bu yöntem, güç, alan ve gecikme metriklerine geçirilse, toplam n-bitlik Ripple Carry toplayıcının ortalama veya en kötü hata durumu, toplam hata toplamdan oldukça farklı olabilir.

Bununla motive olmuş, ilk önce 1-bit tam toplayıcı "Sum" ve "Carry", bitleri birbirinin hatasın azaltarak tasarlanmış, üstelik öyle toplayıcılar tasarlanıyor ki, iki ardışık yaklaşık toplayıcı, biriktirme hataları üretemiyorlar. Örneğin, eğer bir 1-bit toplayıcı beklenen lojik 0 çıktısına yanlışlıkla 1 ürettiği durumunda, bir sonraki toplayıcının çıkışının hatasız veya hatayı düşürerek sonuç verdiğini garanti ediyoruz, yani ikinci toplayıcı beklendiği 1 sayısı yerine ya 0 yâda hatasız 1 çıkışı üretiyor.

Sonuç olarak, önerilen toplayıcılar diğer literatürdeki çalışmalara göre ayni hata kısıttı sağlayarak daha küçük devre alanı ve daha az güç tüketimi sunar. Bir Rıpple Carry toplayıcıyı uygulamak için başka bir yaklaşım, yaklaşık lojik sentezi araçlarını kullanmaktır. Bu araçlar, alanı belirli bir hata kısıtlamasıyla optimize etmek için kullanılan genel amaçlı araçlardır. Neredeyse en uygun çözümleri bulmak, geleneksel yaklaşık olmayan sentez araçlarına kıyasla çok daha fazla zamana ihtiyaç duyduğundan ve / veya geniş alan elde ettikleri için toplayıcı ve çarpıcı için uygun bir yöntem değildir. Örneğin, bu yöntemler ile alan tasarruflu bir 32-bit toplayıcısını uygularken, basit kesme yöntemi aynı hata değeri için daha çok alan tasarrufu sağlarlar.

Genel olarak toplayıcı ve çarpıcının hatasını hesaplamak için bütün giriş ihtimalleri denemek zorundayız. Bit uzunluğunu artırarak hesaplama süresinin üstel olarak artırmasını göz önünde bulundurmalıyız. Bu tez çalışmasında hata hesabı yapmak için, bir matematik denklemi geliştirilmektedir. Önerilen yöntem bit uzunluğu ile doğrusal olarak artıyor ve hata hesap yapmak suresin büyük bir ölçüde azaltılıyor. Öte yandan,

bu denklemi kullanarak değişik hatalar için yaklaşık toplayıcı üreten bir sentez metodu önerilmektedir. Sistematik sentez tekniğimiz hata hesaplamaları açısından oldukça hızlı ve aynı zamanda doğrudur. Ayrıca alan değerleri, lojik sentezi araçlarında elde edilenlerden çok daha küçüktür.

Önerilen tezde, yaklaşık toplayıcı ile birlikte, üç aşamadan oluşan Wallace-Tree çarpanlarını da inceliyoruz. Çarpıcılar için hem kısmi birikiminde hem de nihai sonuç toplanmasında yaklaşık tam ve yarı-toplayıcılar öneriyoruz.

Tasarım stratejimiz, 1-bit toplayıcıların girdi atamalarının ortaya çıkma ihtimallerine dayanmaktadır yanı daha düşük olasılıkları olan giriş atamaları için daha yüksek hata oranları belirleriz. Örnek olarak, iki girişi olan bir devreyi düşünün ve iki farklı senaryoyu düşünün. İlk önce, her iki giriş de 1 ve 0 değerini, 1/2 eşit olasılıkla alır. İkinci senaryoda, girişler 1/4 ve 3/4 olasılıklarla sırasıyla 1 ve 0 değerini alır. Bu iki senaryoda, belirli bir hata sınırlaması için alan optimizasyon tekniklerinin farklı olması gerektiğini yorumluyoruz. Her girdi atamasına karşılık gelen bir hata, ilk senaryo için toplam hataya eşit şekilde katkıda bulunurken, ikinci senaryo için farklıdır. Bu nedenle, örneğimizde 1/4 olasılıklı girdi atamasına karşılık 3/4 olasılık için olanlardan daha hatalı çıktılara sahip oluyor. Bu da, girdilerin olasılığına dayanarak, Wallace-Tree çarpanının yapı taşları olarak tam ve yarım toplayıcı sentezlememize neden olur.

Bu çalışmada önerdiğimiz sentez tekniğini, aynı hata kısıtlamasını sağlayarak, literatürdekilere kıyasla en küçük alanı ve buna bağlı olarak güç tüketimini sunmaktadır. Ayrıca, sistematik sentez tekniğimiz hata hesaplamaları açısından oldukça hızlı ve hata hesaplaması kesin doğrudur.

Bu tezde, her tekniğin artılarını ve eksilerini elde etmek için farklı sentez teknikleri altında yapay sınır ağları gerçekleştirilmektedir. Paralel bir mimaride geniş alan gereksinimi nedeniyle, YSA'lar bu çalışmada, tekrarlanan çoğaltma biriktirme (ÇB) blokları ile gerçekleştirilmektedir. Uygulama olarak MNIST ve pendigit veri tabanları deneyimlenmektedir. Verimliliği incelemek için Önerilen yöntemle YSA'nın çeşitli mimarileri ve yapıları gerçekleştirilmiştir. Deneysel sonuçlar, önerilen yaklaşık çarpıcılar kullanılarak tasarlanan YSA'ların diğer yaklaşık çarpıcılara göre daha küçük bir alana sahip ve daha az enerji tükettiğini göstermektedir.

Hem yaklaşık toplayıcılar ve hem de yaklaşık çarpıcılar kullanarak doğru çalışan devreye göre, alanda ve enerji tüketiminde sırasıyla50% ve 60% 'a varan azalma sağladığı gösterilmektedir.

Bu çalışmanın sonunda YSA'dan esinlenerek, Konvolüsyon işlemi gerçekleştirilmektedir. Önerilen yöntemde, clocklama yöntemini değiştirerek sonuçlar daha kısa zamanda elde edinmektedir. Önerilen yöntemin etkinliğini değerlendirmek için, filtreler  $3 \times 3$ ,  $5 \times 5$  ve  $7 \times 7$  boyutlarla denenmektedirler. Filtrelerin girişleri  $28 \times 28$ piksel olarak MNIST datasetinden alınmaktadır. Deneysel sonuçlara göre, önerilen metodu kullanarak bekleme suresinde 50% azalma ve güç tüketiminde 97% tasarruf görünmektedir.

## **1. INTRODUCTION**

In recent years, artificial neural networks (ANNs) have achieved significant fame in different research areas, including medical image processing [8], face detection [9], and semantic segmentation [10]. Complementary, progression in graphics processing units (GPUs) and central processing units (CPUs), cause calculate on the immense hardware resources like clouds or supercomputers to become prevalent. However, for portable devices, due to their limited memory, the number of processing units, and the battery capacity, the realization of ANNs in these devices is impractical. Here, the main concern for this work arises.

An investigation of ANNs complexity reduction within the literature shows that studies are categorized in software level and hardware level commonly. Some valuable studies provide a survey of topic progressing [11, 12]. At the software level, apart from hardware consideration, the determination of ANNs structure during the training process is intended to obtain a network with minimum parameters. On the other hand, at the hardware level, distinct from the software side, different techniques are employed for reducing the hardware cost of bulky ANNs. Consequently, training based on devoted hardware, and applicable hardware modeling through the software, provide helpful results to diminish ANNs complexity.

At the software level, [13] provides a theoretical analysis of quantization error. In this study, by focusing on the derivation of finite precession error analysis techniques, the minimum bit number for forward retrieving and back-propagation is calculated. Binary weight network and XNOR networks are proposed in [14]. These two approximations are exploited to realize the standard convolution neural networks. Logarithmic computation concept is presented in [15, 16]. This encoding method enables ANNs to eliminate bulky digital multipliers. Determining logarithmic values for weights during the training process, aides to replacing of digital multipliers by shift operations with acknowledging that the multiplicands are constant in power-two numbers. By considering that ANNs consist of multiplication of different matrices, optimizing

the loops is another approach to accelerating network [17], where optimum sharing of these partial terms in the multiple constant multiplications, reduces hardware complexity [18, 19]. Beyond synthesis methods, other approaches like stochastic and approximate neural networks are common in literature. Applying stochastic computational units in neural networks results in error maintains within 10 percent of floating-point implementation [20]. The accuracy of stochastic computation may not be comparable with the conventional method but, low circuit area and power consumption make this method favorable for hardware implementation.

At the hardware level, different field-programmable gate array (FPGA) and application-specific integrated circuit (ASIC) circuits are investigated for accelerating network. To overcome the problem of memory access in large ANNs, a custom multi-chip machine-learning architecture is introduced in [21]. A specialized chip consists of a microcontroller, accelerator, and on-chip SRAM is introduced for always-on subsystems of mobile/Internet of Things (IoT) devices in [22]. Also, apart from customized chips, different hardware architectures by focusing on arithmetic operations are exploited to hinder the bulky area problem of ANNs. ANNs realization under multiplier accumulated units (MAC) is an approach to reduce hardware occupied area and power consumption by considering an increase in delay.

According to MAC-based implementation, ANN hardware structure can classify into two models: axonal-based [23] and dendritic-based [24] models. For axonalbased model, every single input of layers is multiplied by related weights of all neurons of the layer, and all outputs calculate simultaneously, as a result, for axonal-based model obtaining all inputs at the same time is unnecessary. However, for accumulating different multiplication results, extra memory is essential. On the other hand, in dendritic-based model, the value of the next neuron is calculated by multiplying all inputs with related neuron weights and accumulating them. This method results in the sequential generation of outputs, and every step of calculation needs to obtain all inputs to start. In [25], by combining these two architecture, parallel computing is enabled in two successive layers to achieve smaller latency in the computing time of the whole network.

Since the multiplier is a core block of MAC, they dominate calculation time, so designing the multipliers has become an important consideration. Conventional

multipliers consist of an array of Full Adders (FA) to adding partial products and final adders. Exploiting Wallace tree structure with different compressor leads to delay reduction in multipliers.

Based on the error-tolerant inherency of neural networks, approximate neural networks or ANNs with approximate blocks are a favorable approach to realize ANNs, where the trade-off between hardware complexity and accuracy is explored through the approximate level. Approximation for both computation and memory access is investigated in [26], also, the impact of neurons on the output quality is determined to approximate the computation and memory accesses of certain less critical neurons to obtain the maximum efficiency under a given quality constraint. The exact adders and multipliers in the MAC blocks are replaced by the approximate ones in [27]. The exploitation of approximate units yields respectively up to 64% and 43% reduction in energy and area of the ANN design for PENDIGIT data set with a slight decrease in the hardware accuracy. An evaluation of a large pool of approximate multipliers consist of 100 deliberately design, and 500 cartesian genetic programmings (CGP) based multipliers in ANNs, is accomplished in [28]. Also, to determine the critical features of multipliers in ANNs, different error parameters efficacy is investigated. According to this study, the CGP based multipliers introduced in [29] are better suited for use in the investigated ANN.

Beyond the hardware architecture, there are different methods which are related to ANNs based on the application, such as convolutional neural networks (CNNs), recurrent neural networks (RNNs) and multilayer perceptrons (MLPs) based networks. Since our utmost concern is energy efficiency, we focus on MLPs which provide better energy scaling for applications implemented by energy-stringent stand alone devices such as always-on sensors and ASIC chips that detect anomaly [22, 30].

Each layer that comprises MLP has computation workload, which is composed of relatively basic operations, i.e., multiplication, addition, and activation. As the network is layered, arithmetic operations run in a pipeline (feed-forward) by axonal based model, where inputs of one layer wait for the outputs of the previous layer. In this thesis, ANNs are implemented using MAC blocks in two separate architectures to investigate the area and latency trade-off. A single MAC is used to realize each neuron

computation in each layer in the first one, called (*SMAC\_NEURON*), and a single MAC is used to implement the entire ANN in the second one, called (*SMAC\_ANN*).

Furthermore, we present an effective hardware implementation of ANNs using approximate adders and multipliers in time-multiplexed architectures, taking into account the ANN hardware accuracy. The exact adders and multipliers in the MAC blocks and parallel units are replaced with approximate adders and multipliers to form approximate ANNs. Furthermore, we present an algorithm for determining the approximate level of multipliers and adders, using the approximation level of blocks to investigate the trade-off between hardware complexity and accuracy. In contrast to the methods of [31] [29], the generation of an approximate multiplier and adder with different bit-widths of inputs under the specified approximation level in this thesis can be done in linear time. As shown in [26], by using approximate multipliers of different approximation levels for the neuron computations at different layers, the ANN hardware complexity can be greatly reduced. Our experiments show that ANNs with the proposed approximate multiplier occupy less area and consume less energy than the exact versions with only a slight loss in accuracy. It is also demonstrated that, by using the proposed approximate adders, the ANN hardware complexity can be further reduced.

The rest of this thesis is organized as follows. The approximate computing and the proposed blocks are discussed in Chapter 2. ANNs architecture is investigated in Chapter3. The exploiting of the proposed approximate blocks in the ANNs, and the algorithm to replace the approximate blocks with their exact versions are given in Chapter4. Also, a new implementation method of convolutional layers are described in Chapter5. finally, Chapter 6 concludes the thesis.

#### 2. APPROXIMATE COMPUTING

### 2.1 Background and Preliminary Works

As Moore's Law starts to lose its validity, not only the number of transistors on a chip but more severely the chip's power dissipation have reached a critical point at which new circuit design techniques enabling low-power and low-area designs are highly desired [32]. Approximate computing is a class of methods that relaxes the necessity of exact equivalence between a computing system's specification and implementation. This relaxation provides an opportunity to save in design area, delay, or power dissipation at cost of inaccuracy for the calculations. allows you to trade numerical performance precision for design area, delay, or power dissipation savings. Approximate computing is used to increase area, power, and energy efficiency in applications that do not need high precision, such as image processing and learning.

Since these applications are dominated by arithmetic blocks, designing approximate adders and multipliers are extensively investigated in the literature, especially in the last decade [1, 2, 4, 5, 29, 33–37]. The implementation of approximate arithmetic blocks in logic and circuit level is also the subject of this research. Ripple-carry adders and Wallace-tree multipliers are chosen for synthesis based on their area and power efficiency among different adder and multiplier architectures, with the object of minimizing circuit area while satisfying a given error restriction.

We see a common tendency in related studies on approximate ripple-carry adders to assume that the more erroneous outputs (*Sum* and *Carry*) mean less accurate designs [1-3]. It must be considered, Offsetting errors, or errors in separate outputs that entirely or partly cancel each other, are not taken into account in this assumption. Motivated by this, we start by designing 1-bit full adders with offsetting errors in *Sum* and *Carry*. We illustrate how applying an error to output will improve accuracy and reduce the area of inexact adders. Similarly, we construct the ripple-carry adder at a higher level such that two consecutive estimated 1-bit full adders cannot generate

build-up errors, i.e., errors in separate outputs are canceling each other. For example, if a 1-bit adder generates an erroneous logic 1 output, which is supposed to be logic 0, we can guarantee that the output of the neighbor adder will be error-free or will generate an error with a logic 0 output, which is expected to be logic 1.

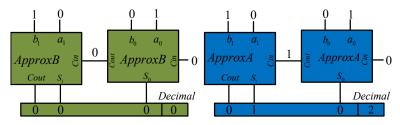

Consider the example of adding two 2-bit  $(01)_2$  and  $(10)_2$  binary numbers in Figure 2.1 to illustrate superposition, offsetting, and build-up terminology. In this example, two different approximate adders (approxA, approxB) are exploited to execute addition operation, the truth-table of these adders for evaluated binary numbers also is given in TBL.2.1. Consider that, however Sum and Cout results are inexact for the first approximate adder, still error distance is 1 for given inputs, where superposition between Sum and Carry cause to error distance be 1 for given inputs  $(011)_2$  yet Sum and Carry both are inexact. The reason is incremation in Sum reliefs by decreasing in Cout, this superposition assists to minimizing Sum and Cout simultaneously. Furthermore according to approxA truth table, two consecutive approxA will not accumulate each other errors, as shown in Figure 2.1 approxA first bit result for  $(010)_2$ inputs is  $(10)_2$  (decimal 2), while exact result is  $(01)_2$  (decimal 1), i.e. lesser than approximate result, correspondingly second adder inexact result for  $(101)_2$  inputs is  $(01)_2$  (decimal 1) lesser than exact result  $(10)_2$  (decimal 2). As a result increment in first adder compensate with decrements by second adder. In essence it is not possible two successive approxA accumulate each other error (build up error). Contrarily for 2-bit approxB adders, inexact results is lesser than exact result, therefore two consecutive approxB adder make build-up error. approxA case shows, superposition can violate for adders with different error profile.

Approximate ripple-carry adders are built in two ways in the literature: 1)implement 1-bit full adders in transistor level and then creating a ripple-carry adder; 2) using synthesis tools to specifically implement a ripple-carry adder in logic level. For the first approach, approximate 1-bit adders are usually derived from standard mirror adders and XOR/XNOR based adders by eliminating transistors and/or replacing certain portions of the adders with smaller circuitries [1–3, 33]. Error dependencies in terms of offsetting and build-up errors are not taken into account in these experiments. It must be mention that, first implementation method is non-systematic, relying heavily on the designer's intuition and experiences. In the second approach, the introduced

Figure 2.1 : Ripple carry adder structure.

| Inputs | ApproxA     | ApproxB                   |

|--------|-------------|---------------------------|

|        | Court Court | $\mathbf{O}$ $\mathbf{O}$ |

**Table 2.1 :** Truth table of sample approximate adders.

|   | Inputs |   |     | Appı | oxA ApproxB |      |     |

|---|--------|---|-----|------|-------------|------|-----|

|   | А      | В | Cin | Cout | Sum         | Cout | Sum |

|   | 0      | 1 | 0   | 0    | 1           | 0    | 0   |

|   | 1      | 0 | 1   | 0    | 1           | 0    | 1   |

| - | 1      | 0 | 0   | 1    | 0           | 0    | 0   |

tools are general-purpose tools, not strictly for ripple-carry adders [31, 38–43]. Furthermore, since determining near-optimal solutions takes far longer than traditional non-approximate synthesis methods, these tools generally suffer from long runtimes. For example, the method in [41] realizes a 32-bit ripple-carry adder with a 10% area savings, while truncation and the proposed methods in this thesis yield 25% and 32% area savings for the same worst-case error value, respectively. The run-time effects would be much worse if an average error value was used.

Motivated by the restrictions of transistor and logic level approximation methods, we suggest a systematic synthesis methodology based on a novel error measurement process. Our synthesis method is ideal for adders because it is fast, precise, and scalable. Furthermore, taking into account n-bit synthesis and the relationship between approximate adders, we can achieve a series of adders with no build-up errors. This function also helps in the formation of an n-bit adder with a different error profile in order to achieve the minimum cost for the desired error metric.

Our proposed systematic synthesis technique is both fast and reliable in terms of error calculation. For example, the synthesis of a 64-bit ripple carry adder takes less than a second. Also, the design area produced by the proposed logic synthesis tools is less when compared to the other methods. For example, given a 0.5% average error for a 32-bit adder, we achieve a 50% smaller area than [40], which can be considered the best area-efficient method in the literature.

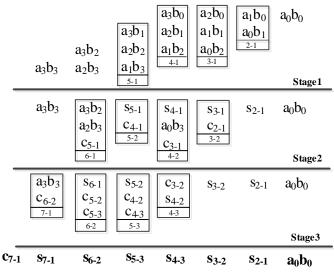

Along with ripple-carry adders, we investigate Wallace-tree multipliers, which have three stages: partial product generation, partial product aggregation, and final result addition.

To implement the approximate multiplier, we initially investigated the different approximate multipliers in the literature to obtain the efficiency of different approaches. The approximate  $2 \times 2$  multiplier is implemented in [44] to produce partial products and exact adders for the accumulation tree. A new approximate adder is recommended for product aggregation in [37], where exact adders are used to restore errors in the final results. Compressors are employed to speed up product accumulation and lessen the tree size in [37, 45]. Two approximate 4-2 compressors with four different approximate multiplier are proposed in [4]. Also, a new multiplier by error recovery is obtained by updating this compressor in [5]. Additionally, truncation and rounding techniques are used in the least significant columns of partial products in certain studies [46, 47]. Also, bit-wise multipliers are proposed in [48, 49], where detecting the leading one block saves area and power for desired error values. In [50], a reconfiguration-oriented adder is suggested. Despite the fact that reconfigurable circuits can be adjusted for various error values, they require additional control blocks, which increases their size and power consumption. These experiments are not included in this work, since we concentrate on reaching minimal area and power rather than reconfigurability.

Unlike the previous studies, we consider using an approximate full-adder and half-adder for both partial product accumulation and final result summation. The probability of input assignments is the basis for our architecture strategy, where for input assignments with lower probabilities we allocate higher error rates. As an example, consider a circuit with two inputs in two separate schemes. Inputs take the value of logic 1 and 0 with equivalent probabilities of 1/2 for the first one. In the second case, all inputs have odds of 1/4 and 3/4 for logic 1 and 0, respectively. We suggest that hardware cost optimization strategies for a given error constraint should be dissimilar for these two scenarios. Although each error associated with each input assignment contributes to the cumulative error in the first example, this is not the case for the second one. As a result, we have more erroneous outputs in our example corresponding to input assignments with 1/4 probabilities compared to the input assignments with 3/4

probabilities. This leads us to implement full and half adders based on the likelihood of inputs as the building blocks of the Wallace-tree multiplier. According to our experiments, introduced synthesis technique, as compared to those in the literature, provides the smallest area while meeting the same error restriction. Furthermore, our systematic synthesis method is both fast and reliable in terms of error calculation.

#### 2.2 Ripple-Carry Adder Design

There are two stages to our synthesis strategies, which are described in the following two subsections. We begin by building a library of approximate 1-bit full adders with various error rates. In the second stage, we use the obtained library to systematically synthesize an n-bit ripple-carry adder from the least to the most significant bits; the adder satisfies the specified error restriction while taking up the least amount of area.

#### 2.2.1 1-bit full adder design

The binary inputs to a 1-bit full adder are A, B, and C(Carry or Cin), as well as *Cout* and *Sum* comprises the output.

The estimated and actual decimal values of the output are denoted by  $\hat{y}$  and y, respectively. It's worth noting that they're in the decimal range [0-3]. We use total absolute error distance (TAED) as an error metric:

TAED =

$$\sum_{i=0}^{7} |y_i - \hat{y}_i|$$

(2.1)

where *i* denotes the truth table's *i*th input assignment. For example, if both *Cout* and *Sum* are zero for all input assignments, this is truncation with zero circuit area cost, and TAED = 12. However, we will show that TAED = 4 can achieve zero cost. TAED = 1, TAED = 2, and TAED = 3 are also used to build adders in this thesis.

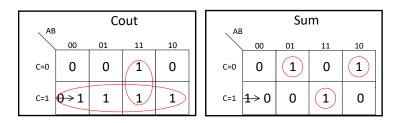

The offsetting errors in *Sum* and *Cout* play key role in our designs, and are exploited in our synthesis technique. Let's take a look at two examples to help clarify the offset concept, consider three separate approximate adders, each of which has an incorrect output for a specific input assignment. The first adder has a  $0 \rightarrow 1$  error in *Sum*, so TAED = 1; the second adder has a  $1 \rightarrow 0$  error in *Cout*, so TAED = 2; and the third adder, which is the proposed one, has both of the errors, so TAED = 1, because simultaneous  $0 \rightarrow 1$  and  $1 \rightarrow 0$  errors in *Sum* and *Cout* for the same input assignment results in a change of 1 in TAED. Simultaneous error in *Sum* and *Cout* means permission has been issued to alleviate the hardware cost of both *Sum* and *Cout*. Consequently, the third approximate adder has a much smaller area than the other two.

Note that, error in *Cout* and *Sum* yields 2 and 1 change in TAED, respectively. On the other hand, simultaneous  $0 \rightarrow 1$  and  $1 \rightarrow 0$  errors occurring in *Sum* and *Cout* for the same input assignments results in a change of 1 in TAED; we name this error as the offsetting error. As a second example, consider the summing operation of  $3_{(10)}$  and  $10_{(10)}$  by an exact adder (EXAD) is as follows.

Assume the *Sum* and *Cout* results are complemented for the adder allocated to the least significant bit. The first bit is computed using the approximate adder *ApproxA*, while the remaining bits are computed using exact adders (EXADs). As a result TAED changes by one, and the error distance is one. The following diagram depicts this.

# $0 \rightarrow 1$ <br/>EXAD $\curvearrowleft \text{APAD}$

| + | 0<br>1 | 0<br>0 | 1<br>1 | 1<br>0 |    |

|---|--------|--------|--------|--------|----|

|   | 1      | 1      | 1      | 0      | -1 |

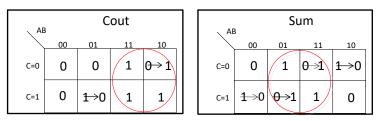

The suggested design approach's key concept is to apply offsetting errors  $0 \rightarrow 1$  and  $1 \rightarrow 0$  to the same input assignments which their results in output bits are non-identical. According to the truth-table of one-bit exact adder in Table 2.2, 6 of 8 inputs combination have different *Sum* and *Cout* values that we will use in our approximation technique. By considering these assignments and choosing the solutions providing the lowest literal costs in sum-of-products (SOP) expressions, we present four separate approximate adders APAD1, APAD2, APAD3, and APPAD4 with TAED values of 1, 2, 3, and 4, respectively. Table 2.2 contains the proposed approximate adders in the form of truth tables. We'll go into each adder form in detail in the sections below.

**Logic synthesis of APAD1, TAED** = 1: Offsetting errors in both *Sum* and *Cout* for one input assignment. There are  $\binom{6}{1}$  candidates for synthesis, and 2 of them have the minimum literal cost.

Figure 2.2a shows one of them and the outputs' literal expression is as follow.

Cout = B + ACin $Sum = ABCin + A\overline{B} \overline{Cin} + \overline{A}B\overline{Cin}$

With this solution, one of the prime implicants of *Sum* is eliminated. Moreover a prime implicant group of *Cout* is expanded. It must be mention changing in 000 and 111 results, yields minimum saving of the literals.

**Logic synthesis of APAD2, TAED** = 2: Offsetting errors in both *Sum* and *Cout* for two input assignments. There are  $\binom{6}{2}$  candidates for synthesis, and 3 of them have the minimum literal cost.

Figure 2.2b shows one of them with following expressions.

Cout = A $Sum = \overline{A}B + \overline{A}Cin + BCin$

**Logic synthesis of APAD3, TAED** = **3:** Since we reached a literal cost of 1 for *Cout* in APAD2, no further 0-1 transitions are preferred for *Cout*. However, for *Sum* we use one more error. As a result, offsetting errors in both *Sum* and *Cout* for two input assignments, and an error in *Sum* for one input assignment return TAED = 3. There are  $\binom{6}{2}\binom{4}{1}$  candidates for synthesis, and 9 of them have the minimum literal cost.

Figure 2.2c shows one of them with following expressions.

Cout = A $Sum = \overline{A}Cin + B$

**Logic synthesis of APAD4, TAED** = 4: Similar to APAD3 synthesis, we use offsetting errors in both *Sum* and *Cout* for two input assignment. Additionally, we apply errors in *Sum* for two input assignments, so TAED = 4. There are  $\binom{6}{2}\binom{4}{2}$  candidates for synthesis, and 9 of them have the minimum literal cost.

Figure 2.2d shows one of them with following expressions for outputs.

# Cout = A

Sum = B

Figure 2.2a : APAD1.

| 、 AB |    | Со              | out |     |

|------|----|-----------------|-----|-----|

|      | 00 | 01              | 11  | 10  |

| C=0  | 0  | 0               | 1   | 0→1 |

| C=1  | 0  | <del>1</del> →0 | 1   | 1   |

|     |    | Su  | m  |     |

|-----|----|-----|----|-----|

| AB  | 00 | 01  | 11 | 10  |

| C=0 | 0  |     | 0  | 1→0 |

| C=1 | 1  | 0 1 | 1  | 0   |

Figure 2.2b : APAD2.

| ∖ AE | 3  | С   | out |     | 1 |

|------|----|-----|-----|-----|---|

|      | 00 | 01  | 11  | 10  |   |

| C=0  | 0  | 0   | 1   | 0→1 |   |

| C=1  | 0  | 1→0 | 1   | 1   |   |

| AE  | Sum AB |     |     |     |  |  |

|-----|--------|-----|-----|-----|--|--|

|     | 00     | 01  | 11  | 10  |  |  |

| C=0 | 0      | 1   | 0→1 | 1→0 |  |  |

| C=1 | 1      | θ→1 | 1   | 0   |  |  |

Figure 2.2c : APAD3.

Figure 2.2d : APAD4.

Figure 2.2 : Karnough Maps of APADs.

|                                                                     |            |                     | nal                                                                                                                  |           |                       |              |                          |                          |         |                                                      |                |  |

|---------------------------------------------------------------------|------------|---------------------|----------------------------------------------------------------------------------------------------------------------|-----------|-----------------------|--------------|--------------------------|--------------------------|---------|------------------------------------------------------|----------------|--|

|                                                                     |            |                     | Decin                                                                                                                | 0         | 0                     |              |                          | 0                        | 0       | ŝ                                                    | e              |  |

|                                                                     |            | APAD4               | Error                                                                                                                | 0         | -                     | 0            | -                        | <del>-</del>             | 0       |                                                      | 0              |  |

|                                                                     |            | AF                  | Sum J                                                                                                                | 2         | <b>X</b> 0 <b>/</b> 0 | 0 1 0        | 0 <b>X</b> 1 <b>X</b> -1 | 1 <b>X</b> 0 <b>X</b> +1 | 1/ 0/ 0 | 1 / 1 × +1                                           | 7              |  |

|                                                                     |            |                     | Cout                                                                                                                 | 0 /0 /0   | 2                     | 2            | ×o                       | 1X                       | 1       | 1                                                    | 1/ 1/ 0        |  |

|                                                                     |            |                     | ecimal                                                                                                               | 0         |                       |              |                          | 7                        | 0       | ю                                                    | $\mathfrak{c}$ |  |

| nucto.                                                              |            | APAD3               | Error D                                                                                                              | 0         | 0                     | 0            | -                        | +                        | 0       |                                                      | 0              |  |

| - חזר מו                                                            |            | AP                  | Sum E                                                                                                                | 2         | 1                     | 7            |                          | <b>X</b> 0               | 20      | 1 <b>X</b>                                           | 1              |  |

| I AIA                                                               |            |                     | Cout S                                                                                                               | 0 00 00 0 | 0 1/ 0                | 0 1/ 0       | 0X 1X                    | 1 X 0X +1                | 1/ 0/ 0 | 1/ 1X +1                                             | 3 1/ 1/ 0      |  |

|                                                                     | e          |                     | imal                                                                                                                 | 0         |                       | 1            | _                        | 2                        | 2       | 5                                                    | 3              |  |

| u app                                                               | Adder Type | 5                   | r Dec                                                                                                                |           |                       |              |                          |                          |         |                                                      |                |  |

| art an                                                              | Adde       | APAD2               | LErro                                                                                                                | 0         | 0                     | 0            | -                        | Ŧ                        | 0       | 0                                                    | 0              |  |

|                                                                     | P          | A                   | Sum                                                                                                                  | 0 0 0     | 0/ 1/ 0               | 0/ 1/ 0      | 0X 1X -1                 | 1 <b>X</b> 0 <b>X</b> +1 | 1/ 0/ 0 | 1/ 0/ 0                                              | 1              |  |

| autus                                                               |            |                     | l Cout                                                                                                               |           | 2                     | 2            | <b>X</b> 0               | 1X                       | 7       | 1                                                    | 1/ 1/ 0        |  |

| TADIC 2.2 . ITULII LADICO DI CAACI AILA APPIDALITIALO I-DIL AUUCIO. |            |                     | A B Cin Cout Sum Decimal Cout Sum Error Decimal Cout Sum Error Decimal Cout Sum Error Decimal Cout Sum Error Decimal | 0         |                       | 0            | 7                        |                          | 0       | 0                                                    | ю              |  |

| •                                                                   |            | APAD1               | Error I                                                                                                              | 0         | 0                     |              | 0                        | 0                        | 0       | 0                                                    | 0              |  |

| Tault                                                               |            | AI                  | Sum ]                                                                                                                | 2         | 1                     | ×            | 2                        | 1                        | 2       | 2                                                    | 1              |  |

|                                                                     |            |                     | l Cout                                                                                                               | 2         | 2                     | 1 <b>×</b> 1 | 1                        | <b>&gt;</b> 0            | 1       | 1                                                    | 1              |  |

|                                                                     |            |                     | ecima                                                                                                                | 0         | -                     |              | 0                        | -                        | 0       | 0                                                    | ε              |  |

|                                                                     |            | FA                  | Sum D                                                                                                                | 0         | -                     |              | 0                        | -                        | 0       | 0                                                    |                |  |

|                                                                     |            |                     | Cout                                                                                                                 | 0         | 0                     | 0            | -                        | 0                        | -       |                                                      | -              |  |

|                                                                     |            | Inputs <sup>-</sup> | Cin                                                                                                                  | 0 0 0 0   | -                     | 0            | -                        | 0 0 1                    | -       | 0                                                    |                |  |

|                                                                     |            | Inp                 | АB                                                                                                                   | 0 0       | $0 \ 0 \ 1$           | 0 1          | $0 \ 1 \ 1$              | 1 0                      | $1 \ 0$ | $\left  \begin{array}{c} 1 \\ 1 \end{array} \right $ | 1              |  |

Table 2.2 : Truth tables of exact and approximate 1-bit adders.

### 2.2.2 n-bit ripple-carry adder design

We composed the ripple-carry adder such that no build-up errors can occur when two approximate 1-bit full adders are used in a sequence. For example, if a 1-bit adder generates an erroneous logic 1 output, which should be logic 0, we should guarantee that the output of the neighbor adder will be error-free or will generate an offsetting error with a logic 0 output, which should be logic 1. The following lemma specifies the conditions that must be met in order to avoid build-up errors.

**Lemma 1.** Consider a ripple-carry adder with various 1-bit approximate adders. If and only if all of the following conditions are fulfilled, build-up errors in successive adders will be eliminated:

- *1.* For all input assignments causing error, Cout = Cin;

- 2. For all input assignments causing a positive error that increases the expected output, all corresponding Couts should be the same ; and

- 3. For all input assignments causing a negative error, decreasing the expected output, all corresponding Couts should be the same.

*Proof.* The proof comes in the form of a contradiction. If a 1-bit adder has an assignment that causes an error with Cout = Cin, so repeatedly using this adder will result in build-up errors. A build-up error occurs when the second or third condition is violated even the first is met. Finally, meeting these three criteria is enough to avoid build-up errors.

To illustrate this lemma, consider a 2-bit adder in which the least significant bit adder is APAD4 and the second adder may be any of the proposed APADs. Let's look at all of the potential inputs and their inexact outcomes. Start with 001 as an APAD4 input, which yields 0s for both *Cout* and *Sum*. According to Table 2.2, this outcome is less than the actual result, so we call it a negative error. We examine inputs with Cin = 0 for the second adder since *Cout* of APAD4 is *Cin* of the second adder.

According to Table 2.2 when *Cin* is 0, the generated results are exact results or positive errors. i.e if APAD4 generates negative error, it is impossible to have a positive error

for the second adder. Next, consider the other input 011 causing negative error; same considerations are applicable for this case too. For positive error cases, inputs are 100 and 110; for both cases *Cout* value is 1. According to Table 2.2, if there is a positive error, *Cin* is always 0. Therefore two consecutive positive error is impossible too.

To satisfy Lemma 1, we shrink our 1-bit approximate adder library. Initially, it consists of 2 APAD1, 3 APAD2, 9 APAD3, and 9 APAD4, and it becomes 2 APAD1, 2 APAD2, 2 APAD3, and 2 APAD4, all satisfying Lemma 1 with Cin = 0 for positive errors, Cin = 1 for negative errors, and  $Cout = \overline{Cin}$ . Note that for each APAD type, we have two options with identical area and error performances. For simplicity we use the adders given in Table 2.2, where all of proposed adders, satisfying Lemma 1 for all experiments.

In our synthesis technique, starting from the least to the most significant bit, we benefit the ordering of APAD4-APAD3-APAD2-APAD1-EXAD, where this array is justified with the following lemma.

**Lemma 2.** Consider two successive 1-bit adders in a ripple-carry adder. To achieve minimum area with a given error constraint, the one closer to the least significant bit should have a larger or an equal TAED value compared to the one closer to the most significant bit.

*Proof.* By contradiction, assume that the statement is wrong. By interchanging the two adders, we achieve a smaller error with the same area. However, the minimum area should have a negative correlation with the given error constraint. There is a contradiction.  $\Box$

To understanding this lemma consider two scenarios for 2-bit adder. In the first scenario the least significant bit adder is APAD4 and the second bit adder is APAD1. In the second scenario the least significant bit adder is APAD1 and the second bit adder is APAD4. Both cases hold same area, but the first scenario results in smaller error.

In our synthesis technique, we use average absolute error distance (AAED) that is obtained with dividing TAED by the number of input assignments. For example AAED values of APAD4, APAD3, APAD2, and APAD1 are 4/8, 3/8, 2/8, and 1/8, respectively. We model AAED value and named it estimated average absolute error

distance (EAAED). For an n-bit ripple-carry adder:

EAAED =

$$\sum_{i=0}^{n-1} E_i 2^{i-1}$$

(2.2)

where  $E_i$  represents the error contribution of the *i*th 1-bit adder from the least significant bit.

$$E_{i} = \frac{2}{3} \sum_{a \in \{-1,0,1\}} \sum_{b \in \{-1,1\}} P(i-1:a,i:b) \mid 0.5a+b \mid$$

(2.3)

where *a* and *b* represent the error values of the (i - 1)th and *i*th 1-bit adders, respectively. Since, Equation 2.2.2 gives the error contribution of the *i*th adder, b = 0 case, no error in the *i*th adder, is excluded. In the equation, *P* represents a probability that the (i - 1)th and *i*th adders have errors of *a* and *b*, respectively. The constant factor 2/3 is the ratio of the error contribution of the *i*th adder (*X*) to the total error contribution of the *i*th and the (i - 1)th adders (0.5X + X). In a similar fashion, |0.5a + b| represents the total error distance caused by the the (i - 1)th and the *i*th adders. In calculating *P*'s we use conditional probability such that P(i - 1 : a, i : b) = P(i - 1 : a)P(i : b | i - 1 : a). The following example elucidates our calculation steps of  $E_i$  given in Equation 2.2.2.

## **Example 1.** Calculate $E_i$ if the (i-1)th and the *i*th adders are both APAD4.

Table 2.3 gives the calculations by using the truth table of APAD4, previously given in Table 2.2. There are six cases in Table 2.3 corresponding to six rows in the table for different assignments of *a* and *b*. For the first and the sixth cases *P*'s are zero, since two successive positive error or negative error is impossible. For the second case, P(i-1:-1) = 2/8 since APAD4 has 2 input assignments causing -1 error among 8 total assignments. Additionally, P(i:+1 | i-1:-1) = 2/4 since -1 error causes *Cout* = 0 for the (i-1)th adder, so the *i*th adder's C is logic 0 and it has 2 input assignments causing +1 error among 4 total assignments with C = 0. A similar justification can be done for the fifth case. For the third and the fourth cases, P(i-1:0) = 4/8 and since a = 0, P(i:b | i-1:0) = P(i:b) = 2/8.

| a  | b                   | $P = P(i-1:a) \times P(i:b \mid i-1:a)$               | 0.5a+b              | $\sum_{b \in \{-1,1\}}$ |

|----|---------------------|-------------------------------------------------------|---------------------|-------------------------|

| -1 | -1                  | 2/8 	imes 0                                           | 3/2                 | 0                       |

| -1 | +1                  | $2/8 \times 2/4$                                      | 1/2                 | 1/16                    |

| 0  | -1                  | $4/8 \times 2/8$                                      | 1                   | 2/16                    |

| 0  | +1                  | $4/8 \times 2/8$                                      | 1                   | 2/16                    |

| +1 | -1                  | $2/8 \times 2/4$                                      | 1/2                 | 1/16                    |

| +1 | +1                  | 2/8 	imes 0                                           | 3/2                 | 0                       |

|    | $\frac{2}{3}\Sigma$ | $a \in \{-1,0,1\} \sum_{b \in \{-1,1\}} P(i-1:a,i:b)$ | $0.5a + b \mid = 4$ | 4/16                    |

**Table 2.3 :** Calculation of  $E_i$  for example 1.

**Table 2.4 :** Values of  $E_i$ 's for different APAD combinations.

| i-1   | APAD1   | APAD2   | APAD3   | APAD4 |

|-------|---------|---------|---------|-------|

| APAD1 | 2.66/32 | ×       | ×       | ×     |

| APAD2 | 2.33/32 | 4.66/32 | ×       | ×     |

| APAD3 | 2.33/32 | 4.33/32 | 6.66/32 | ×     |

| APAD4 | 2/32    | 4/32    | 6/32    | 8/32  |

Table 2.4 gives  $E_i$  values for all different combinations of APAD's as the (i-1)th and the *i*th adders with satisfying Lemma 2. Since C = 0 for the ripple-carry first adder, we can obtain  $E_1$  as 2/4 for APAD4 and APAD3, and 1/4 for APAD2 and APAD1 by using the truth tables in Table 2.2.

**Example 2.** Calculate EAAED of an 8-bit ripple-carry adder having APAD4-APAD4-APAD4-APAD4-APAD2-APAD1-EXAD-EXAD 1-bit adders ordered from the least to the most significant bit.

With  $E_1 = 2/4$ , and using Table 2.4:  $EAAED = \frac{2}{4}2^0 + \frac{8}{32}(2^1 + 2^2 + 2^3) + \frac{4}{32}2^4 + \frac{2.33}{32}2^5 = 8.33.$

Constructed on Lemma 2 and the proposed error calculation method summarized in Table 2.4, our synthesis technique consists of the following 5 steps.

- 1. Start with an exact ripple-carry adder consisting of EXAD's.

- 2. From the least to the most significant bit, replace EXAD's with APAD4's until the calculated error value is larger than the given target error value.

- 3. Repeat the second step for APAD3, APAD2, and APAD1 instead of APAD4, respectively, replacing the unchanged EXAD's. Save the solution.

Figure 2.3 : Demonstration of steps for example 3.

- 4. Replace all APAD3's, APAD2's, and APAD1's with EXAD's in Step 3; replace the last APAD4 (most significant one) respectively with APAD3, APAD2, and APAD1; apply the second step with APAD3, APAD2 and APAD1 instead of APAD4. Save solutions.

- 5. Using area costs of APAD4, APAD3, APAD2, APAD1, and EXAD, select the best solution with minimum area cost.

Note that due to the essence of the proposed method, without using any error detection block that causes area overhead, build-up errors are fully eliminated. To elucidate our synthesis technique, we present an example.