# ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL OF SCIENCE ENGINEERING AND TECHNOLOGY

# HIGH PERFORMANCE TUNABLE ACTIVE INDUCTORS FOR MICROWAVE CIRCUITS

### Ph.D. Thesis

## **Hadi GHASEMZADEH MOMEN**

**Electronics and Communications Engineering Department**

**Electronics Engineering Programme**

Thesis Advisor: Assoc. Prof. Dr. Metin YAZGI Thesis Co-Advisor: Assist. Prof. Dr. Ramazan KÖPRÜ

# ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL OF SCIENCE ENGINEERING AND TECHNOLOGY

# HIGH PERFORMANCE TUNABLE ACTIVE INDUCTORS FOR MICROWAVE CIRCUITS

### Ph.D. Thesis

# Hadi GHASEMZADEH MOMEN (504112204)

**Electronics and Communications Engineering Department**

**Electronics Engineering Programme**

Thesis Advisor: Assoc. Prof. Dr. Metin YAZGI Thesis Co-Advisor: Assist. Prof. Dr. Ramazan KÖPRÜ

## <u>İSTANBUL TEKNİK ÜNİVERSİTESİ</u> ★ FEN BİLİMLERİ ENSTİTÜSÜ

# MİKRODALGA DEVRELERİ İÇIN YÜKSEK BAŞARIMLI AYARLANABİLİR AKTİF ENDÜKTÖRLER

### **Doktora Tezi**

Hadi GHASEMZADEH MOMEN (504112204)

Elektronik ve Haberleşme Mühendisliği Anabilim Dalı

Elektronik Mühendisliği Programı

Tez Danışmanı: Doç. Dr. Metin YAZGI Eş Danışman: Yrd.Doç. Dr. Ramazan KÖPRÜ

**AĞUSTOS 2016**

Hadi GHASEMZADEH MOMEN, a Ph.D. student of ITU Graduate School of Science Engineering and Technology student ID 504112204, successfully defended the dessertation entitled "HIGH PERFORMANCE TUNABLE ACTIVE INDUCTORS FOR MICROWAVE CIRCUITS", which he prepared after fulfilling the requirements specified in the associated legislations, before the jury whose signatures are below.

| Thesis Advisor: | Assoc. Prof. Dr. Metin YAZGI İstanbul Technical University          |  |

|-----------------|---------------------------------------------------------------------|--|

| Co-Advisor:     | <b>Assist. Prof. Dr. Ramazan KÖPRÜ</b><br>Işik University           |  |

| Jury Members :  | Assist. Prof. Dr. Metin HÜNER Istanbul Technical University         |  |

|                 | <b>Prof. Dr. Mustafa KARAMAN</b> Istanbul Technical University      |  |

|                 | <b>Prof. Dr. İsmail Serdar ÖZOĞUZ</b> Istanbul Technical University |  |

|                 | <b>Prof. Dr. Avni MORGÜL</b> Fatih Sultan Mehmet Vakıf University   |  |

|                 | <b>Assis. Prof. Dr. Vedat TAVAS</b> Istanbul Ticaret University     |  |

Date of Submission: 15 July 2016 Date of Defense: 04 August 2016

To my family

#### **FOREWORD**

First and foremost I would like to express my sincerest appreciation to my advisor and Co-Advisor, Assoc. Prof. Dr. Metin YAZGI and Assist. Prof. Dr. Ramazan KÖPRÜ, who have guided me throughout my Ph.D. dissertation with their patience and knowledge whilst allowing me to work in my own way. It was an honor for me to work with them during my time at Istanbul Technical University.

I would like to thank the members of my dissertation committee; Prof. Dr. Avni MORGÜL, Prof. Dr. Mustafa KARAMAN and Assis. Prof. Dr. Metin HÜNER for their valuable points and motivational advices.

My special thanks go to my brother-in-law, Ali, not only during Ph.D. study but also in my life for his emotional supports and fruitful discussions.

I am deeply and forever indebted to my family; my patient father, great mother, lovely sister and brother for their love, support and encouragement throughout my entire life, and in particular, I must acknowledge my wife, without whose endless help, I would not have finished this dissertation.

July 2016

Hadi GHASEMZADEH MOMEN (Electronic Engineer, M.Sc)

# TABLE OF CONTENTS

| <u>I</u>                                                                | Page |

|-------------------------------------------------------------------------|------|

| FOREWORD                                                                |      |

| TABLE OF CONTENTS                                                       | xi   |

| ABBREVIATIONS                                                           | XV   |

| LIST OF TABLES                                                          |      |

| LIST OF FIGURES                                                         |      |

| SUMMARY                                                                 |      |

| ÖZET                                                                    |      |

| 1. INTRODUCTION                                                         |      |

| 1.1 Inductive Properties in High-Speed Applications                     |      |

| 1.1.1 Bandwidth Improvement                                             |      |

| 1.1.2 Impedance Matching                                                |      |

| 1.1.3 Phase Shifting                                                    |      |

| 1.1.4 Frequency Selection                                               |      |

| 1.1.5 Gain Boosting                                                     |      |

| 1.1.6 Power Divider                                                     |      |

| 1.2 Spiral Inductors                                                    |      |

| 1.3 Active inductors                                                    |      |

| 1.4 Conclusion                                                          |      |

| 1.5 Dissertation Organization                                           |      |

| 2. CMOS ACTIVE INDUCTORES                                               |      |

| 2.1 Principles of GC AIs                                                |      |

| 2.1.1 Ideal (lossless) Grounded GC AIs                                  |      |

| 2.1.2 Ideal Floating GC AIs                                             |      |

| 2.1.3 Lossy Grounded GC AIs                                             |      |

| 2.1.4 Lossy floating GC AIs                                             |      |

| 2.2 Active Inductor Properties                                          |      |

| 2.2.1 Frequency Range                                                   |      |

| 2.2.2 Inductance Tunability                                             |      |

| 2.2.3 Quality Factor                                                    |      |

|                                                                         |      |

| 2.2.5 Stability                                                         |      |

| 2.3 CMOS Grounded AI Impelementation Base on GC Topology                |      |

| 2.3.1 Active Inductors Proposed by Yodprasit-Ngarmnil                   |      |

| 2.3.2 Active Inductor Proposed by Uyanik-Tarim                          |      |

| 2.3.3 Noise-Cancelling of A CMOS Active Inductor                        |      |

| 2.3.4 Loss Regulated Active Inductor Proposed by Nair                   |      |

| 2.3.5 Cascoded Flipped Active Inductor Proposed by Saberkari            |      |

| 2.3.6 Low Noise and Low Loss Active Inductor Proposed by Manjula        |      |

| 2.4 CMOS Floating Active Inductors Impelementation Base on GC Topology. |      |

| 2.4.1 Floating Active Inductor Proposed by Mahmoudi                     |      |

| 2.4.2 Floating Active Inductor Proposed by Cetinkava                    |      |

| 2.4.3 Feedback Resistance Floating Active Inductor Proposed by Akbari        |     |

|------------------------------------------------------------------------------|-----|

| 2.5 Chapter Summery                                                          | 42  |

| 2.5 Chapter Summery                                                          |     |

| INDUCTOR CIRCUITS BASED ON GYRATOR-C ARCHITECTURE                            |     |

| 3.1 Introduction                                                             | 44  |

| 3.2 A New Low loss CMOS Active Inductor Circuit                              | 44  |

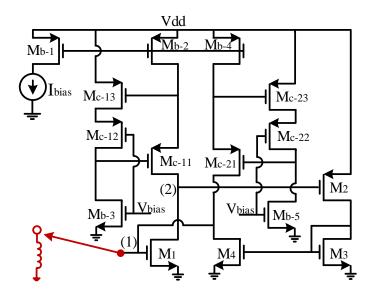

| 3.2.1 Circuit Level Description                                              | 45  |

| 3.2.2 Simulation Results                                                     |     |

| 3.3 A new low-loss active inductor with independently adjustable self-resona | nce |

| frequency and quality factor parameters                                      |     |

| 3.3.1 Theoretical and Implementation Description                             |     |

| 3.3.2 Simulation results and performance analysis                            |     |

| 3.4 Low-Noise CMOS Active Inductor Circuit                                   |     |

| 3.4.1 Circuit and Performance Description                                    |     |

| 3.4.2 Noise improvement of AI                                                |     |

| 3.4.3 Proposed Active Inductor Characterization                              |     |

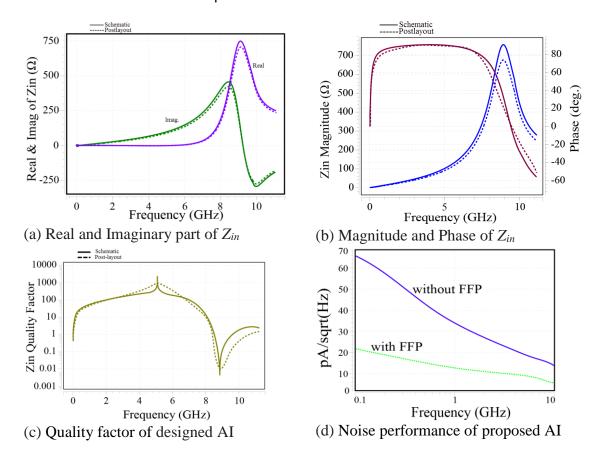

| 3.4.4 Simulation Results                                                     |     |

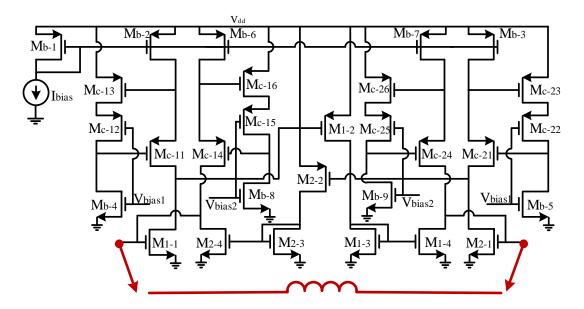

| 3.5 New Low Loss Fully CMOS Tunable Floating Active Inductor                 |     |

| 3.4.1 System Level Description                                               |     |

| 3.4.2 Circuit Level Design                                                   |     |

| 3.4.3 Simulation Results                                                     |     |

| 3.6 Chapter Summery                                                          |     |

| 4. CMOS GYRATOR-C ARCHITECTURES APPLICATIONS                                 |     |

| 4.1 A 3-Axis Accelerometer With an Accurate CMOS GC Based Interface          |     |

| Circuit                                                                      | 81  |

| 4.1.1 A 3-Axis MEMS Capacitive Accelerometer Free of Cross Axis              |     |

| Sensitivity                                                                  | 81  |

| 4.1.1.1 Operation Principles and Structural Design                           | 82  |

| 4.1.1.2 Applied Acceleration Is In One Direction                             |     |

| 4.1.1.3 Applied Acceleration Is In Two Directions                            |     |

| 4.1.1.4 Applied Acceleration Is In Three Directions                          |     |

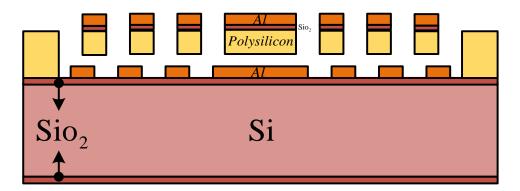

| 4.1.1.5 Fabrication Process                                                  |     |

| 4.1.1.6 Simulation Results                                                   | 86  |

| 4.1.2 An Accurate CMOS Interface Small Capacitance Variation Sensing         |     |

| Circuit                                                                      | 87  |

| 4.1.2.1 Circuit Description                                                  | 88  |

| 4.1.2.2 Proposed Circuit                                                     | 88  |

| 4.1.2.3 Simulation results                                                   | 91  |

| 4.2 Filter Designing By Using Designed Active Inductors                      | 94  |

| 4.2.1 Low-Pass Filter                                                        | 96  |

| 4.2.2 Band-Pass Filter                                                       |     |

| 4.2.2.1 Mathematical Framework                                               | 99  |

| 4.2.2.2 Extracting the characterization of two port network                  | 101 |

| 4.2.2.3 Computational Steps                                                  | 103 |

| 4.2.2.4 Designing 6-order BPF                                                | 104 |

| 4.4 Chapter Summery                                                          |     |

| 5. CONCLUSION                                                                |     |

| 5.1 Summary of the Work                                                      |     |

| 5.2 Scope of Future Works                                                    |     |

| REFERENCES                                                                   | 113 |

| CURRICULUM VITAE | 25 |

|------------------|----|

|------------------|----|

#### **ABBREVIATIONS**

**ABB** : Analog Building Block

AI : Active Inductor BPF : Band Pass Filter

**CAD** : Computer Aided Design

CD : Common-Drain

CG : Common-Gate

CS : Common-Source

**DCT** : Direct Computational technique

**FAI** : Floating Active Inductor **FFP** : Feed Forward Path

**GAI** : Grounded Active Inductor

GC : Gyrator-C

IC : Integrated Circuits

LNA : Low Noise Amplifier

LPF : Low Pass Filter

**MEMS** : Micro Electro-Mechanical System

MRC : Multi-Regulated Cascode

**OTA** : Operational Transconductance Amplifiers

PA : Power Amplifier

PI : Passive Inductor

PSI : Passive Spiral Inductor

PVT : Process Voltage Temperature

QF : Quality Factor RF : Radio Frequency

**RFIC** : Radio Frequency Integrated Circuit **RF-LST** : Real Frequency Line segment Technique

SF : Scaling Factor SFG : Signal Flow Graph

**SRF** : Self-Resonant Frequency

**SRFR** : Self-Resonance Frequency Range **SRFT** : Simplified Real Frequency Technique

**TAI** : Tunable Active Inductor

TFAI : Tunable Floating Active Inductor

TGAI : Tunable Grounded Active Inductor

VCCS : Voltage Control Current Source

VCO : Voltage Control Oscillator

# LIST OF TABLES

|                                                                                | <b>Page</b> |

|--------------------------------------------------------------------------------|-------------|

| Table 1.1: BPF with CMOS spiral and active inductors                           | 5           |

| Table 1.2: Recent publish applications of CMOS AIs                             | 9           |

| Table 3.1: Resistance comparison with-without MRC stage                        | 47          |

| Table 3.2: Proposed GAI Characteristics                                        | 49          |

| Table 3.3: Influence of cascoding transistors transconductances variation on t | he          |

| proposed AI properties                                                         | 53          |

| Table 3.4: Charactrization of the proposed AI in different temprature          | 56          |

| Table 3.5: Performance comparison of the proposed AI with reported AIs         | 57          |

| Table 3.6: Proposed AI Characteristics                                         | 64          |

| Table 3.7: Comparison with Other AIs                                           | 65          |

| Table 3.8: Equivalent resistance with-without MRC stage                        | 72          |

| Table 3.9: Transistors aspect ratio of proposed circuit                        | 75          |

| Table 3.10: Optimized Q and SRF value for different inductance values          | 77          |

| Table 3.11: Comparison with other FAIs                                         | 79          |

| Table 4.1: Accelerometer Characteristics                                       | 86          |

| Table 4.2: Linearity in different frequencies                                  | 93          |

| Table 5.1: Comparison pons and cons of designed AIs                            | 109         |

| Table 5.2: Comparison of designed AIs with reported AIs                        |             |

# LIST OF FIGURES

| <u>F</u>                                                                                    | Page |

|---------------------------------------------------------------------------------------------|------|

| <b>Figure 1.1 :</b> Inductive peaking, (a) Shunt peaking, (b) Series peaking                | 3    |

| <b>Figure 1.2:</b> Impedance matching in narrow-band low-noise amplifiers                   |      |

| <b>Figure 1.3:</b> RF phase shifters with floating inductors and shunt varactors            |      |

| Figure 1.4: Gain boosting of low noise amplifiers using LC tank load                        |      |

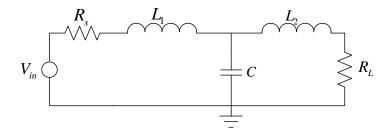

| Figure 1.5: Equivalent circuit of lumped Wilkinson power divider                            |      |

| Figure 1.6: Spiral Inductors (a) planar (b) stacked.                                        |      |

| Figure 2.1 : Ideal grounded GC AI.                                                          |      |

| Figure 2.2 : Simplified schematic of basic transconductors.                                 | . 14 |

| Figure 2.3 : Ideal (lossless) Floating GC AI.                                               |      |

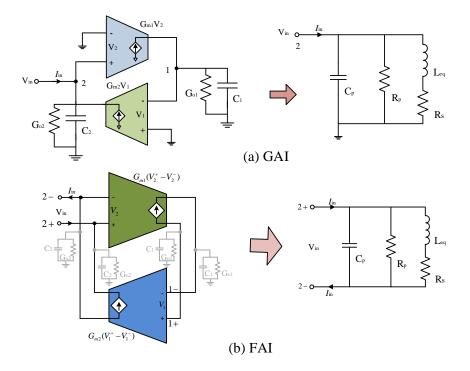

| <b>Figure 2.4 :</b> Block diagram of GAI realization and its equivalent passive model       |      |

| <b>Figure 2.5 :</b> Block diagram of FAI realization and its equivalent passive model       |      |

| Figure 2.6: Bode plots of the impedance of lossy Gyrator-C AI.                              |      |

| Figure 2.7 : Sideview of MOS varactors                                                      |      |

| Figure 2.8: Capacitance variation in MOS varactors.                                         |      |

| Figure 2.9: Inductance tuning via transconductances or load capacitance variation           |      |

| 1 igure 2.7 : inductance tuning via transconductances of four capacitance variation         |      |

| <b>Figure 2.10 :</b> deriving the input-referred noise voltage of CG transconductor         |      |

| Figure 2.11 : Yodprasit-Ngarmnil AI and its passive model.                                  |      |

| Figure 2.12 : Cascode double-feedback active inductor.                                      |      |

| Figure 2.13 : Simplified schematic of Uyanik-Tarim active inductor                          |      |

| Figure 2.14 : Frequency response of the active inductor                                     |      |

| Figure 2.15: Low Noise AI.                                                                  |      |

| Figure 2.16 : Simulated input referred noise with and without NC                            |      |

| <b>Figure 2.17:</b> Small signal model of the simplified active inductor in Figure 2.15.    |      |

| Figure 2.18: Simulated frequency response.                                                  |      |

| Figure 2.19: Active inductor (a) schematic and equivalent small-signal model, (b)           |      |

| typical AI performance at UWB frequencies                                                   |      |

| Figure 2.20: (a) Basic flipped-active inductor, (b) cascoded flipped-active induct          |      |

| and (c) small signal equivalent circuit.                                                    |      |

| Figure 2.21 : Characterizations of the CASFAI: (a) Inductance value, (b) quality            |      |

| factor                                                                                      |      |

| Figure 2.22 : Proposed Low Noise and Low Loss AIs and their Small Signal                    | 33   |

| Models.                                                                                     | 25   |

|                                                                                             |      |

| Figure 2.23: Simulated Frequency Response of Input Impedance.                               |      |

| Figure 2.24: QF Tuning of Modified AI.  Figure 2.25: Noise Voltage of the Modified AI.      |      |

|                                                                                             |      |

| Figure 2.26: Floating AI implementation based on GC architecture                            |      |

| Figure 2.27: Small-signal equivalent circuit of FAI.                                        |      |

| Figure 2.28: The gyrator-C equivalent of the floating active inductor                       |      |

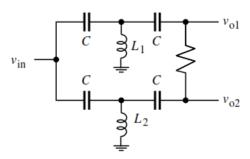

| Figure 2.19 : 3-order LPF.                                                                  |      |

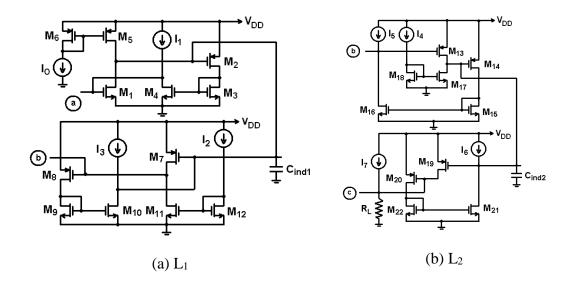

| <b>Figure 2.30 :</b> FAIs circuits used in the filter a) L <sub>1</sub> , b) L <sub>2</sub> | 40   |

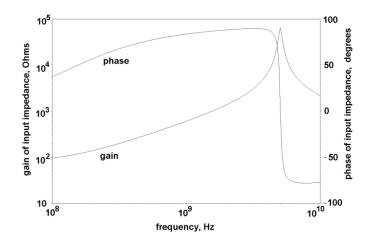

| Figure 2.31: Freque                   | ency response of FAIs                                                | 40 |

|---------------------------------------|----------------------------------------------------------------------|----|

| Figure 2.32: Simpli                   | ified schematic of feedback resistance FAI                           | 41 |

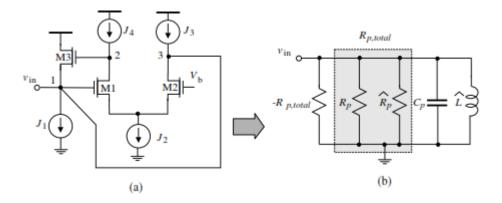

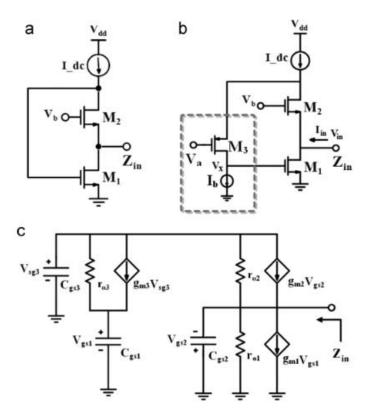

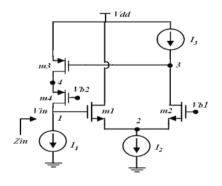

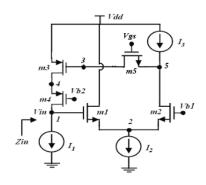

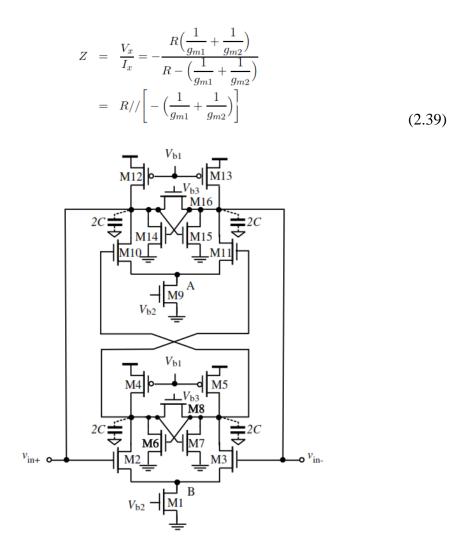

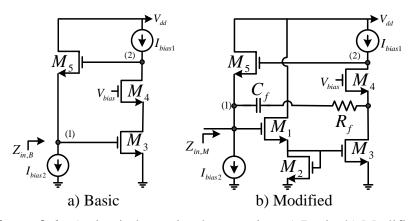

|                                       | atic of gyrator-C active inductors a) Basic b) Modified              |    |

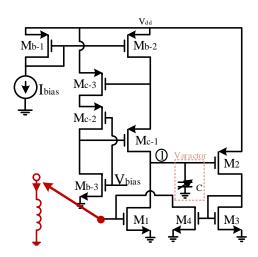

|                                       | ed GAI                                                               |    |

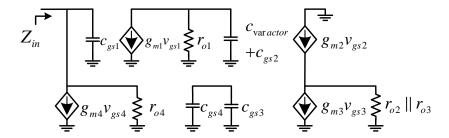

| Figure 3.3: Small-s                   | ignal equivalent model of proposed GAI                               | 47 |

|                                       | AI simulation results                                                |    |

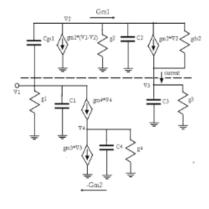

| Figure 3.5: SFG of                    | GC topology                                                          | 51 |

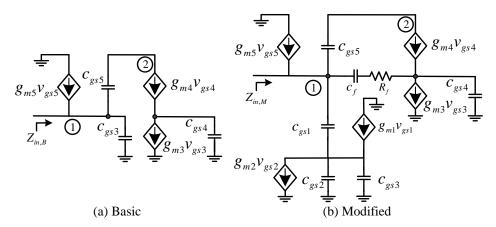

| Figure 3.6 : Active i                 | inductor implementation, a) Basic, b) Modified                       | 51 |

| Figure 3.7: Small-s                   | ignal model, a) Basic, b) Modified                                   | 52 |

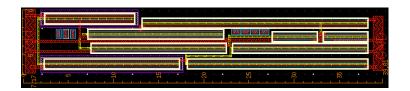

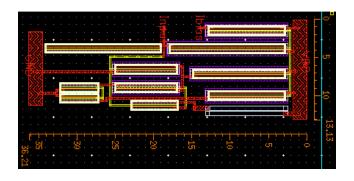

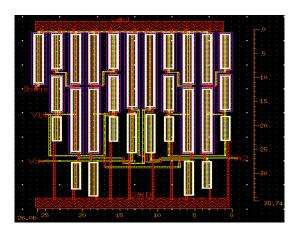

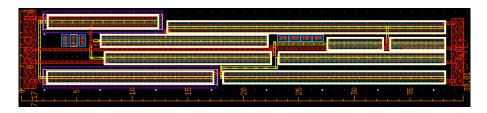

| Figure 3.8: Layout                    | of the proposed circuit                                              | 54 |

|                                       | ncy response of the proposed AI                                      |    |

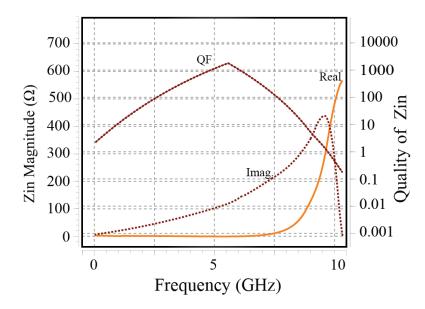

|                                       | eart, imaginary part and QF of the of the input impedance Zin        |    |

| _                                     | esult of Monte Carlo analysis of GC circuit for ±5 % mismate         |    |

|                                       | sistors aspect ratio and threshold voltage (No. of iterations =      |    |

|                                       |                                                                      |    |

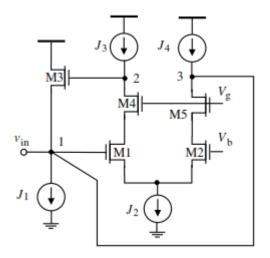

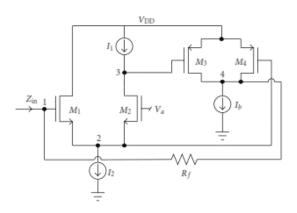

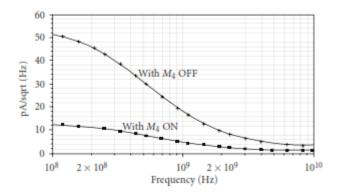

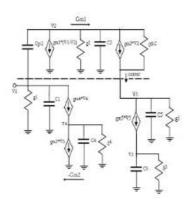

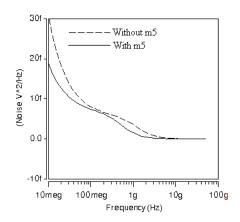

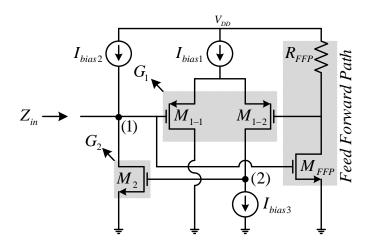

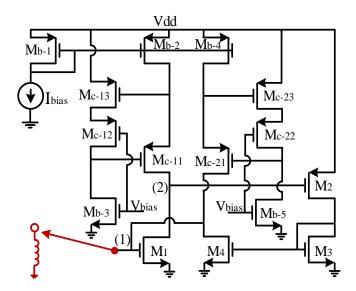

| ,                                     | sed low-noise and low-loss AI.                                       |    |

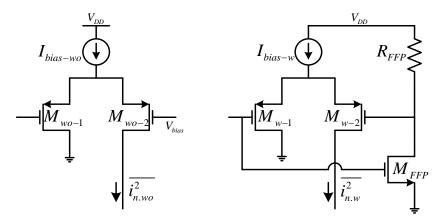

|                                       | current comparison in differential pair with-without FFP             |    |

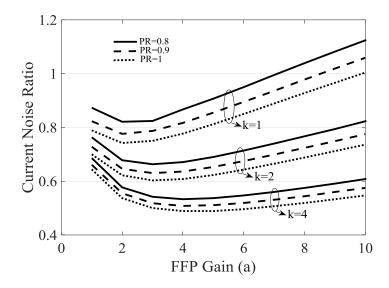

|                                       | current ratio of proposed AI with FFP.                               |    |

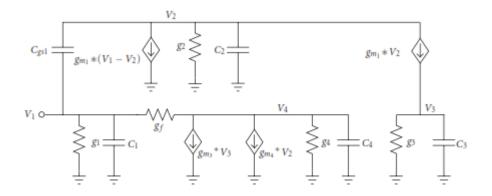

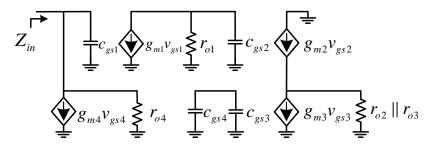

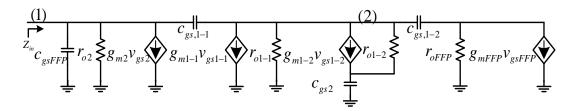

| 0                                     | -signal model of proposed AI (Figure 3.12)                           |    |

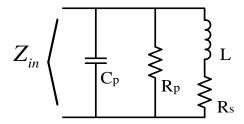

|                                       | alent RLC model                                                      |    |

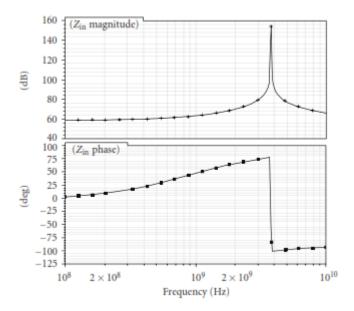

|                                       | sed AI simulation results                                            |    |

|                                       | t of proposed AI                                                     |    |

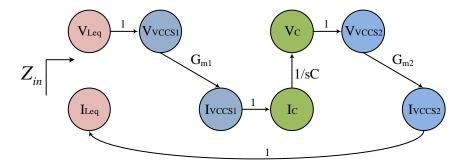

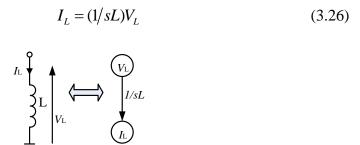

|                                       | eal inductor and SFG representation                                  |    |

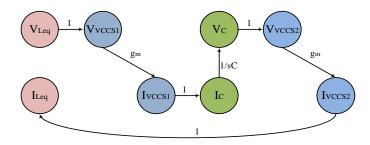

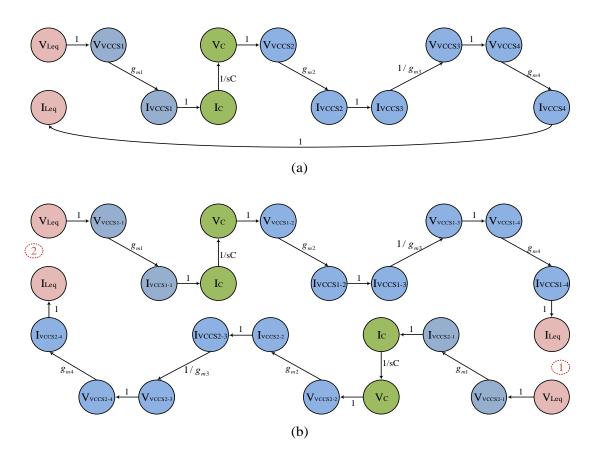

|                                       | al SFG for AI's circuit generation with VCCS                         |    |

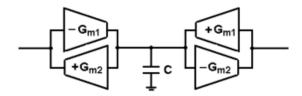

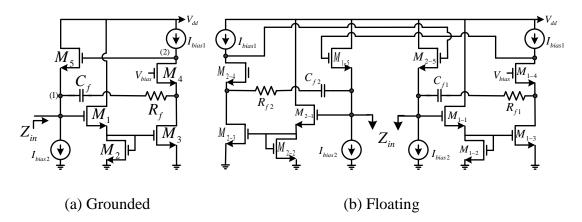

| Figure 3.21 : Modif                   | ied SFG (a) GAI. (b) FAI                                             | 68 |

|                                       | diagram of AI realization by OTA and equivalent passive              |    |

|                                       | (a) Grounded (b) Floating                                            | 69 |

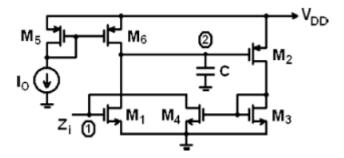

|                                       | ified CMOS-based GAI (a) basic, (b) modified                         |    |

|                                       | S varactor                                                           |    |

|                                       | ied GAI.                                                             |    |

|                                       | -signal equivalent of proposed GAI                                   |    |

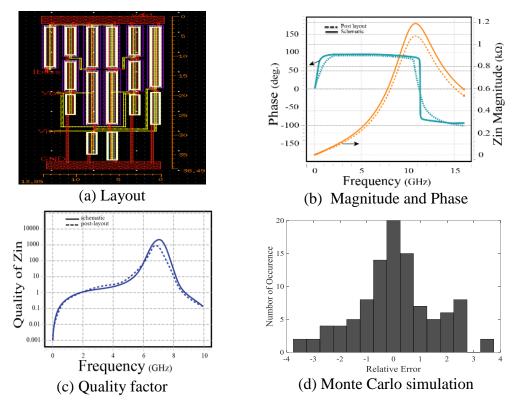

|                                       | t implementation of the proposed FAI                                 |    |

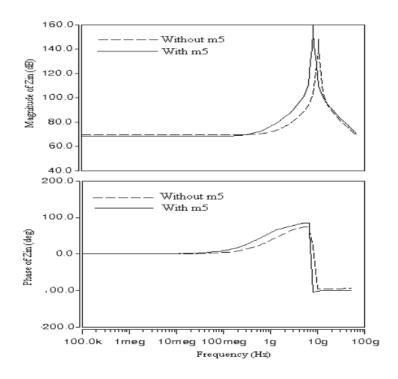

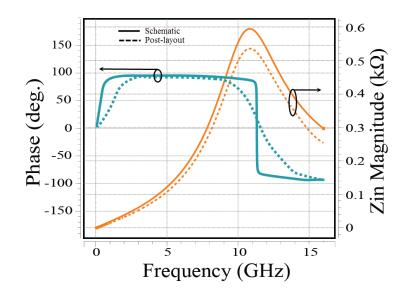

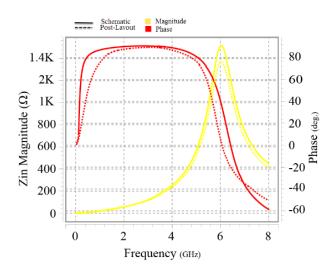

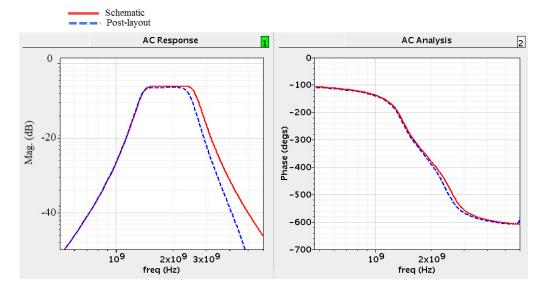

|                                       | arison AI circuits with and without MRC stage (magnitude             |    |

|                                       | iase).                                                               |    |

|                                       | t for FAI simulation                                                 |    |

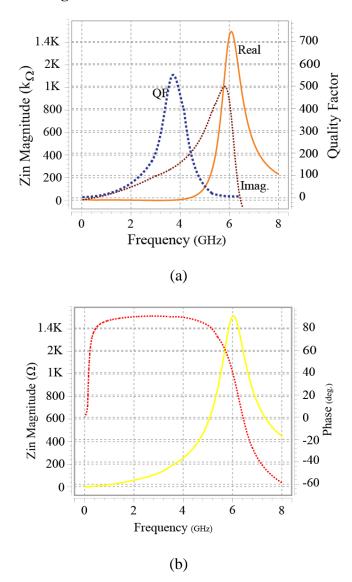

|                                       | mance of proposed AI, (a) real and imaginary parts and QF,           |    |

|                                       | gnitude and phase                                                    | 76 |

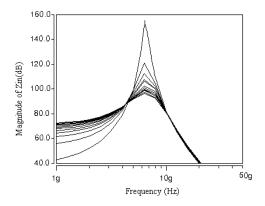

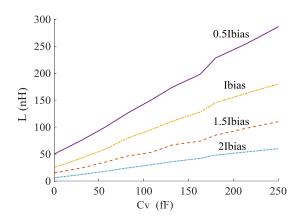

|                                       | ility of AI by changing bias current and varactor capacitance        |    |

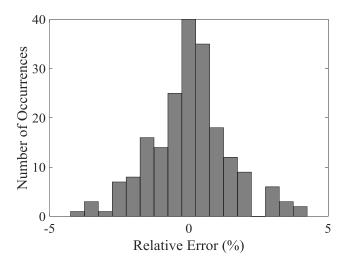

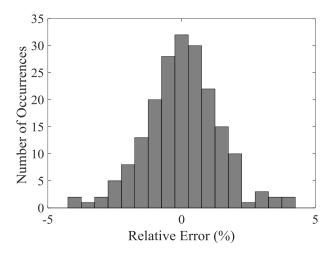

| 0                                     | esult of Monte Carlo analysis of GC circuit for ±5 % mismate         |    |

| 0                                     | nsistors aspect ratio and threshold voltage (No. of iterations =     |    |

|                                       |                                                                      |    |

| Figure 3.33 : Lavou                   | t of the proposed FAI                                                | 78 |

|                                       | itude and Phase of AI (schematic and post-layout simulation)         |    |

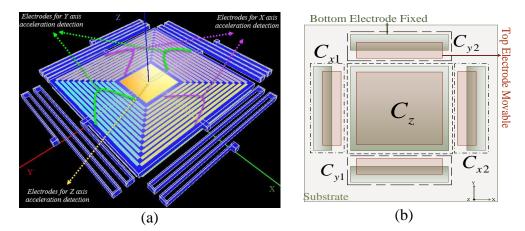

| 0                                     | ed Structure, (a)3D view, (b) Electrodes Arrangement (2D, to         |    |

|                                       | su su deture, (a) 22 + 12 + 1, (e) 21 est estes 1 mangement (22), to | -  |

| · · · · · · · · · · · · · · · · · · · | ection view of final structure                                       |    |

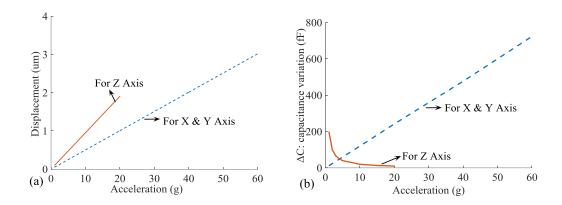

| 0                                     | lacement versus applied acceleration in 3-Axis, (b)Capacitano        |    |

|                                       | n versus applied acceleration in 3-Axis                              |    |

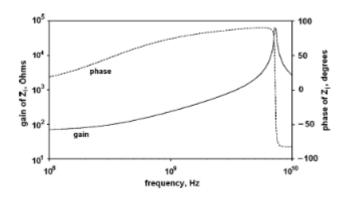

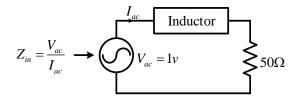

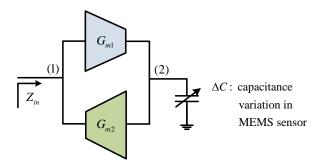

|                                       | :-C topology                                                         |    |

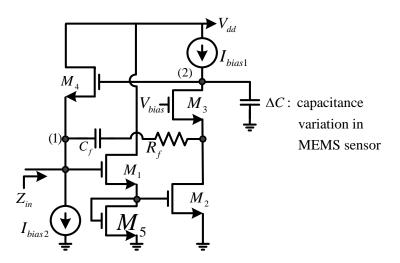

| •                                     | atic of the proposed circuit                                         |    |

| 5 Semente                             | r-r-r                                                                | 07 |

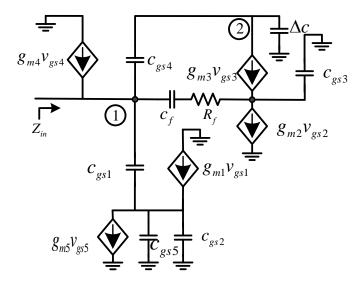

| Figure 4.6: Small-signal equivalent of proposed circuit                              | 90 |

|--------------------------------------------------------------------------------------|----|

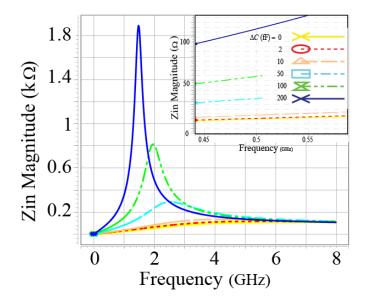

| Figure 4.7: Zin Mag. versus frequency in different capacitance variation             | 92 |

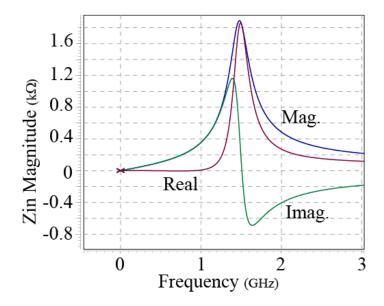

| <b>Figure 4.8 :</b> Mag., real and Imaginary Parts of Zin when $\Delta C$ =200fF     | 92 |

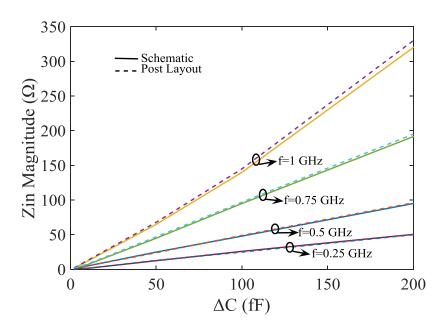

| Figure 4.9: Zin Magnitude versus capacitance changing in f=0.25, 0.5, 0.75 and 1     | _  |

| (GHz)                                                                                | 93 |

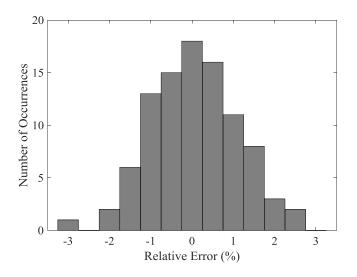

| Figure 4.10: The result of Monte Carlo analysis of GC circuit for $\pm 5$ % mismatch |    |

| in transistors aspect ratio and threshold voltage when $\Delta C=100$ fF and         | 1  |

| f=0.5 GHZ (No. of iterations = 100)                                                  | 94 |

| Figure 4.11: Layout of proposed circuit                                              | 94 |

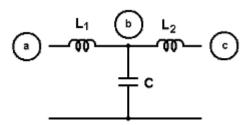

| Figure 4.12: Low pass filter topology                                                | 96 |

| Figure 4.13 : Core GAI of FAI                                                        | 97 |

| Figure 4.14: The GC equivalent of the FAI.                                           | 97 |

| Figure 4.15: FAI circuit used in filter designing                                    | 98 |

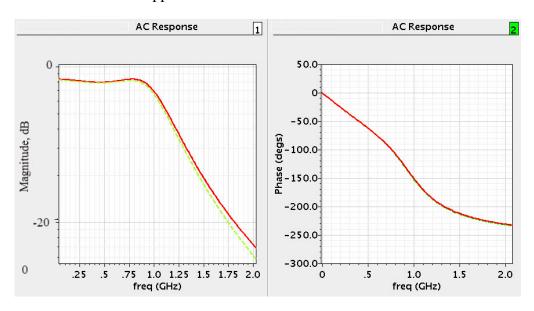

| <b>Figure 4.16 :</b> Frequency response of LPF with passive (red) and active (green) |    |

| inductors                                                                            |    |

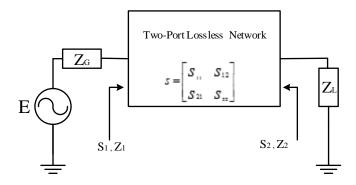

| Figure 4.17: Two port network                                                        | 00 |

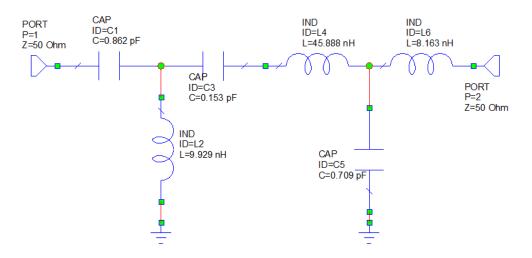

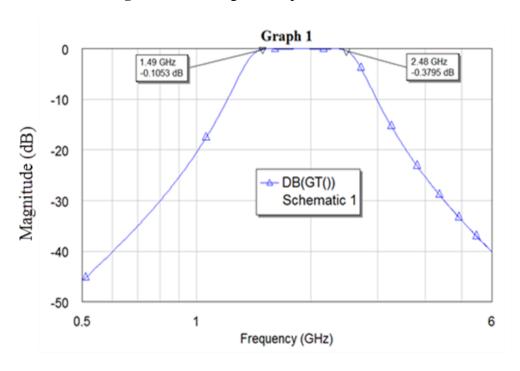

| Figure 4.18: Designed lumped element BPF.                                            | 05 |

| Figure 4.19: TPG performance of designed BPF                                         | 05 |

| Figure 4.20: AC response proposed BPF with passive (red) and active inductors        |    |

| (blue) - Magnitude and Phase 1                                                       | 06 |

| Figure 4.21: Utilized grounded and floating AIs in 6-order BPF, a)Grounded,          |    |

| b)Floating1                                                                          | 06 |

# HIGH PERFORMANCE TUNABLE ACTIVE INDUCTORS FOR MICROWAVE CIRCUITS

#### **SUMMARY**

There is critical need for inductive characteristics in RF applications, especially in filters, LNA, VCO, bandwidth-enhancement in many kinds of amplifiers, phase shifters, power divider and matching networks. The drawbacks of using passive and spiral inductors in CMOS process are discussed in the literature. It is shown that these kind of inductors suffer from a low quality factor, a low self-resonant frequency, a low and fixed inductance value and the need for a large silicon area.

Furthermore, it is shown in the literature that CMOS Active Inductors (AIs), which are synthesized using MOS transistors, offer a number of attractive characteristics as compared with their spiral counterparts. These characteristics include a low silicon consumption, a large and tunable self-resonant frequency, a large and tunable inductance, a large and tunable quality factor, and fully realizable in digital CMOS technologies.

Then principles, topologies, characterizations and implementation of the Gyrator-C (GC) network is discussed in-depth. The GC networks, which are implemented by operational transconductance amplifier, are suitable for RF application. This property arises from their minimum usage of active elements. It is shown that both grounded and floating active inductors can be implemented by GC networks. To provide a quantitative measure of the performance of AIs, a number of figure-of-merits have been introduced in the thesis. These figure-of-merits include frequency range, inductance tunability, quality factor, noise and power consumption. Due to parasitic components of CMOS transistors, designed AIs have inductive behavior in a specified frequency range. The low frequency bound is set by the frequency of the zero of the gyrator-C networks while the upper frequency bound is set by Self-Resonance Frequency (SRF). One of the key advantages of active inductors over their spiral counterparts is the large tunability of their inductance. The inductance of GC AIs can be tuned by varying either the transconductances of the transconductors or the load capacitance, which is implemented by MOS varactor.

Based on GC topology, there are many reported CMOS AI circuits in literature. All of them have tried to invent high performance AI by using different techniques. Some of recent proposed Grounded AI (GAI) and Floating AI (FAI) circuits are reviewed in the thesis. Some of them use negative resistor to compensate the loss of AI for QF enhancement. Some others try to use minimum number of transistors in order to increase the self-resonance frequency of AI for RF applications. In some applications, AIs are used in LNA circuits for gain boosting purpose. In that applications, designers have tried to cancel the noise of AI by using a feedback stage with a degeneration resistor to reduce the noise contribution to the input. The main aim of all the techniques is to cancel or reduce the effects of parasitic components.

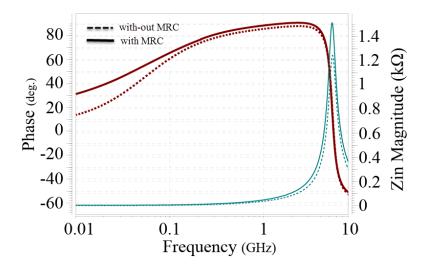

In the thesis, four new grounded and floating AIs are designed by using advanced circuit techniques. The first one, Multi Regulated Cascode (MRC) stages are employed for lowering conductance in input and output nodes of AI. Thus, Q performance is improved. Since these stages are used only for increasing impedance of input/output nodes, they are made up of PMOS transistors in order to:

- minimize the input transistor as small as possible in order to adjust second stage biasing,

- decrease the number of transistors in main path of AC signal

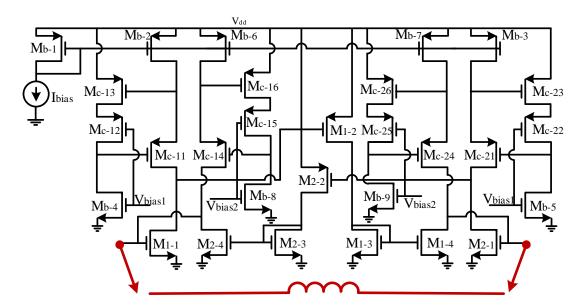

Theoretical analysis and post-layout simulation results shows the effectiveness of using MRC stages usage in properties of AI. High Q symmetric floating version of low loss inductor is also designed by utilizing MRC stages.

Designers do their best to improve SRF and QF, two main characteristics in term of AI performance. An AI with ability to adjust its SRF and QF without affecting each other is designed and simulated as a third. The cascoding and RC feedback structures are used in the new design of AI. As it discussed before, input transistor is very important regarding to AI characterizations. Cascoding input transistor gives the ability to adjust the first gyrator's transconductance and input parasitic capacitance independently which it results in adjusting the self-resonance frequency and quality factor separately. Due to our best knowledge from literature reviewing, it is first time that the properties of an inductor can be adjusted independently. Furthermore, the inductance value can be adjusted by other transistor's transconductances. Also, the RC feedback is utilized to cancel the parasitic series-resistance of AI which results in QF enhancement. Since, bias condition of cascoding transistors is provided by a diodeconnected transistor, the proposed structure is robust in terms of performance over variation in process, voltage and temperature.

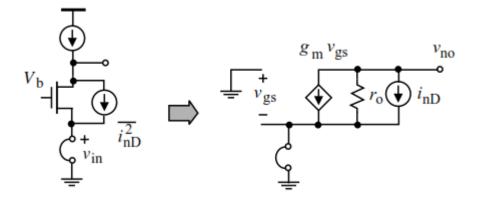

The Noise of designed AIs has limited the use of them in RF applications such as LNAs. The main noise source of an AI is its input transistor. In order to have low noise AI, the input transistor should be designed large enough. But it leads to low SRF which limited the inductive frequency band. As a fourth active inductor design, a low-noise and low-loss AI is presented suitable for RF low noise applications. Utilizing all transistors in Common Sourse (CS) configuration on the AI circuit leads to low conductance nodes which causes the AI to have high Q. P-type MOS transistors and Feed-Forward Path (FFP) are employed to decrease noise of the AI, respectively.

The GC topologies can convert a low capacitance variation to high impedance changing which makes it a good choice for capacitive sensors. The capacitive based micro sensors convert mechanical signals to small capacitance variation. The capacitance variation in micro sensor is in the range of femto-Farads which makes it difficult to sense. Thus, the GC topologies can be used in capacitive sensors in order to sense small capacitive variations. In the thesis, this technique is used in a new accelerometer sensor. It is first time that a gyrator-C network is employed as an interface circuit for capacitive change detection in micro sensors. The new accelerometer structure is designed by using with ability to cancel cross section sensitivity. The sensor's electrodes are located in such a way that enables the structure to detect acceleration in 3-axis independently. Embedding all 3-axis detecting electrodes in a single proof mass and ability to detect acceleration orientation are salient features of the proposed sensor. Consequently, a new GC configuration for sensing very small capacitance changes in a capacitive sensor is presented in the thesis. In the proposed configuration, the operating frequency range and scaling factor can be

adjusted without affecting each other by tuning the bias currents of utilized gyrators. In addition, the proposed configuration employs RC feedback together with the cascoding technique to cancel the effect of the parasitic components in order to get accurate scaling from gyrator-C network.

Finally, in order to show versatility of designed AIs, they are used in designed third and sixth order broadband microwave filters. The first one is a third order Chebyshev low pass filter. The second one, which is designed by using simplified real frequency technique is a sixth order Chebyshev band pass filter. The simulated frequency response of filters prove the workability of the designed AIs.

## MİKRODALGA DEVRELERİ İÇİN YÜKSEK BAŞARIMLI AYARLANABİLİR AKTİF ENDÜKTÖRLER

### ÖZET

RF uygulamalarında enduktif karakteristiğe önemli ölçüde ihtiyaç duyulmaktadır; bunlar, özellikle filtreler, düşük gürültülü yükselteçler (LNA, low noise amplifiers), gerilim kontrollü osilatörler (VCO, voltage controlled oscillators), pek çok farklı türde yükselteç için band genişliği iyileştirilmesi, faz kaydırıcılar, güç bölücüler ve eşleştirme (matching) devreleri vb. uygulamalardır. Pasif sarmal çip-içi CMOS endüktansların eksik yönleri ayrıntılı olarak literatürde tartışılmıştır. Bu tür endüktanslar düşük değer katsayısı (quality factor), düşük öz-rezonans frekansı (SRF, self-resonance frequency), sabit ve düşük değerli endüktans ve geniş bir silikon (silicon) alanı gerektirmeleri gibi istenmeyen özelliklere sahiptirler.

Diğer yandan, MOS transistorlar kullanılarak sentezlenen CMOS aktif endüktansların, pasif sarmal eşdeğer yapıları ile karşılaştırıldığında pek çok çekici karakteristik özellik sunabildikleri gösterilmiştir. Bunlar; geniş bir bölgede ayarlanabilir öz-rezonans frekansı başarımı, geniş bir bölgede ayarlanabilir endüktans başarımı, geniş bir bölgede ayarlanabilir değer katsayısı başarımı, CMOS teknolojileri ile tümüyle gerçeklenebilme ve az alan kaplama gibi karakteristik özellikleri olarak ortaya konulmaktadır.

Literatürde jiratör-C (GC) prensibi, topolojisi, karakterizasyonu ve uygulamaları ayrıntılı olarak ele alınmaktadır. İşlemsel geçiş-iletkenliği kuvvetlendiricisi (OTA, operational transconductance amplifier) ile gerçeklenen GC devreleri, RF uygulamaları için oldukça uygundur. Bu özellik, GC yapılarının söz konusu yapı kullanılarak en az sayıda aktif eleman ile gerçeklenebilmesinden kaynaklanmaktadır. Gerek topraklı (grounded) gerekse yüzen (floating) aktif endüktansların GC devreleri ile gerçeklenebildiği gösterilmiştir. Aktif endüktansların başarımlarının nicel olarak ölçülmesi amacıyla, çok sayıda ölçüt ortaya konulmuştur. Bu ölçütler frekans çalışma aralığı, endüktans ayarlanabilirliği, değer katsayısı, gürültü ve güç tüketimi gibi temel özellikleri içerirler. CMOS transistorların parazitik bileşenlerinden dolayı tasarlanan

aktif endüktanslar belirli bir frekans bölgesinde endüktif davranış gösterirler. Alt frekans sınırı, GC devrelerinin sıfır frekansı ile belirlenirken; üst frekans sınırı ise özrezonans frekansı ile belirlenir. Aktif endüktansların pasif sarmal eşdeğer yapılarına göre en önemli üstünlüklerinden biri de; endüktanslarının geniş bir değer aralığıunda ayarlanabilir olmasıdır. GC aktif endüktansların endüktans değeri, transistorların geçiş-iletkenliklerinin ya da MOS varaktörlerle gerçeklenen yük kapasitanslarının değiştirilmesi ile ayarlanabilir.

Literatürde, GC topolojisine dayalı pek çok CMOS AI (active inductor) devresi bildirilmiştir. Bunların tümü, farklı teknikler kullanılarak yüksek başarımlı AI yapıları oluşturmayı amaçlamışlardır. Bu tezde, bunlardan güncel olan bazı GAI (grounded AI) ve FAI (floating AI) yapıları gözden geçirilmiştir. Bunlardan bazıları, değer katsayısını (QF) iyileştirmek amacıyla, AI kaybını telafi etmek için negatif direnç kullanmışlardır. GC yapıları RF uygulamaları için tasarlandıklarında en az sayıda transistor kullanımı çok kritiktir. Çünkü bu durum AI öz-rezonans frekansının artmasına yardımcı olur. AI'ler, kazanç artırma amacıyla LNA'lerde geniş kullanım alanı bulabilmektedirler. Diğer taraftan, AI yapılarının en önemli dezvantajlarından biri gürültü başarımının pasif endüktanslara nispeten yüksek olmasıdır. Literatürde bu dezavantajı gidermek amacıyla teklif edilen yaklaşımlardan biri dejenerasyon direncinin bulunduğu bir geribesleme katı kullanılarak girişe gelen gürültü katkısını azaltmayı amaçlamıştır. Literatürde teklif edilen tekniklerin amacı, parazitik bileşenlerin etkisini azaltmak ya da tümüyle ortadan kaldırmaktır.

Bu tezde, ileri devre teknikleri kullanılarak, yeni topraklı (grounded) ve yüzen (floting) AI yapıları tasarlanmıştır. AI giriş ve çıkış düğümlerine ait iletkenlikleri azaltmak için çoklu-düzenlenmiş kaskod (multi-regulated cascode, MRC) katları QF değerini iyileştirme amacıyla kullanılmaktadır. MRC katı PMOS transistorlarıyla oluşturulmuştur. PMOS transistor kullanımı,

- ikinci kat kutuplamasını ayarlayabilmek amacıyla, giriş transistor boyutunun mümkün olduğunca azaltılmasını,

- ana AC işaret yolundaki transistor sayısının azaltılmasını, sağlamaktadır.

Tezde sunulan teorik analiz ve serim sonrası benzetim sonuçları, MRC katı kullanımının AI özelliklerine yaptığı etkiyi göstermektedir. Elde edilen sonuçlar bu

katların AI tasarımında yüksek QF elde edilmesini imkan tanıdığını ortaya koynaktadır.

Literatürde, iki ana AI başarım karakteristiği olan SRF ve QF başarımlarının iyileştirmesi için çok sayıda çalışma bulunmaktadır. Bu tezde, birbirlerini etkilemeksizin SRF ve QF başarımlarının ayarlanabilmesi özelliğine sahip bir AI'ın tasarımı ve benzetgimi yapılmıştır. Kaskod ve RC geribesleme yapıları yeni AI tasarımında kullanılmıştır. Daha önce de tartışıldığı üzere, AI karakterizasyonu açısından giriş transistoru çok önemlidir. Girişi transistorunun kaskodlanması, ilk jiratörün geçiş-iletkenliğinin ve giriş parazitik kapasitansının birbirinden bağımsız olarak ayarlanması gibi önemli ve kullanışlı bir özelliği beraberinde getirir. Bunun yanısıra, endüktansın değeri diğer transistorun iletkenliği ile ayarlanabilir. AI parazitik seri-rezistansını yok etmek amacıyla kullanılan RC geribeslemesi, QF iyileştirmesini sağlayabilmektedir. Kaskod transistorların kutuplama koşulu bir diyot-bağlı transistor ile sağlandığından; önerilen yapı proses, gerilim ve sıcaklık değişimleri açısından kararlı ve yüksek başarımlıdır.

AI yapılarında karşılaşılan düşük gürültü başarımı, AI'ların LNA gibi RF uygulamalarda kullanımını sınırlamaktadır. Bir AI'ın ana gürültü kaynağı giriş transistorudur. Düşük gürültülü AI elde etmek için, giriş transistoru yeterince büyük boyutlu olarak tasarlanmalıdır. Ne var ki, büyük boyutlu böyle bir transistor, düşük bir SRF ve dolayısıyla sınırlı bir endüktif bandı beraberinde getirir. Bu tezde, düşük gürültülü ve az kayıplı uygun bir AI, düşük gürültü gerektiren RF uygulamaları için sunulmuştur. Teklif edilen AI devresindeki tüm transistorların ortak-kaynak (common-source, CS) yapısında kullanılması, düşük iletkenliğe sahip düğümlerin dolayısıyla yüksek QF değerine sahip bir AI'ın elde edilmesine olanak sağlamaktadır. AI gürültüsünü azaltmak için, sırasıyla P-tipi MOS transistorlar ve ileri-besleme yolu yapısı (feed-forward path, FFP) kullanılmaktadır.

Bilindiği gibi, sensörler çok çeşitli fiziksel büyüklüklerin eletrik mühendisiliği alanına taşınmasını sağlamaktadır. Çok geniş kullanım alanı bulan sensör tiplerinden biri kapasitif mikro algılıyıcılardır. Kapasitif mikro algılayıcılar mekanik hareketleri küçük kapasitans değişimlerine çevirirler. Micro algılayıcıdaki kapasitans değişimi femto-Farad mertebesinde olup algılamayı zorlaştırmaktadır. Diğer yandan, küçük bir kapasitans değişimini yüksek bir empedans değişimine çevirebilmeleri dolayısıyla, GC topolojilerinin kapasitif algılayıcılarda kullanılabileceğini söylemek mümkündür.

Bu tezde, bu düşünceden yola çıkılarak, kesit duyarlılığını yok etme yeteneğine sahip yeni bir 3-eksen ivme-ölçer tasarlanmıştır. Yapının, her eksendeki ivmeyi bağımsız olarak algılayabilmesi için, algılayıcı elektrodları uygun olarak yerleştirilmiştir. Daha sonra, bir kapasitif algılayıcıdaki çok küçük kapasitans değişimlerini algılayabilmek için yeni bir GC yapısı teklif edilmiştir. Önerilen yapıda, çalışma frekansı aralığı ve ölçekleme çarpanı, kutuplama akımlarının ayarlanması suretiyle birbirini etkilemeksizin ayarlanabilmektedir. Ayrıca, önerilen yapıda, parazitik bileşenlerin etkisini yok etmek için RC geribesleme ve kaskod yapılar kullanılmaktadır.

Son olarak, bu tezde sunulan AI'ların çok amaçlı özellikte olduğunu göstermek amacıyla, 3 ve 6. dereceden geniş bantlı mikrodalga filtrelerde kullanılmaları ele alınmıştır. İlki 3. dereceden bir Chebyshev alçak geçiren filtredir. Basitleştirilmiş gerçel frekans tekniği (SRFT, simplified real frequency technique) ile tasarlanan ikincisi ise, 6. dereceden bir Chebyshev band geçiren filtredir. Filtrelerin benzetimle elde edilmiş frekans yanıtları, bu tezde sunulan AI'ların literatürdeki yapılara güçlü birer alternatif olduklarını ortaya koymaktadır.

#### 1. INTRODUCTION

Most of nowadays high-volume customer applications requires the accessibility of low power, low cost and remote microsystems. According to these necessities, CMOS technology has turn into one of the most important alternatives for wireless communication systems. However, CMOS Spiral Inductors have found a broad range of applications in high-speed analog signal processing including impedance matching [1] and gain-boosting in wireless transceivers [2], bandwidth improvement in broadband data communications over wire and optical channels [3], oscillators and modulators [4, 5], RF bandpass filters [6], RF phase shifters [7], RF power dividers [8], and coupling of high-frequency signals [9], to name a few. Traditionally, passive inductors and transformers are off-chip discrete components. The need for off-chip communications with these passive components severely limits the bandwidth, reduces the reliability, and increases the cost of systems [10, 11]. Since early 1990s, a significant effort has been made to fabricate inductors and transformers on a silicon substrate such that an entire wireless transceiver can be integrated on a single substrate monolithically [12, 13]. In the mean time, the need for a large silicon area to fabricate spiral inductors and transformers has also sparked a great interest in and an intensive research on the synthesis of inductors and transformers using active devices, aiming at minimizing the silicon consumption subsequently the fabrication cost and improving the performance [14, 15].

In this chapter, the properties of spiral and active inductors, their advantages and limitations and the impact of them on the application of these devices are looked. Section 1.1 demonstrates the critical need for an inductive characteristic in high-speed applications. Then section 1.2 dicuses about spiral inductors. In section 1.3, the pros and cons of Active Inductors (AIs) are investigated. The chapter is concluded in section 1.4.

### 1.1 Inductive Properties in High-Speed Applications

In order to improve performance of the high-speed systems, such as improving bandwith, boosting gain, selecting frequency and matching networks, inductive charactristics are critically needed. These applications include LC tank oscillators, bandwidth enhancement in broadband communications, impedance matching in narrowband communications, phase shifting for RF antennas and radars, RF power dividers, frequency selection, in particular, RF bandpass filters, RF power amplifiers, and gain boosting of RF low-noise amplifiers. Some of the aforementioned applications are discussed briefly in upcoming subsections.

## 1.1.1 Bandwidth Improvement

Bandwith is a ciritical in Designing broadband circuits, such as amplifiers, matching networks and etc. The bandwidth of a circuit is set by the time constant of the critical node, i.e. the node that has the largest time constant, of the circuit. Three approaches, namely inductive peaking, current-mode signaling, and distributed amplification, are widely used to improve the bandwidth of circuits. The inductive peaking approach is discussed in next paragaragh and extra information about other approaches are fined at [16].

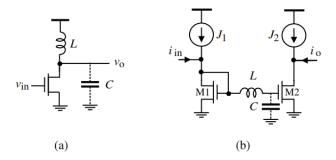

Inductive peaking: The idea is to place an inductor at the node where a large nodal capacitance exists such that the first-order RC network associated with the node is replaced with a second-order RLC network. Because a RLC network has three different modes of operation, namely over damped, critically damped, and under damped. The bandwidth in these three cases differs with under-damped RLC systems exhibit the largest bandwidth. Both shunt peaking [16, 17] and series peaking [18], have been used, as shown in Figure 1.1. It was demonstrated in [16, 17] that inductive shunt peaking can improve the bandwidth of a common-source amplifier by as much as 70%. As shown in Figure 1.1(a&b), in the shunt peaking the peaking inductor *L* is in parallel with the dominant capacitor *C* and in series peaking type it is in series with the dominant *C*.

**Figure 1.1:** Inductive peaking, (a) Shunt peaking, (b) Series peaking.

## 1.1.2 Impedance Matching

For decreasing signal reflection at interface of channels and high-speed circuits, impedance matching is required. Resistors are usually used to provide a matching impedance in broadband communication systems as impedance matching is required over a broad frequency spectrum. Frequency-dependent elements, such as capacitors and inductors, can not be used for impedance matching in broadband communication systems simply due to their frequency-dependent characteristics. But most of the communication circuits operate in a narrow-band mode. Although resistors can be used for these applications, the high level of the thermal noise of resistors limited their usage in wireless communications where there is a stringent constraint on the noise performance of these systems. Instead, noiseless and lossless elements such as capacitors and inductors are widely used in narrow-band impedance matching because these frequency-dependent noiseless elements can provide the desired impedance in a narrow frequency band and at the same time keep the noise at required level [19].

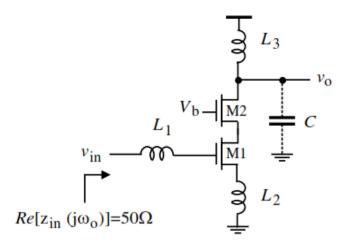

Figure 1.2 shows widely used termination scheme for narrowband Low-Noise Amplifiers (LNAs). Neglecting  $C_{gd}$  and other parasitic capacitances, the input impedance of the LNA can be written as:

$$Z_{in} = \left[ j\omega(L_1 + L_2) + \frac{1}{j\omega C_{gs_1}} \right] + \frac{g_{m1}L_2}{C_{gs_1}}$$

(1.1)

Where  $C_{gs1}$  and  $g_{m1}$  are the gate source capacitance and transconductance of  $M_1$ , respectively. It is seen from (1.1) that reactive part of input impedance (first term) can be made zero by imposing:

Figure 1.2: Impedance matching in narrow-band low-noise amplifiers.

$$j\omega(L_1 + L_2) + \frac{1}{j\omega C_{gs_1}} = 0$$

(1.2)

The input impedance of the LNA in this case becomes purely resistive and is given by:

$$Z_{in} = \frac{g_{m1}L_2}{C_{gs_1}} \tag{1.3}$$

The reason of using two inductors in gate and source of  $M_1$  is as following: Once the dimension of  $M_1$  is chosen,  $g_{m1}$  and  $C_{gs1}$  are determined. The desired input impedance of the LNA in this case can be obtained by adjusting  $L_2$ . Once  $L_2$  is chosen, the value of  $L_1$  can be tuned to ensure the total cancellation of the reactive part of the input impedance.

### 1.1.3 Phase Shifting

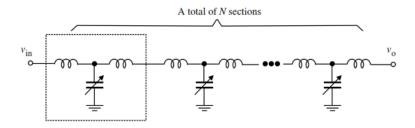

A well-designed phase shifter should possess the characteristics of a low insertion loss, a high return loss, and a large phase shift range. The common configuration of RF phase shifters is shown in Figure 1.3. The tuning of the amount of the phase shift is carried out by varying the capacitance of the shunt varactors.

**Figure 1.3:** RF phase shifters with floating inductors and shunt varactors.

## 1.1.4 Frequency Selection

Frequency selection systems are implemented by lumped elements. For instance, Bandpass Filters (BPFs) with a high passband center frequency are used extensively in narrow-band wireless communications for RF band selection. Implementing inductors with antiont approaches are not compatible with CMOS technologies, which are domimnant in Radio Frequency Integrated Circuit (RFIC) designing. The recent effort on integrating RF BPFs on a silicon substrate is accelerated with the emergence of CMOS passive and active inductors. A single-chip realization of RF transceivers with on-chip RF BPFs offers a number of critical advantages including a reduced assembly cost, increased system reliability, and improved performance. Table 1.1 tabulates some recently reported RF bandpass filters with CMOS spiral and active inductors.

**Table 1.1:** BPF with CMOS spiral and active inductors.

| Ref. | Year | Tech. (µm) | $f_0$ (GHz) | Filter order | Inductor type |

|------|------|------------|-------------|--------------|---------------|

| [6]  | 2002 | 0.18       | 1.75        | 3            | spiral        |

| [20] | 2002 | 0.25       | 2.14        | 3            | spiral        |

| [21] | 2010 | 0.09       | 3.46        | 2            | active        |

| [22] | 2012 | 0.18       | 0.6         | 3            | active        |

| [23] | 2011 | 0.13       | 0.6         | 1            | active        |

## 1.1.5 Gain Boosting

Traditional gain-boosting techniques such as cascodes and regulated cascodes lose their potency at high frequencies due to the increased gate-source and gate-drain couplings via the gate-source and gate-drain capacitors of MOSFETs. A technique that is widely used in boosting the voltage gain of narrowband low-noise amplifiers (LNAs) is to use a LC tank as the load of the LNAs [24, 25], utilizing the infinite impedance of ideal LC tanks at their self-resonant frequency. When a LC tank is used as the load of a common-source amplifier whose voltage gain is approximated by  $A_v \approx -g_m Z_L$ , where  $g_m$  is the transconductance of the MOSFET and  $Z_L$  is the load impedance, as

shown in Figure 1.4, the large impedance of the LC tank at its self-resonant frequency  $\omega_0 = \frac{1}{\sqrt{L_p C}}$  will significantly boost the gain of the amplifier at  $\omega_0$ . The resonant frequency of the tank is set to be the same as the frequency of the input of the LNA. Note that voltage gain of the amplifier at frequencies other than  $\omega_0$  is low.

**Figure 1.4:** Gain boosting of low noise amplifiers using LC tank load.

# 1.1.6 Power Divider

Usaully, transmission lines are employed to implement power dividers. But in order to reduce the size of the structure, lumped elements is used to construct power dividers at the cost of a high insertion loss and a limited bandwidth. Equivalent circuit of the lumped Wilkinson power divider is depicted in Figure 1.5. Replacing passive spiral inductors with CMOS AIs brings the advantages of the high quality factor, low silicon consumption, and high self-resonant frequency [26, 27].

Figure 1.5: Equivalent circuit of lumped Wilkinson power divider.

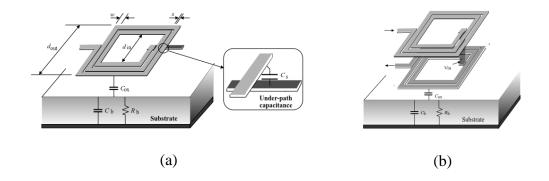

### 1.2 Spiral Inductors

Monolithic on-chip inductors are also known as spiral inductors due to the way in which these inductors are laid out. Both planar and stacked spiral inductors have been illustraded in Figure 1.6(a&b). Modern Computer Aided Design (CAD) tools for Integrated Circuit (IC) design are equipped with spiral inductors as standard elements in their component libraries.

Figure 1.6: Spiral Inductors (a) planar (b) stacked.

Spiral inductors offer the key advantages of superior linearity and a low level of noise. The performance and applications of spiral inductors are affected by a number of drawbacks that are intrinsic to the physical geometry of these passive devices and CMOS technologies in which spiral inductors are implemented. These drawbacks include:

- Low quality factor The Quality Factor (QF) of spiral inductors and transformers is limited by the ohmic loss of the spiral at high frequencies. Two sources that contribute to the ohmic loss of the spiral inductors and transformers exist: the skin-effect induced resistance of the spiral and the resistance induced by the eddy currents in the substrate.

- Low self-resonant frequency The self-resonance of a spiral inductor is the resonance of the LC tank formed by the series inductance of the spiral inductor and the shunt capacitance between the spiral of the inductor and the substrate, as well as its underpass capacitance. The low Self-Resonant Frequency (SRF) of spiral inductors is mainly due to the large spiral-substrate capacitance, arising from the large metal area occupied by the spiral.

- Large silicon area Due to the low inductance of spiral inductors, especially

planar spiral inductors, and the fact that the inductance of these inductors is

directly proportional to the number of the turns of the spiral of the inductors, the silicon area required for routing the spiral of the inductors is large.

### 1.3 Active Inductors

Als are mainly implemented by CMOS transistors which are main elements of electronic systems in recent years. Many architecture are used to improve the performance of AIs such as feedback, cascode stage and Feed Forward Path (FFP). Under certain DC biasing conditions and signal-swing constraints, these networks exhibit an inductive characteristic in a specific frequency range. The main advantages of AIs which push the designer to use them instead of their spiral counterparts, are as follow:

- Low silicon consumption Because only MOS transistors are usually required in the realization of CMOS AIs and the inductance of these active inductors is inversely proportional to the transconductances of the transistors, the silicon consumption of CMOS active inductors is negligible as compared with that of their spiral counterparts.

- Large and tunable SRF CMOS AIs have high SRF. For example, the passband center frequency of an active inductor RF bandpass filter is typically set to the SRF of the active inductor of the filter. The larger the SRF of the active inductor, the higher the passband center frequency of the filter. A large SRF of AIs ensures that the active inductors will have an inductive behavior over a large frequency range.

- Large and tunable inductance As to be seen in Chapter 2, the inductance of CMOS AIs is inversely proportional to the transconductances of the transistors synthesizing the inductors. The smaller the width of the transistors, the larger the inductance. Also the inductance can be tuned conveniently by varying the DC biasing condition of the transistors synthesizing the inductor with a large inductance tuning range. Additionally, fine tuning of the inductance can be achived by varying the load capacitance of the transconductors.

- Large and tunable QF The QF of CMOS AIs is set by the ohmic loss of the inductors, arising mainly from series resistance of AI. This resistance comes from the finite output resistance of the transconductors of the inductors. Thus QF

can be increased by increasing output resistance of the transcoductors. A number of methods are available to boost the output resistance, such as cascodes, regulated cascodes, and negative resistor compensation.

Highly compatibility with CMOS technology – Spiral inductors are existing in mixed mode technology. However, AIs are compatible with all CMOS process.

These kinds of inductors have found many applications such as oscillators, RF filters, RF phase shifters, LNAs, RF power dividers, communication systems and matching networks. Table 1.2 declares some recently published applications which were employed CMOS AIs.

**Table 1.2:** Recent publish applications of CMOS AIs.

| Ref. | Year | Tech.   | application      | Remark         |

|------|------|---------|------------------|----------------|

| [28] | 2012 | 0.09 µm | LC VCO           | 13 GHz         |

| [29] | 2015 | 0.18 µm | TAI VCO          | 0.6-7.2 GHz    |

| [30] | 2011 | 0.13 µm | VCO              | 0.833-3.72 GHz |

| [32] | 2015 | 0.18 µm | Matching network | 0-6.9 GHz      |

| [31] | 2009 | 0.18 µm | LNA              | 0.375-2.18 GHz |

| [34] | 2013 | 0.18 µm | LNA              | 0.8-2.5 GHz    |

| [33] | 2015 | 0.18 µm | LNA              | 3.1-10.6 GHz   |

| [35] | 2013 | 0.09 µm | Bandpass Filter  | 0.8-6 GHz      |

| [36] | 2011 | 0.18 µm | Power divider    | 5.8-10.4 GHz   |

These AIs in mentioned applications are influenced by some difficulties such as: limited dynamic range, high level of noise, high sensitive to process variations and supply sources fluctuation. These difficulties arise from the intrinsic characteristics of CMOS devices. Fortunately, the effect of many of these difficulties can be reduced through innovative designs and proper circuit configurations. For example, the limited

dynamic range of active inductors can be expanded using class AB configurations [36]. The process variation can be compensated by tuning the inductance and QF [38] and the effect of noise can be decreased by noise cancellation configuration [37]. The developing utilizations of CMOS AIs keep on improving alongside the origin of new design strategies and circuit topologies.

#### 1.4 Conclusion

Due to explanations, it is obvios that inductive charactristics are very crutial in many applications especially in RF. It is shown that integrated spiral inductors suffer from a low quality factor, a low SRF, a low and fixed inductance, and the need for a large silicon area. Meanwhile, CMOS AIs offer a number of attractive characteristics as compared with their spiral counterparts. These characteristics include a low silicon consumption, a large and tunable SRF, a large and tunable inductance, a large and tunable QF and etc. Also, AIs are employed to implement many electronic circuits' blocks such as LNAs, Power Amplifiers (PAs), filters, power dividers, Voltage Control Oscillators (VCOs) and matching networks.

The utilizations of AIs are influenced by a few difficulties emerging from the intrinsic properties of CMOS devices including limited dynamic range, high level of noise, high sensitivity to process variations and supply voltage fluctuations. By using some advanced circuit design techniques and developing the process technology, many of these difficulties can be overcome.

### 1.5 Dissertation Organization

In chapter 2, the principles, topologies, characterizations and implementation of the gyrator-C is discussed in-depth. The GC networks which are implemented by Operational transconductance amplifier are suitable for RF application. This property arises from their minimum usage of active elements. It is shown that both grounded and floating active inductor can be implemented by gyrator-C networks. To provide a quantitative measure of the performance of active inductors, a number of figure-of-merits have been introduced. These figure-of-merits include frequency range, inductance tunability, quality factor, noise and power consumption. One of the key advantages of active inductors over their spiral counterparts is the large tunability of

their inductance. The inductance of gyrator-C active inductors can be tuned by varying either the transconductances of the transconductors or the load capacitance which is implemented by MOS varactor

In chapter 3, new grounded and floating AIs are designed by using advanced circuit techniques. For lowering conductance in input and output nodes of AI, Multi-Regulated Cascode (MRC) stages are employed to Q enhancement purpose. Theoretical analysis and post-layout simulation results shows the effectiveness of using MRC stages usage in properties of AI. Also, these stages are utilized to design high Q floating AI.

Designers do their best to improve SRF and QF, two main characteristics in term of AI performance. An AI with ability to adjust its SRF and QF without affecting each other is designed and simulated. The cascoding and RC feedback structures are used in the new design of AI. As it discussed before, input transistor is very important regarding to AI characterizations. Cascoding input transistor gives the ability to adjust the first gyrator's transconductance and input parasitic capacitance independently. Furthermore, the inductance value can be adjusted by other transistor's transconductance. The RC feedback is utilized to cancel the parasitic series-resistance of AI which results in QF enhancement. Since, bias condition of cascoding transistors is provided by a diode-connected transistor, the proposed structure is robust in terms of performance over variation in process, voltage and temperature.

The Noise of designed AIs has limited the use of them in RF applications such as LNAs. The main noise source of an AI is its input transistor. In order to have low noise AI, the input transistor should be designed large enough. But it leads to low SRF which limited the inductive frequency band. A low-noise and low-loss AI is presented suitable for RF low noise applications. Utilizing all transistors in CS configuration on the AI circuit leads to low conductance nodes which it causes to high Q AI. P-type MOS transistors and Feed-Forward Path (FFP) are employed to decrease noise of the AI, respectively.

In chapter 4, GC network in 3 applications are presented. The capacitive based micro sensors convert mechanical signals to small capacitance variation. The capacitance variation in micro sensor is in the range of femto-Farads which makes it difficult to sense. On the other hand, the Gyrator-C topologies can convert a low capacitance

variation to high impedance change which makes it a good choice for being interface circuits for capacitive sensors. Then a new 3-axis accelerometer with ability to cancel cross section sensitivity is designed. The sensor's electrodes are located in such a way that enables the structure to detect acceleration in all axis independently. Consequently, a new GC configuration for sensing very small capacitance changes in a capacitive sensor is presented. In the proposed configuration, the operating frequency range and Scaling Factor can be adjusted without affecting each other by tuning the bias currents. In addition, the proposed configuration employs RC feedback and cascoding techniques to cancel the effect of the parasitic components.

Finally, in order to show versatility of designed AIs, they are used in designed third and sixth order broadband microwave filters. The first one is a third order Chebyshev low pass filter. The second one which is designed by using simplified real frequency technique is a sixth order Chebyshev band pass filter. The simulated frequency response of filters prove the workability of the designed AIs.

Finally, dissertation is concluded in chapter 5 and some scopes for future works are given.

#### 2. CMOS ACTIVE INDUCTORES

This chapter provides a background overview of the principles, topologies, characteristics, and implementation of CMOS active inductors. First, the principles of gyrator-C based synthesis of inductors are explained. Both grounded and floating configuration of Gyrator-C (GC) AIs are investigated. Section 2.2 diclares salient features of AI such as frequency range, inductance tunability, Quality Factor (QF), noise, stability and etc, which quantify the performance. Sections 2.3 and 2.4 detail the CMOS implementation of grounded and floating AIs, respectively. The chapter is summarized in Section 2.5.

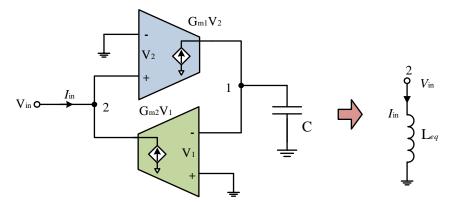

# 2.1 Principles of Gyrator-C Active Inductors

# 2.1.1 Ideal (lossless) Grounded Gyrator-C Active Inductors

A gyrator consists of two back-to-back connected transconductors. When one port of the gyrator is connected to a capacitor, as shown in Figure 2.1, the network is called the GC network.

**Figure 2.1:** Ideal grounded GC AI.

According to the ideal GC network shown in Figure 2.1, the input admittance is calculated as:

$$Y = \frac{I_{in}}{V_{in}} = \frac{1}{s(\frac{C}{G_{m1}G_{m2}})}$$

(2.1)

Equation (2.1) indicates that port 2 of the GC network behaves as a grounded ideal inductor, which its inductance value is given by:

$$L = \frac{C}{G_{m1}G_{m2}} \tag{2.2}$$

Thus, GC can be used to synthesize inductors. The inductance of GC AI is directly proportional to the load capacitance C and inversely proportional to the product of the transconductances of the transconductors of the gyrator.

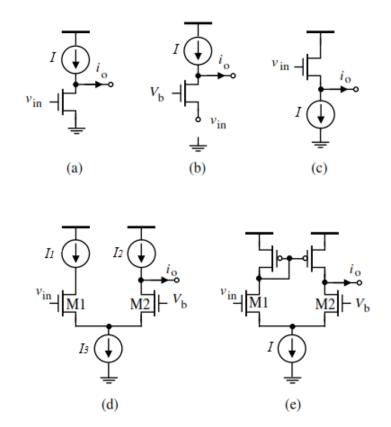

Although the transconductors of GC networks can be configured in various ways, the constraint that the synthesized inductors should have a large frequency range, a low level of power consumption, and a small silicon area requires that these transconductors be configured as simple as possible. Figure 2.2 shows the simplified schematics of the basic transconductors that are widely used in the configuration of GC AIs. Common-Gate (CG), Common-Drain (CD), and differential-pair transconductors all have a positive transconductance while the Common-Source (CS) transconductor has a negative transconductance [89].

Figure 2.2: Simplified schematic of basic transconductors. (a) CS ( $i_o = -g_m v_o$ ), (b) CG ( $i_o = g_m v_o$ ), (c) CD ( $i_o = g_m v_o$ ), (d, e) differential-pair ( $i_o = g_m v_o$ ).

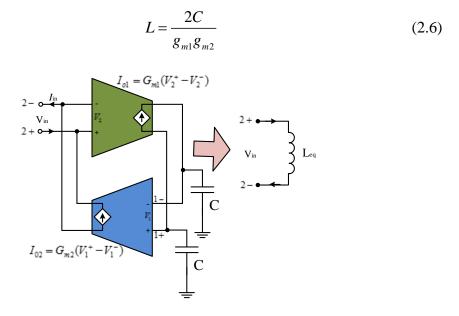

## 2.1.2 Ideal Floating Gyrator-C Active Inductors

A Floating Active Inductor (FAI) has floating terminals, which are not connected to ground. Floating GC AIs can be designed by replacing single-ended transconductors with differentially-configured transconductors, as depicted in Figure 2.3 [89]. Because

$$V_{in1}^{+} = -\frac{g_{m1}}{sC}(V_{in2}^{+} - V_{in2}^{-}), \ V_{in1}^{-} = \frac{g_{m1}}{sC}(V_{in2}^{+} - V_{in2}^{-})$$

(2.3)

$$I_{o2} = g_{m2}(V_{in1}^{+} - V_{in1}^{-}) \implies I_{o2} = -\frac{2g_{m1}g_{m2}}{sC}(V_{in2}^{+} - V_{in2}^{-})$$

(2.4)

Thus, the input admittance is given by

$$Y = \frac{I_{in}}{V_{in2}^{+} - V_{in2}^{-}} = \frac{1}{s(\frac{2C}{g_{m1}g_{m2}})}$$

(2.5)

Equation (2.5) reveals that the GC network in Figure 2.3 behave as a floating inductor with the value of:

Figure 2.3: Ideal (lossless) Floating GC AI.

The Floating Active Inductors (FAIs) have some attractive advantages in constract with their Grounded Active Inductors (GAIs) counterparts like:

- ➤ Their diffirentional configuration leads to reject of common-mode disturbances of AI which make is suitable for mixed signal applications.

- ➤ The voltage swing of FAIs is twice than their GAIs counterpart.

## 2.1.3 Lossy Grounded Gyrator-C Active Inductors

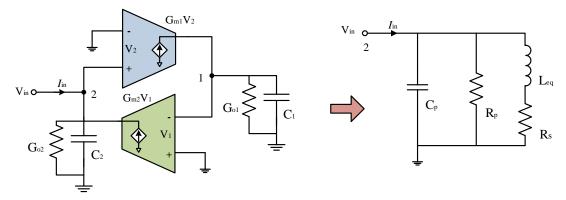

In practical, the AIs do not have inductive behavior in all frequency spectrum due to their parasitic components in input/output nodes. Consider the lossy GC GAI shown in Figure 2.4, where  $G_{oi}$  and  $C_i$  are parasitic conductance and capacitance in ith node, respectively.

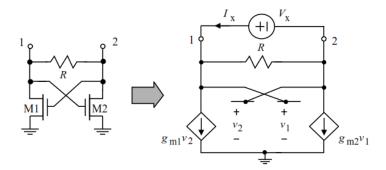

**Figure 2.4**: Block diagram of GAI realization and its equivalent passive model.

The transconductances of transconductors are assumed constaint to have simplify analysis. The admittance looking into port 2 of GC topology is calculated as:

$$Y_{in} = \frac{1}{Z_{in}} = \frac{I_{in}}{V_{in}} = sC_2 + G_{o2} + \frac{1}{s(\frac{C_1}{G_{m1}G_{m2}}) + \frac{G_{o1}}{G_{m1}G_{m2}}}$$

(2.7)

Equation (2.7) indicates that the GAI can be modeled by a RLC network (Figure 2.4) which its elements value are obtained as:

$$R_{p} = \frac{1}{G_{02}}, \qquad R_{s} = \frac{G_{o1}}{G_{m1}G_{m2}},$$

$$C_{p} = C_{2}, \qquad L_{eq} = \frac{C_{1}}{G_{m1}G_{m2}}$$

(2.8)

As it can be seen from the equivalent model values, in order to have low ohmic loss  $R_p$  should be maximized and  $R_s$  should be minimized. The finite input and output impedances of the transconductors of the GC network, however, have no effect on the inductance of the AI. The finite input and output impedances of the transconductors constituting active inductors result in a finite quality factor. For applications such as band-pass filters, active inductors with a large quality factor are mandatory. In these cases, Q-enhancement techniques that can offset the detrimental effect of  $R_p$  and  $R_s$

should be used to boost the QF. The resonance frequency of the RLC network of the AI is given by:

$$\omega_0 = \sqrt{\frac{1}{C_p L_{eq}}} = \sqrt{\frac{G_{m1} G_{m2}}{C_2 C_1}}$$

(2.9)

$\omega_0$  is the Self-Resonance Frequency (SRF) of the AI. The SRF defines the upper limit of the frequency band range, which AI operates. In other words, the SRF of an AI is set by cut-off frequency of the transconductances which constructing it.

# 2.1.4 Lossy Floating Gyrator-C Active Inductors

Floting type of GC AI can be analyzed in similer way of GAIs in 2.1.3 section. Figure 2.5 depicts the lossy floating GC network and its passive equivalent model. Calculating the input admittance in port 2 gives:

$$Y_{in} = \frac{1}{Z_{in}} = \frac{I_{in}}{V_{in}} = s\frac{C_2}{2} + \frac{G_{o2}}{2} + \frac{1}{s(\frac{C_1}{2G_{m1}G_{m2}}) + \frac{G_{o1}}{2G_{m1}G_{m2}}}$$

(2.10)

Investigation of equation (2.10) shows that it equivalent with RLC network which its parameters given by:

$$R_{p} = \frac{2}{G_{02}}, \qquad R_{s} = \frac{G_{o1}}{2G_{m1}G_{m2}},$$

$$C_{p} = \frac{C_{2}}{2}, \qquad L_{eq} = \frac{C_{1}}{2G_{m1}G_{m2}}$$

(2.11)

**Figure 2.5**: Block diagram of FAI realization and its equivalent passive model.

The constant in (2.11) is due to the floating configuration of the AI.

# 2.2 Active Inductor Properties

The most important properties of AIs which quantify its performance is discussed in this section. They are such as frequency range, inductive tunability, QF, noise, stability and etc.

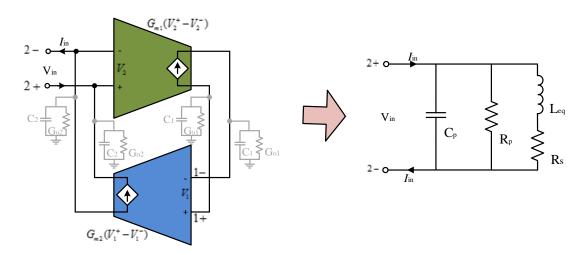

# 2.2.1 Frequency Range

It was shown in the preceding section that a lossy GC AI only exhibits an inductive characteristic over a specific frequency range. This frequency range can be obtained by examining the impedance of the RLC equivalent circuit of the lossy active inductor which its input impedance can be calculated as:

$$Z_{in} = \left(\frac{R_s}{C_p L_{eq}}\right) \frac{s \frac{L_{eq}}{R_s} + 1}{s^2 + s\left(\frac{1}{R_p C_p} + \frac{R_s}{L_{eq}}\right) + \frac{R_p + R_s}{R_p C_p L_{eq}}}$$

(2.12)

When complex conjugate poles are encountered, the pole resonant frequency of  $Z_{in}$  is given by:

$$\omega_p = \sqrt{\frac{R_p + R_s}{R_p C_p L_{eq}}} \tag{2.13}$$

Because  $R_p \gg R_s$ , Eq. (2.13) is simplified to:

$$\omega_p \approx \sqrt{\frac{1}{C_p L_{eq}}} = \omega_0 = SRF$$

(2.14)

where,  $\omega_0$  is the self-resonant frequency of the active inductor. Also observe that  $Z_{in}$  has a zero at the frequency

$$\omega_z = \frac{R_s}{L_{eq}} = \frac{G_{o1}}{C_1}$$

(2.15)

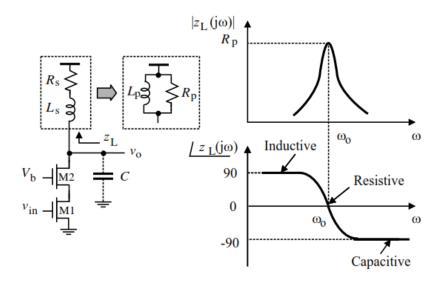

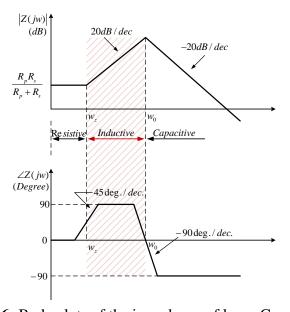

The Bode plots of  $Z_{in}$  are sketched in Figure 2.6. It is evident that the gyrator-C network is resistive, when  $\omega \leq \omega_z$ , inductive when  $\omega_z \leq \omega \leq \omega_0$ , and capacitive when  $w \geq w_0$ . The frequency range in which the GC network is inductive is lower-bounded by  $\omega_z$  and upper-bounded by  $\omega_0$ . Also it is observed that  $R_p$  has no effect on the frequency range of the active inductor.  $R_s$ , however, affects the lower bound of the frequency range over which the GC network is inductive. The upper bound of the frequency range is set by the SRF of the AI, which is set by the cut-off frequency of the transconductors constituting the active inductor. For a given inductance  $L_{eq}$ , in order to maximize the frequency range, both  $R_s$  and  $C_p$  should be minimized.

**Figure 2.6:** Bode plots of the impedance of lossy Gyrator-C AI.

### 2.2.2 Inductance Tunability

Inductance tunability is required in many applications such as phase-locked loops, Voltage Controlled Oscillators (VCOs) and filters. The salient feature of GC AIs is that their inductance value can be tuned not only by changing the load capacitance but also by varying the transconductances of the transconductors.

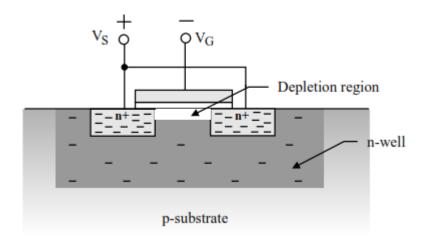

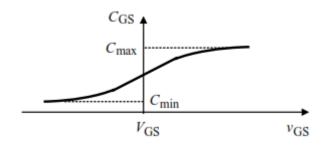

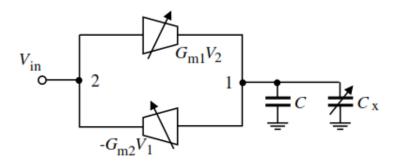

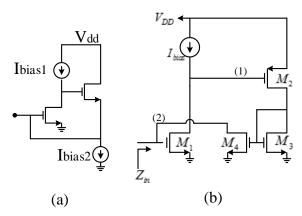

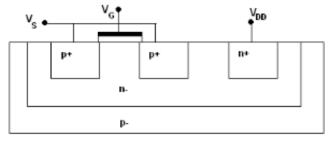

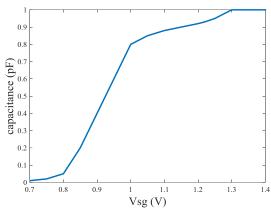

Varactors are employed as tunable capacitors in CMOS technology. Two types of varactors exists, namely pn-junction varactors and MOS varactors. The MOS type is usually used in circuits which are implemented by transistors. Figure 2.7 exhibits the sideview of accumulation-mode MOS varactors. A key advantage of accumulation-mode MOS varactors is the large voltage swing across the terminals of the varactors.

They are the most widely used varactors in voltage/current-controlled oscillators. Figure 2.8 shows the capacitance variation in MOS varactors [89].

Figure 2.7: Sideview of MOS varactors.

**Figure 2.8:** Capacitance variation in MOS varactors.

Bias variation is used to transcoductance tuning of transconductores in GC topology of AIs. This approach offers a large conductance tuning range, subsequently a large inductance tuning range. The conductance tuning range is set by the constraint that the transconducting transistors of the transconductors must remain in the saturation. Consequently, conductance varying is used for large inductance variation while load capacitance changing is used for small inductance variation (Figure 2.9). The conductance tuning range is set by the pinch-off condition while the capacitance tuning range is set by the range of the control voltage of the varactors.

Figure 2.9: Inductance tuning via transconductances or load capacitance variation.

It is obvious that the transconductance variation will affect the parasitic series resistance of AI. This is echoed with a change in the quality factor of the active inductors. The variation of the quality factor due to the tuning of L must therefore be compensated for such that L and Q are tuned independently. The load capacitance changing does not affect the QF of AI.

# 2.2.3 Quality Factor

High QF is the most salient feature of AIs in contrast with their Passive Spiral Inductors (PSIs). It is independent from voltage/current of PSIs but it is not valid for AIs. The QF of an inductor quantifies the ratio of the net magnetic energy stored in the inductor to its ohmic loss in one oscillation cycle. Equation (2.16) convenient way to quantify the Q of linear inductors including AIs.

$$Q = \frac{\text{Im}[Z]}{\text{Re}[Z]} \tag{2.16}$$

Active inductors are linear when the swing of the voltages/currents of the inductors are small and all transistors of the active inductors are properly biased. The quality factor of a lossy gyrator-C active inductor can be derived directly from (2.12) and (2.16).

$$Q = \left(\frac{\omega L_{eq}}{R_s}\right) \frac{R_p}{R_p + R_s \left[1 + \left(\frac{\omega L_{eq}}{R_s}\right)^2\right]} \left[1 - \frac{R_s^2 C_p}{L_{eq}} - \omega^2 C_p L_{eq}\right]$$

(2.17)

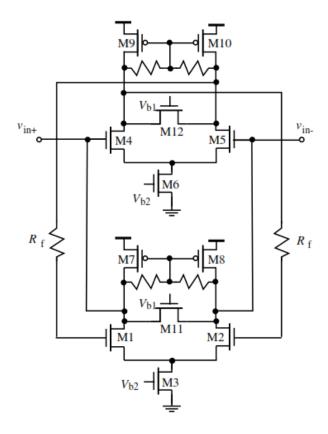

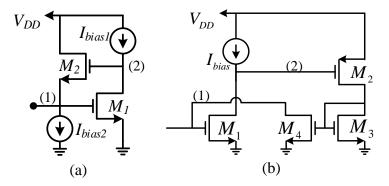

It is clear from (2.17) QF is mostly dependent on  $R_s$  and  $R_p$ . Furthermore, it is seen that the first term of (2.17)  $\left(\frac{\omega L_{eq}}{R_s}\right)$  is dominant part of QF in AI. So, it is used to quantify